Fターム[5F033TT08]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 側壁絶縁膜 (2,038) | 電極、配線の側壁 (1,106)

Fターム[5F033TT08]に分類される特許

261 - 280 / 1,106

半導体装置の製造方法および半導体装置

【課題】ゲート−ドレイン間寄生容量を低減できる半導体装置の面積を低減し、工程数を削減する。

【解決手段】トランジスタ領域では、ソース配線層とゲート電極がトレンチ内に埋め込まれている。ソース引き出し領域は、トランジスタ領域の隣またはトランジスタ領域内に設けられ、ソース配線層がトレンチの上端よりも上に突出するように形成される。このソース配線層は、トレンチの直上で、トランジスタ領域に形成されたソース電極と接続される。ゲート引き出し領域は、ソース引き出し領域の外側に設けられ、ゲート電極とゲート配線層とが接続される。ゲート電極は、ポリシリコン膜を成膜した後、レジストパターンを形成することなくエッチバックすることにより形成される。このとき、ソース配線層のトレンチの上端よりも上に突出した部分の側壁には、ポリシリコン膜がサイドウォール状に残る。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート電極部と容量コンタクトプラグとのショートを防止する。

【解決手段】複数のゲート電極部10と該ゲート電極部10間を接続する配線部との上に、耐エッチング膜17を備えたゲートハードマスク20を形成後、前記配線部上の前記耐エッチング膜17を除去する。これにより、CMP処理を経てコンタクトプラグ22を形成し、さらに、エッチングにより容量コンタクトホール24を開口して容量コンタクトプラグ25を形成した場合に、ゲート電極部10と容量コンタクトプラグ25とのショートを防止することができる。

(もっと読む)

寄生容量が低減されたSOIボディ・コンタクト型FETのための方法

【課題】

ボディ・コンタクトを半導体オン・インシュレータ・デバイスに設け、それにより、デバイスに寄生容量の低減をもたらすこと。

【解決手段】

1つの実施形態において、本発明は、絶縁層の上を覆うように配置された半導体層を含む基板であって、半導体層は、半導体ボディと、半導体ボディの外周の周りに存在する分離領域とを含む基板と、基板の半導体層の上を覆うゲート構造体であって、半導体ボディの上面の第1の部分上に存在するゲート構造体と、非シリサイド半導体領域によって半導体ボディの第1の部分から分離される半導体ボディの第2の部分と直接物理的に接触しているシリサイド・ボディ・コンタクトとを含む、半導体デバイスの製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】 極短時間アニール処理を行う際に、基板自体の損傷を抑制する半導体装置の製造方法を提供する。

【解決手段】 半導体基板上にゲート電極を形成する工程と、前記半導体基板に導電性の不純物を導入する工程と、前記半導体基板及び前記ゲート電極上に保護膜を形成する工程と、前記保護膜を形成後に前記半導体基板の裏面全面を研磨する工程と、前記半導体基板の裏面全面を研磨した後に前記半導体基板の表面が1000℃以上での保持時間が0.1秒以下となるような加熱処理により前記不純物を活性化する工程とを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造工程での乾燥処理におけるパターンの倒壊を抑制可能とする、半導体装置の製造方法を提供すること。

【解決手段】シリコン系材料を用いて構成されるシリコン系部材層を形成し、前記シリコン系部材層の上に、金属材料を用いて構成される金属部材層を形成し、前記金属部材層をパターニングし、パターニングされた前記金属部材層の表面に側壁膜を形成し、前記シリコン系部材層をパターニングすることにより、前記シリコン系部材層と、前記側壁膜で表面を覆われた前記金属部材層と、を備える構造体を形成し、薬液を用いて前記構造体の表面を洗浄し、前記構造体の表面から前記薬液を除去し、前記構造体の表面に撥水性保護膜を形成し、前記撥水性保護膜が形成された前記構造体の表面をリンスし、前記構造体の表面を乾燥させる、工程を含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、信頼性の高い半導体装置の製造方法および半導体装置を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板上に設けられた第1絶縁体層を貫く第1開口に第1プラグ電極を形成する工程と、第1プラグ電極と接触する第1配線層を形成する工程と、第1絶縁体層上および第1配線層上にエッチングストップ層および第2絶縁体層をこの順で形成する工程と、第1配線層上のエッチングストップ層および第2絶縁体層をドライエッチングを用いて除去することにより第1配線層を露出させ、第1配線層の側面上および第1絶縁体層の一部の上に設けられたエッチングストップ層ならびに第2絶縁体層を含むサイドウォールを形成する工程と、第3絶縁体層を形成する工程と、第3絶縁体層を貫く第2開口を形成する工程と、第2開口に第1配線層と接触する第2プラグ電極を形成する工程とを備えることを特徴とする。

(もっと読む)

成膜方法および半導体装置の製造方法

【課題】誘電率が低くかつエッチング耐性に優れた窒化シリコン系絶縁膜を形成する。

【解決手段】基材上にシラン系ガス(DCS)、窒化性ガス(NH3)及びホウ素含有ガス(BCl3)を、N2パージを逐次行いながらこの順で供給してホウ素含有窒化シリコン層を形成する工程と、このホウ素含有窒化シリコン層に、プラズマにより活性化された窒化性ガス(活性化NH3)を供給する工程とを含み、これらの工程をこの順で繰り返し行う成膜方法。

(もっと読む)

半導体装置およびその製造方法

【課題】製造工程の増加を抑えて、通常のコンタクトとシェアードコンタクトとをそれぞれ良好なコンタクト特性を有するようにする。

【解決手段】半導体装置100は、第1の不純物拡散領域106aに接続するとともに、第1のゲート電極112aとは接続しないように形成された第1のコンタクト124と、第2のゲート電極112bおよび第2の不純物拡散領域106bに共通して接続するように形成された第2のコンタクト126とを含む。第1のコンタクト124および第2のコンタクト126は、それぞれ、層間絶縁膜122の表面から基板101に向かう途中の位置でテーパー角度が小さくなるように変化する形状を有し、第2のコンタクト126においてテーパー角度が変化する位置が、第1のコンタクト124においてテーパー角度が変化する位置よりも基板101に近い。

(もっと読む)

半導体装置の製造方法

【課題】本発明は多層配線構造を有する半導体装置の製造方法に関し、高い集積度が要求される場合に優れた歩留まりと高い信頼性とを確保することを目的とする。

【解決手段】トランジスタのソースドレイン領域の上層にシリコン酸化膜7を形成する。一端面がソースドレイン領域6に導通し、他端面がシリコン酸化膜7の表面に露出するように、シリコン酸化膜7の内部に導電性のパッド10を設ける。シリコン酸化膜7およびパッド10の上層にシリコン酸化膜11を形成する。一端面がパッド10に接触し、他端面が配線層14と導通するようにシリコン酸化膜11の内部にプラグとして機能する導電層を設ける。シリコン酸化膜7の表面と、パッド10の他端面は平滑な同一平面を形成する。プラグとして機能する導電層は、パッド10に比して小さく、かつ、パッド10の中央部近傍に接触するように形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】耐湿リングの一部のパターンが剥離するのを防止しうる半導体装置及びその製造方法を提供することにある。

【解決手段】第1の耐湿リング8aと第2の耐湿リング8bとを有し、第1の耐湿リングは、第1の絶縁層142に埋め込まれた第1のパターン150aと、第2の絶縁層156に埋め込まれた第1のパターンより幅の狭い第2のパターン160aと、第2の絶縁層上に形成され、長手方向に沿った両側部のうちの少なくとも一方が第1のパターンと平面的に重なり合っていない第3のパターン160cとを有しており、第2の耐湿リング8bは、第1の絶縁層に埋め込まれた第4のパターン150bと、第2の絶縁層に埋め込まれた第4のパターンより幅の狭い第5のパターン160bと、第2の絶縁層上に形成され、長手方向に沿った両側部のうちの少なくとも一方が第4のパターンと平面的に重なり合っておらず、第3のパターンと分離された第6のパターン162bとを有している。

(もっと読む)

半導体装置の製造方法

【課題】プラズマ雰囲気の周囲に存在する銅による影響を抑制する半導体装置の製造方法を提供する。

【解決手段】半導体基板1の上方に絶縁膜18〜21を形成する工程と、絶縁膜18〜21上にレジスト膜24を形成する工程と、レジスト膜24の上方にマスク膜25を形成する工程と、マスク膜25の上方にレジストパターン27を形成する工程と、レジストパターン27をマスクにしてマスク膜25をエッチングする工程と、酸素ガスとハイドロフロロカーボンガスの混合ガスを導入し、30mTorr以上の圧力の雰囲気内で、マスク膜25から露出する領域のレジスト膜24をエッチングする工程とを有する。

(もっと読む)

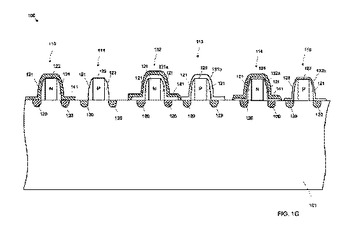

ストレス低減層を有する集積回路装置

集積回路装置が開示され、集積回路装置はNMOSゲート薄膜スタック(122)を覆う張力ストレス層(141)を有するデュアルストレスライナーNMOSデバイス(110)と、PMOSゲート薄膜スタック(123)を覆う圧縮ストレス層(142)を有するデュアルストレスライナーPMOSデバイス(111)と、張力ストレス層(141)とNMOSゲート薄膜スタック(124)との間に延在するストレス低減層(131a)を有する低減ストレスのデュアルストレスライナーNMOSデバイス(112)と、圧縮ストレス層(142)とPMOSゲート薄膜スタック(125)との間に延在するストレス低減層(131b)を有する低減ストレスのデュアルストレスライナーPMOSデバイス(113)とを含む。発明の実施形態において、追加の低減ストレスのデュアルストレスライナーNMOSデバイス(114)と低減ストレスのPMOSデバイス(115)とは、ストレス低減層(132a,132b)の厚みおよび/または材料特性を変更することによって形成される。  (もっと読む)

(もっと読む)

電界効果トランジスタ

【課題】従来の光学素子に電界効果トランジスタを適用するとき、PN接合部の光リークを抑えるために、トランジスタの周囲に遮光領域を設定する必要が有り、回路面積が大きくなるという課題があった。また、反射光に対して遮光性が十分でないという問題があった。

【解決手段】本発明の電界効果トランジスタは、ゲート電極上に、PN接合部に平面的に重なるように遮光部材を有する。この遮光部材により、PN接合部を遮光することができる。また、電界効果トランジスタ面積が増大しないため、回路の面積を小さく設定できる。

(もっと読む)

半導体装置及びその製造方法

【課題】加工マージンの大きい半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置は、主面を有する半導体基板と、半導体基板上に形成された第1絶縁膜と、第1絶縁膜に形成された複数のコンタクト孔と、複数のコンタクト孔内にそれぞれ形成された複数の第1コンタクトプラグと、第1絶縁膜上に形成され、該第1絶縁膜の複数の第1コンタクトプラグが形成された領域を含む所定領域を露出させる開口部を有する第2絶縁膜と、第1絶縁膜のうち開口部で露出した部分に形成され、半導体基板の主面に対して垂直方向に見て、開口部が形成されていない第1絶縁膜の上面の位置よりも低い上面の位置を有する凹部と、開口部を横切り、かつ複数の第1コンタクトプラグのそれぞれの上面に接続されるように、第1絶縁膜の凹部から第2絶縁膜の開口部を経て第2絶縁膜の上面にかけて形成された第2導電膜から成る複数の配線と、を有している。

(もっと読む)

半導体装置の製造方法

【課題】洗浄処理での腐食を抑えた高性能で高品質の半導体装置を提供する。

【解決手段】例えば、LCOSデバイスにおける画素電極90を形成する際、画素電極90の材料となる層に、間口の開口幅A1に対して底部の開口幅A2が狭い溝91を形成して、個々の画素電極90を形成した後、洗浄処理を行う。溝91の間口を広くすることで、洗浄処理時の液の滞留が抑えられ、画素電極90の腐食が抑えられるようになる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】強誘電体キャパシタの下部電極とバリアメタル膜との間の酸化膜の形成を防止する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、トランジスタTのソース/ドレイン拡散層11に接続するように形成された第1、第2のビアコンタクト23、24と、バリアメタル膜31を介して第1、第2のビアコンタクト23、24に接続された強誘電体キャパシタCとを備える。強誘電体キャパシタCは、バリアメタル膜31上に設けられた下部電極32と、強誘電体膜33と、上部電極34とを備える。下部電極32は、錐台形状の上部322と、この上部322に比べ水平方向に突出した鍔部を有する底部321とからなり、下部電極32の底部321は、バリアメタル膜31の上面を全て覆い、バリアメタル膜31の端面、鍔部の端面、及び強誘電体膜33の端面が水平方向において整合している。

(もっと読む)

半導体装置の製造方法

【課題】欠陥の発生を防止し且つ電気的特性に優れた強誘電体キャパシタを用いた半導体装置の製造方法を提供する。

【解決手段】第1の導電層40を形成し、第1の導電層40の表面に酸化膜10を形成し、酸化膜10を大気にさらし、酸化膜10を、減圧下且つ第1の温度で減圧加熱処理し、減圧加熱処理された酸化膜10を大気にさらすことなく、減圧下且つ第1の温度よりも低い第2の温度で、非晶質の第1の誘電体層41を酸化膜10上に形成し、第1の温度よりも高い第3の温度で、非晶質の第1の誘電体層41を結晶化する。

(もっと読む)

半導体装置の製造方法

【課題】素子分離部に対するウエルコンタクトホールの位置合わせ精度を向上する。

【解決手段】半導体基板にウエル領域2を形成する第1の工程と、前記半導体基板に、第1のアライメントマークと、前記ウエル領域2にアクティブ領域を分離する素子分離部7とを形成する第2の工程と、前記半導体基板の上に、第2のアライメントマークと、MOSトランジスタのゲート電極9とを形成する第3の工程と、前記ゲート電極9とともにソース電極又はドレイン電極となるべき半導体領域を形成する第4の工程と、前記半導体基板及び前記ゲート電極9の上に絶縁膜14を形成する第5の工程と、前記第1のアライメントマークを基準として決められた位置に、ウエルコンタクトホールを形成する第6の工程と、前記第2のアライメントマークを基準として決められた位置に、前記絶縁膜14を貫通するコンタクトホールを形成する第7の工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

261 - 280 / 1,106

[ Back to top ]