Fターム[5F033TT08]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 側壁絶縁膜 (2,038) | 電極、配線の側壁 (1,106)

Fターム[5F033TT08]に分類される特許

241 - 260 / 1,106

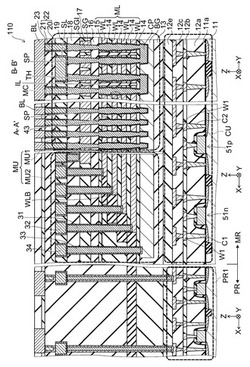

不揮発性半導体記憶装置及びその製造方法

【課題】回路部の上部にメモリ部を形成し、回路部が高温にさらされても回路部の配線層やコンタクトが劣化しない不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板11と、メモリ部MUと、半導体基板とメモリ部との間の回路部CUと、を備える。メモリ部は、半導体基板の主面11aに垂直な第1方向に交互に積層された複数の電極膜WLと複数の絶縁膜14とを有する積層構造体MLと、積層構造体を第1方向に貫通する半導体ピラーSPと、電極膜と半導体ピラーとの交差部に対応して設けられた記憶部43と、を有す。回路部は、それぞれ第1、第2導電型のソース/ドレイン領域を有する第1、第2トランジスタ51n、51pと、シリサイドを含む第1配線W1と、ソース/ドレイン領域と同じ導電型のポリシリコンからなるコンタクトプラグC1、C2と、を有す。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性の高い半導体装置およびその製造方法を提供すること。

【解決手段】半導体基板と、半導体基板の第1面側に形成された半導体素子と、半導体基板の第1面側に形成されて半導体素子と電気的に接続された配線を有する配線層と、半導体基板の第1面側に形成された電極パッド部と、半導体基板の第1面からその反対側の第2面まで貫通する貫通孔内に形成された貫通電極とを備え、前記電極パッド部は、半導体基板の第1面に部分的に積層された単一導電層と、単一導電層に積層された混成導電層とを有し、前記単一導電層は、貫通電極と電気的に接続する導電領域部からなり、前記混成導電層は、単一導電層と前記配線とを電気的に接続する導電領域部と、単一導電層と配線とを電気的に絶縁する絶縁領域部とが混成されてなる半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】新規な半導体装置の製造方法を提供する。

【解決手段】SiN層にPおよびOを注入する工程と、前記SiN層に注入されたPおよびOをH2Oと反応させ、前記SiN層をエッチングする工程とを有する方法により、半導体装置を製造する。特に、半導体装置を形成するにあたり、狭スペースで高アスペクト比の溝サイドウォールを形成する工程や、埋め込み型ビット線を形成する工程に、上記のようにSiN層をエッチングすることができる。

(もっと読む)

多層配線基板及びそれを備えた半導体装置

【課題】遮光領域を抑制することにより、開口率の低下を防止するとともに、製造工程を簡素化することができる多層配線基板及びそれを備えた半導体装置を提供することを目的とする。

【解決手段】TFT基板1は、第1コンタクトホール11が形成された第1絶縁膜8と、第1絶縁膜8の表面及び第1コンタクトホール11の表面に形成された第1配線層14と、第2コンタクトホール15が形成された第2絶縁膜9と、第2絶縁膜9上に積層されるとともに、第2絶縁膜9の表面及び第2コンタクトホール15の表面に形成され、第1配線層14と導通された第2配線層16とを備えている。そして、第1及び第2コンタクトホール11,15が、TFT基板1の上下方向Xにおいて重なった状態で直線的に配置され、第1コンタクトホール11において、第1配線層14上に絶縁性樹脂25が充填されている。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの微細化が進展しても、広いキャパシタ面積を確保し、容量を増大させることが可能なキャパシタを備える、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板111と、基板上に、第1の電極材で形成された複数の第1の電極層と、第1の電極材と異なる第2の電極材で形成された複数の第2の電極層とが、キャパシタ絶縁膜を介して交互に積層されたキャパシタ102と、第1及び第2の電極層の側方に形成されており、第1の電極層と電気的に接続され、第2の電極層と電気的に絶縁されている、1つ以上の第1のコンタクトプラグ171Aと、第1及び第2の電極層の側方に形成されており、第2の電極層と電気的に接続され、第1の電極層と電気的に絶縁されている、1つ以上の第2のコンタクトプラグ171Bとを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク電流の増加と絶縁耐圧の劣化を抑制し、かつ配線容量の増加を抑制する、信頼性の高い半導体装置を提供する。

【解決手段】半導体基板1上の層間絶縁膜11,13に、第2の配線溝20内の第2の銅配線24、および第2の配線溝20に接続したビアホール15内のプラグとを設ける。ビアホール15の側壁に設けられた第1のサイドウォール17および第2のサイドウォール22と、第2の配線溝20の側壁に設けられた第2のサイドウォール22とを備える。これによりビアホール15のサイドウォールの膜厚を、第2の配線溝20のサイドウォールの膜厚より厚くする。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの下部電極のダメージを抑制することができる半導体装置およびその製造方法を提供するものである。

【解決手段】本発明の半導体装置は、立設する複数の電極と、前記電極の立設を保持する第1の絶縁膜と、前記電極が貫通するように前記第1の絶縁膜に形成され、各々の前記電極の外周側面の少なくとも一部に接触する複数の孔部と、前記第1の絶縁膜に形成され、前記複数の孔部のうちその一部の孔部に連結する第1の開口と、前記第1の絶縁膜に形成され、前記複数の孔部のいずれの孔部に対してよりも前記溝部に近接する位置に配置すると共に前記複数の孔部のいずれにも連結しない第2の開口とを、備えたことを特徴とすることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域に印加される応力分布のピークとソース領域近傍に発生する電位分布のピークの位置を最適化することで、キャリア速度を向上させて飽和電流特性を向上させることを可能にする。

【解決手段】半導体基板11に形成されたチャネル領域12と、前記チャネル領域12の一方側に形成されたソース領域19と、前記チャネル領域12の他方側に形成されたドレイン領域20と、前記チャネル領域12上にゲート絶縁膜13を介して形成されたゲート電極14と、前記チャネル領域12に応力を印加する第1、第2応力導入層21、23を有し、前記チャネル領域12と前記ソース領域19とのpn接合境界と、前記チャネル領域12と前記ドレイン領域20とのpn接合境界の間に、前記ソース領域19側の応力分布のピークと前記ドレイン領域20側の応力分布のピークが位置する。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィーのプロセスマージンを確保すると共に、ゲート電極とコンタクトプラグとの短絡が生じにくい半導体装置の製造方法を実現できるようにする。

【解決手段】半導体装置の製造方法は、層間絶縁膜114の上に第1の下部開口部115aを有する第1のマスク層115を形成する工程と、第1のマスク層115の上に第1の下部開口部115aを通して層間絶縁膜114を露出する第1の上部開口部116aを有する第2のマスク層116を形成する工程とを備えている。第1の下部開口部115aは、隣接するゲート電極102同士の間に形成され、ゲート電極102と平行な方向に延びる長辺と、ゲート電極102と交差する方向に延びる短辺とを有する平面方形状である。第1の上部開口部116aは、各辺の長さが第1の下部開口部115aの短辺よりも長い平面方形状である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】Siピラーの上部の面積を十分に確保でき、さらなるシュリンク(小型化)に対応できる半導体装置を提供する。

【解決手段】半導体基板1上に配置された複数の半導体ピラー部2と、半導体基板1上の第1方向における各半導体ピラー部2間に埋設された絶縁体ピラー部3と、半導体ピラー部2の側壁2cおよび絶縁体ピラー部3の側壁3cに第1方向に沿って連続して設けられた第1配線用凹部4と、半導体ピラー部2の第1配線用凹部4の内壁に設けられた第1絶縁膜と、第1配線用凹部4内に埋設された配線層6とを備える半導体装置とする。

(もっと読む)

自己整合ローカル・インターコネクト・プロセスにおけるゲートへの選択的なローカル・インターコネクト

【解決手段】

半導体デバイス生産プロセスは、ハードマスク(112)を用いて半導体基板上にトランジスタのゲート(102)を形成することを含む。ハードマスクは、ゲート上の1つ以上の選択された領域で選択的に除去される。選択された領域でのハードマスクの除去によって、実質的にトランジスタ上にある少なくとも1つの絶縁層を通してゲートが上部金属層に接続できる。導電性材料が、少なくとも1つの絶縁層を通して形成された1つ以上のトレンチ内に堆積される。導電性材料は、少なくとも1つの選択された領域内でゲートへのローカル・インターコネクトを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

半導体装置およびその製造方法

【課題】写真製版プロセスのマージンを大幅に拡大でき、かつマイクロローディング効果を低減することによって「開口不良」を抑制できるとともに「ショート」のプロセス裕度を確保しやすくし、かつコンタクト抵抗を低減できる半導体装置の製造方法を提供する。

【解決手段】活性領域に対して傾斜して延びるようにゲート電極層50と窒素を含む絶縁膜2とが積層される。シリコン酸化膜5が形成される。活性領域の幅より大きくかつ互いに隣り合う活性領域のピッチより小さい帯状の開口パターンが絶縁膜2に形成され、開口パターンから1対の不純物拡散領域の各々が露出させられる。開口パターンが導電層23で埋め込まれる。導電層23から1対の不純物拡散領域の各々に電気的に接続されたプラグ導電層23a、23bが形成されるとともに、プラグ導電層23a、23bの各上面と絶縁膜2の上面とが同一平面とされる。

(もっと読む)

半導体装置およびその製造方法

【課題】平坦な表面を有する層間絶縁膜を短時間で形成することができ、また、層間絶縁膜の厚さの増大を招くことなく、金属イオンによる半導体基板の汚染に対する長期信頼性を保証することができる、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、半導体基板2と、半導体基板2上に形成された層間絶縁膜8とを備えている。そして、層間絶縁膜8は、半導体基板2側から順に、HDP膜10、ゲッタリング層12およびNSG膜11が積層された構造を有している。ゲッタリング層12は、金属イオン、とくに可動イオンを捕獲する性質を有している。

(もっと読む)

半導体装置の製造方法

【課題】 極短時間アニール処理を行う際に、基板自体の損傷を抑制する半導体装置の製造方法を提供する。

【解決手段】 半導体基板上にゲート電極を形成する工程と、前記半導体基板に導電性の不純物を導入する工程と、前記半導体基板及び前記ゲート電極上に保護膜を形成する工程と、前記保護膜を形成後に前記半導体基板の裏面全面を研磨する工程と、前記半導体基板の裏面全面を研磨した後に前記半導体基板の表面が1000℃以上での保持時間が0.1秒以下となるような加熱処理により前記不純物を活性化する工程とを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

(もっと読む)

製造制御装置及び製造制御方法

【課題】膜厚変動を抑制することにより、トランジスタ特性のばらつきを低減できる製造制御装置及び製造制御方法を提供する。

【解決手段】第1半導体ウェハ上に絶縁膜を堆積する成膜装置30を制御する制御パラメータ(堆積時間ttarget)を算出する製造制御装置20であって、第2半導体ウェハの第2ウェハ表面積L1が大きいほど、成膜装置30に絶縁膜を厚く堆積させる制御パラメータ(堆積時間ttarget)を算出する。また、製造制御装置20は、第2ウェハ表面積L1が大きいほど堆積時間ttargetが長くなるように堆積時間ttargetを算出する堆積時間算出部116を備えてもよい。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線間容量の低い半導体装置を安定的に形成する。

【解決手段】配線1間に、仕切層5aで仕切られた複数の空洞の溝2を形成し、その後、それらの溝2を覆うように、配線1及び仕切層5aの上側に絶縁膜を形成する。配線1間に仕切層5aを設けることにより、絶縁膜形成に用いる絶縁膜原料3aの溝2内への進入が抑えられ、溝2内の絶縁膜形成が抑えられるようになる。それにより、配線1間の容量が低く、また、容量のばらつきが抑えられた半導体装置が形成可能になる。

(もっと読む)

半導体装置の製造方法

【課題】複数の同種の製造装置を用いて半導体装置を製造する場合に、製品間での寸法のばらつきの発生を抑制できる技術を提供する。

【解決手段】制御機器CDをそれぞれの露光機に対して個別に配置する。露光処理が完了した各ロットは、どの露光機で露光処理がなされたかによって分類され、露光機毎に、露光機を調整するためのパラメータが製品情報収集部CD1に収集され、最適製造条件計算部CD2にて処理条件が計算され、計算された処理条件が設定される。すべてのロットは、露光処理を行う露光機が予め割り当てられ、露光処理が済んでいないロットは、分類機CMによって割り当てられた露光機へ振り分けられ、制御機器CDによって求められた処理条件で露光処理が行われる。

(もっと読む)

241 - 260 / 1,106

[ Back to top ]