Fターム[5F033TT08]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 側壁絶縁膜 (2,038) | 電極、配線の側壁 (1,106)

Fターム[5F033TT08]に分類される特許

221 - 240 / 1,106

半導体装置の製造方法

【課題】

太幅配線の添加元素を細幅配線の添加元素とは独立に制御する。

【解決手段】

層間絶縁膜に、第1の幅を有する第1の配線溝および第1の幅より広い第2の幅を有する第2の配線溝を形成し、第1の配線溝および第2の配線溝内に、第1の添加元素を含む第1のシード層を形成し、第1のシード層上に第1の銅層を形成し、第1の配線溝内の第1の銅層および第1のシード層を残存させつつ、第2の配線溝内の第1の銅層および第1のシード層を除去し、その後、第2の配線溝内に、第2の添加元素を含む又は添加元素を含まない第2のシード層を形成し、第2のシード層の上に第2の銅層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】

微細化したMOSトランジスタを含む半導体装置において、リーク/ショートの可能性を抑制する。

【解決手段】

半導体装置の製造方法は、活性領域上に、ゲート絶縁膜とシリコン膜とを形成し、シリコン膜上方にゲート電極用レジストパターンを形成し、レジストパターンをマスクとして、シリコン膜を厚さの途中までエッチングしてレジストパターン下方に凸部を残し、レジストパターンを除去した後シリコン膜を覆うダミー膜を形成し、ダミー膜を異方性エッチングして、凸部の側壁にダミー膜を残存させつつ、平坦面上のダミー膜を除去し、ダミー膜をマスクとして、シリコン膜の残りの厚さをエッチングしてゲート電極を形成し、ゲート電極両側の半導体基板に、ソース/ドレイン領域を形成し、シリコン領域にシリサイドを形成する。

(もっと読む)

半導体装置

【課題】ヒューズ用開口部からガードリング外への水分等の伝達をより強固に防止する。

【解決手段】下地絶縁膜3上に第1シリコン膜パターンからなるシリコンヒューズとシリコン配線パターン7が形成されている。第1シリコン膜パターンとは別途形成された第2シリコン膜パターンからなり、上方から見てヒューズ5の周囲を取り囲み、一部分がシリコン配線パターン7上を跨いで下地絶縁膜上に環状に形成されたシリコンガードリング11が形成されている。シリコンガードリング11と交差している部分のシリコン配線パターン7表面にシリコン表面絶縁膜9が形成されている。シリコン配線パターン7とシリコンガードリング11はシリコン表面絶縁膜9により互いに絶縁されている。シリコンガードリング11上に金属材料からなる環状のガードリング17,19,25,27が上方から見てヒューズ5の周囲を取り囲んで形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】プラグの上面の形状を工夫することにより、半導体装置の電気的特性において、信頼性の向上を図ることができる技術を提供する。

【解決手段】本願発明におけるプラグPLGは、上面がコンタクト層間絶縁膜CILの表面(上面)よりも突出した上に凸のドーム形状をしている。つまり、プラグPLGは、上面が上に凸のドーム形状となっており、コンタクト層間絶縁膜CILの上面の高さよりもバリア導体膜BF1の上端部の高さが高く、かつ、タングステン膜WFの上端部の高さはバリア導体膜BF1の上端部の高さよりも高くなっている。

(もっと読む)

半導体装置

【課題】半導体チップのチップサイズを縮小化することができる技術を提供する。特に、LCDドライバを構成する長方形形状の半導体チップにおいて、短辺方向のレイアウト配置を工夫することにより、半導体チップのチップサイズを縮小化することができる技術を提供する。

【解決手段】LCDドライバを構成する半導体チップCHP2は、複数の入力用バンプ電極IBMPのうち一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されている一方、複数の入力用バンプ電極IBMPのうち他の一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されずにSRAM2a〜2c(内部回路)が配置されている。

(もっと読む)

半導体装置の製造方法

【課題】銅配線とアルミニウム配線との間のバリアを形成するための新規な技術を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の上方に形成された銅配線上に、絶縁膜を形成する工程と、絶縁膜に凹部を形成し、凹部の底に前記銅配線を露出させる工程と、凹部の底に露出した銅配線上に、250℃〜350℃の範囲の成膜温度で、フッ化タングステンの供給期間と供給停止期間とを交互に繰り返して、CVDでタングステン膜を選択的に成膜する工程と、タングステン膜上方に、アルミニウム配線を形成する工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】配線構造に接続される低抵抗の貫通プラグ、または貫通プラグ及びコンタクトプラグを有する半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板1と、半導体基板1の表面近傍に埋め込まれた素子分離絶縁膜2と、素子分離絶縁膜2を貫通するように半導体基板1の裏面から表面まで貫通し、半導体基板1中で素子分離絶縁膜2に囲まれた領域を有する上段部101aと上段部101aよりも径が大きい下段部101bとを含む多段構造を有する貫通プラグ101と、貫通プラグ101の半導体基板1の表面側の端部に接続され、半導体基板1の表面側の上方に形成された電極パッド104と貫通プラグ101を接続するコンタクトプラグ103と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細トランジスタのシリサイド形成工程において、ゲート間容量の増大がなく且つL字状スペーサの端部がエッチングされず接合リーク等の不良を防止できるようにする。

【解決手段】 半導体基板101上にゲート絶縁膜103を介して形成されたゲート電極104及びその側面上に形成された第1のサイドウォール108及びソースドレイン拡散層111を有する第1のトランジスタと、半導体基板上にゲート絶縁膜103を介して形成されたゲート電極104、その側面上に形成された第1のサイドウォール108、及びその外側に形成された第2のサイドウォール109を有する第2のトランジスタとを備えている。シリサイド形成領域Aにおけるゲート電極の上部及びソースドレイン拡散層の上部にはニッケルシリサイド層114が形成されており、第1のサイドウォール108は、第2のサイドウォール109をエッチングする際のエッチング材に対して耐性を有している。

(もっと読む)

半導体装置の製造方法

【課題】銅を用いた多層配線を有する半導体装置を高性能化する。

【解決手段】シリコン基板上に第1配線層用絶縁膜Z1を形成し、第1配線層用絶縁膜Z1に第1配線用孔部H1を形成する。その後、第1配線用孔部H1の側壁および底面を覆うようにして、タンタルまたはチタンを含む下部バリア導体膜eb1と、ルテニウムを主体とする上部バリア導体膜et1とからなる第1配線用バリア導体膜EM1を形成する。続いて、上部バリア導体膜et1をシード層として、電気めっき法により、銅を主体とする第1配線用導体膜EC1を形成し、CMP法により第1配線用導体膜EC1を第1配線用孔部H1に埋め込む。特に、上部バリア導体膜et1として、1〜5%の濃度で炭素を含ませるようにして、ルテニウムを主体とする導体膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、シリサイドを構成する金属のサイドウォールの直下への潜り込みの影響を低減する。

【解決手段】 シリコン基板上にゲート電極を形成する工程と、ゲート電極の側壁に、第1絶縁膜による第1サイドウォールと、第1サイドウォール上にあって、第1絶縁膜とはエッチング特性の異なる第2絶縁膜による第2サイドウォールを形成する工程と、シリコン基板および第2サイドウォールを含む表面に金属をスパッタリングにより堆積させ、金属の一部をシリコン基板に侵入させる工程と、シリコン基板上に堆積した金属を除去する工程と、金属の除去工程の後に熱処理を行って、スパッタリングによってシリコン基板に侵入した金属とシリコン基板中のシリコン原子とを反応させてシリサイド層を形成する工程とを備える。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法においてSRAMのセルサイズを縮小することを目的とする。

【解決手段】メモリセルCの活性領域31a、31bが画定されたシリコン基板31と、素子分離絶縁膜32上に形成され、第1の方向に延在するゲート電極35と、シリコン基板31とゲート電極35の上に形成された第1の絶縁膜42と、第1の絶縁膜42を貫通し、ゲート電極35と第1の活性領域31aに重なり、第1の方向に直交する第2の方向に延在する第1の銅プラグ45aと、第2の活性領域35b上の第1の絶縁膜42を貫通する第2の銅プラグ45bと、第1の絶縁膜42上に形成された第2の絶縁膜44と、第2の絶縁膜44に埋め込まれ、第1の銅プラグ45aの側面45xから第2の延在方向に後退して形成され、第1の銅プラグ45aの上面の一部のみを覆う銅配線48aとを有する半導体装置による。

(もっと読む)

半導体装置の製造方法

【課題】多層配線を有する半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1上に第1配線用絶縁膜IM1を形成し、第1配線用絶縁膜IM1に配線溝TM1を形成する。その後、配線溝TM1に銅を主体とする導体膜を埋め込むことで配線MW1を形成する。続いて、配線MW1上にキャップ導体膜MC1を形成した後、キャップ導体膜MC1に表面研磨を施す。特に、キャップ導体膜MC1はALD法によって配線MW1上に選択的に形成する。

(もっと読む)

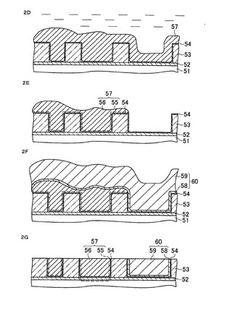

固体撮像装置およびその製造方法

【課題】本発明は、固体撮像装置に含まれる配線層間の絶縁膜の平坦性の向上に有利な技術を提供することを目的とする。

【解決手段】半導体基板上に、第1の配線層の導電パターンと、当該導電パターンの上部を覆う絶縁性を有する第1の研磨停止層とを形成する第1の形成工程と、第1の研磨停止層が形成された半導体基板上に層間絶縁層を形成する工程と、層間絶縁層の上に、半導体基板の少なくとも受光領域を覆うように絶縁性を有する第2の研磨停止層を形成する第2の形成工程と、導電パターンの上部を覆う第1の研磨停止層が少なくとも露出し、且つ受光領域を覆う第2の研磨停止層の少なくとも表面が研磨されるまで、第2の研磨停止層が形成された半導体基板の上側表面を平坦化するように研磨する研磨工程と、研磨された半導体基板に、第2の配線層の導電パターンを形成する工程とを含むことを特徴とする固体撮像装置の製造方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】比較的低い温度のもとで、良質で、かつ、薄いシリコン酸化膜等を均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】ステップ1では、半導体基板がモノシラン(SiH4)に暴露される。次に、ステップ2では、残存するモノシラン(SiH4)が排気される。そして、ステップ3では、半導体基板が亜酸化窒素プラズマに晒される。ステップ1〜3を1サイクルとして、必要とされる膜厚が得られるまでこのサイクルを繰り返すことで、所望のシリコン酸化膜が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法及び電子機器

【課題】光電変換部の面積を縮小することなく、光電変換部から電荷電圧変換部への信号電荷の転送性を改善することができる仕組みを提供する。

【解決手段】本発明の固体撮像装置は、光電変換部に蓄積された信号電荷を電荷電圧変換部26に転送する転送ゲート32と、電荷電圧変換部26で生成された信号電圧を出力するための配線42と、電荷電圧変換部26と配線42との電気的な接続を中継する中継電極38とを備える。中継電極38は、電荷電圧変換部26に電気的に接続するコンタクト部38cと、プラグ41を介して配線42に電気的に接続するコンタクト部38fと、転送ゲート32の上面に絶縁膜35を介して対向することにより当該転送ゲート32と容量的に結合する容量結合部38a,38bとを有する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の向上に寄与し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10上にトランジスタ34を形成する工程と、半導体基板上及びトランジスタ上に複数の部分膜36a、38a、40a、42を積層することにより、複数の部分膜を有する第1の絶縁層44を形成する工程と、第1の絶縁層上に、第1の絶縁層とエッチング特性が異なる第2の絶縁層46を形成する工程と、第1の絶縁層をエッチングストッパとして、第2の絶縁層をエッチングすることにより、第2の絶縁層にコンタクトホールを形成する工程と、コンタクトホール内に露出する第1の絶縁層をエッチングする工程とを有し、第1の絶縁層を形成する工程では、複数の部分膜のうちの最上層の部分膜以外の部分膜に対して膜を収縮させるキュア処理を行い、複数の部分膜のうちの最上層の部分膜に対してキュア処理を行わない。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を効率良く製造できるようにする。

【解決手段】半導体基板1上に積層された複数の層間絶縁膜16、19、22と、複数の層間絶縁膜16、19、22の最上面の上に形成され、外部からプローブが当てられるプローブ接触領域を有するパッド25と、複数の層間絶縁膜16、19、22の間に形成される複数層の配線12,15、18と、パッド25のプローブ接触領域の直下の領域に形成され、前記層間絶縁膜22が充填される非直線状スリットか孔の少なくとも一方を有する導電性パターンを有する応力緩和部42とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、バリアメタルの絶縁膜及びCuに対する密着性と、Cu拡散防止とを両立する。

【解決手段】 絶縁膜に設けた凹部の側壁にシール絶縁膜を形成し、シール絶縁膜の内側に順にシール絶縁膜との密着性が優れている第1の導電性バリア層、Cu拡散阻止能力が高い第2の導電性バリア層、及び、Cu系埋込電極との密着性が優れている第3の導電性バリア層の3層構造のバリア層を介してCu系埋込電極を設ける。

(もっと読む)

半導体装置の洗浄方法

【課題】ゲートメタル材料の溶解抑制と良好なコンタクト抵抗取得とを両立可能な半導体装置の洗浄方法を提供する。

【解決手段】半導体装置の洗浄方法は、以下の工程を備えている。シリコンを含み、かつ主表面MSを有する半導体基板SBが準備される。主表面MSの上にメタル層GMとシリコン層GPとを下から順に積層した積層ゲートGE2が形成される。主表面MSとシリコン層GP表面との各々にシリサイド層SCLが形成される。主表面MSと積層ゲートGE2表面との各々のシリサイド層SCLの上に絶縁層ILが形成される。半導体基板SBの主表面MSと積層ゲートGE2の表面との各々のシリサイド層SCLが絶縁層ILから露出するようにシェアードコンタクトホールSC2が絶縁層ILに形成される。シェアードコンタクトホールSC2に硫酸洗浄、過酸化水素水洗浄およびAPM洗浄をそれぞれ別工程で行うことによりシェアードコンタクトホールSC2に形成された変質層ALが除去される。

(もっと読む)

221 - 240 / 1,106

[ Back to top ]