Fターム[5F033VV09]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | 受動素子 (1,084) | 抵抗 (216)

Fターム[5F033VV09]に分類される特許

201 - 216 / 216

半導体装置及びその製造方法

【課題】 ゲート電極配線上のシリサイド層の断線に起因するゲート電極配線の高抵抗化を抑制する。

【解決手段】 半導体基板101の活性領域上にゲート電極104aを形成すると共に、該活性領域を囲む素子分離絶縁膜102上に、ゲート電極104aと同一材料からなるゲート配線104bを形成する。ゲート電極104a及びゲート配線104bのそれぞれの側面に絶縁性サイドウォール105を形成した後、ゲート配線104bの少なくとも一部分の側面に形成された絶縁性サイドウォール105を除去する。ゲート電極104a及びゲート配線104bのそれぞれの上面、並びにゲート配線104bの側面における絶縁性サイドウォール105が除去された部分にシリサイド層108を形成する。

(もっと読む)

電子回路を自己組織化させる方法及びその方法によって形成された回路

回路を組み立てる方法が、テンプレートを準備するステップと、半導体材料が該テンプレート上に自己組織化することを可能にするステップと、回路を形成するために、該半導体材料と該テンプレートとの間における接続の自己組織化を可能にするステップとを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 ヴィアホール、配線層の良好なカバレージを得ることにより、歩留りや信頼性の向上を図った半導体装置の製造方法を提供する。

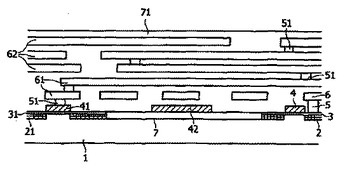

【解決手段】 半導体基板上1に、所定パターンの第1の金属層3を形成する工程と、全面に、第1の絶縁膜4を形成する工程と、前記第1の絶縁膜4上に、所定パターンの第2の金属層5を形成し、この第2の金属層5上に第3の金属層6を形成する工程と、前記第3の金属層6上に、第2の絶縁膜7を形成する工程と、前記第2の絶縁膜7を平坦化する工程と、全面に、第3の絶縁膜9を形成する工程と、前記第3の絶縁膜9上に反射防止膜10を形成する工程と、前記反射防止膜10上にレジスト層を形成する工程と、前記レジスト層をパターニングする工程と、パターニングされたレジスト層11をマスクとしてエッチングを行い、所定位置に前記第2の金属層に到達する開口部12、13を形成する工程と、前記開口部12、13内を含む全面に、第4の金属層及び第5の金属膜を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】 抵抗率のばらつきによる抵抗値のばらつきをもなくすため、抵抗素子の抵抗値を正確に知ることが可能であって、かつ、抵抗値を知るために回路領域が制限されることがない半導体装置の製造方法を提供する。

【解決手段】 抵抗素子を構成するポリシリコン膜と共にスクライブライン9上にもポリシリコン膜を成膜し、スクライブライン9上に成膜されたポリシリコン膜をパターニングし、モニタパターン7を形成する。また、モニタパターン7を使ったポリシリコン膜の抵抗率の測定結果に基づいて、抵抗素子を構成するポリシリコン膜を、このポリシリコン膜よりも上方に設けられる膜と同時にエッチングする。

(もっと読む)

電子デバイスの評価素子及び電子デバイスの評価方法

【課題】 電子デバイス内の所定構造体の抵抗ばらつきをその電子デバイスの形成位置毎に評価することができるようにした電子デバイスの評価素子及び電子デバイスの評価方法を提供する。

【解決手段】 シリコンウエーハW上に形成されるフラッシュメモリ300のセル内におけるコンタクト抵抗のばらつきを評価するための評価素子100であって、セル内のコンタクト部位と同じような構造を持ったユニットを複数個含むホールチェーン20を備え、第1、第2の電極パッド2a,2b間の抵抗値を測定する。次に、第1、第3の電極パッド2a,2c間の抵抗値を測定し、第1、第4の電極パッド2a,2d間の抵抗値を測定し、その後、第1、第5の電極パッド2a,2e間の抵抗値を測定する。ユニット数に対するホールチェーンの抵抗値の増加度合いから、フラッシュメモリ300セル内におけるコンタクト抵抗のばらつきを知ることができる。

(もっと読む)

スレーブ装置、マスタ装置及び積層装置

【課題】 本発明は、積層される複数の装置を識別しつつ、容易に積層装置を製造することができる技術を提供することを目的とする。

【解決手段】端子の配置が同一である複数のスレーブ装置とマスタ装置とが積層される積層装置を提供する。ここで、マスタ装置は、隣接するスレーブ装置の端子に識別コマンドを入力するコマンド送信手段を有する。また、スレーブ装置は、隣接するスレーブ装置及び自装置の少なくとも1の端子同士を接続する貫通配線と、識別コマンドを受信するコマンド受信手段と、識別コマンドに基づいて自装置の識別IDを設定する識別ID設定手段と、を有し、隣接するスレーブ装置同士を接続する端子の位置はスレーブ装置ごとに異なっており、各スレーブ装置のコマンド受信手段は、スレーブ装置毎に接続位置が異なる貫通配線を通過することにより、各スレーブ装置毎に異なる値に変化した識別コマンドを受信することを特徴とする。

(もっと読む)

バイポーラトランジスタを用いた電力増幅器とその製造方法

【課題】多セル構造のバイポーラトランジスタからなる電力増幅器では、高出力時に熱分布上コレクタ出力側が高くなるため、コレクタ出力側が熱暴走し、破壊に到る。

【解決手段】コレクタ出力側のトランジスタのベースに接続されたバラスト抵抗を大きくすることによって、発熱量の多いトランジスタのベース電位を低く抑えることができ、発熱によるベース電位の上昇の正帰還を抑制することができるため、熱暴走を避けることができる。

(もっと読む)

半導体装置

【課題】 巨大配線構造部を持つ半導体装置における微細配線構造部に発生する応力を緩和し、駆動電流が大きく高周波で動作する信頼性が高い半導体装置を提供する。

【解決手段】 半導体基板11上に、第1配線層と第1絶縁層が交互に積層された微細配線構造部12を設け、その上に、厚さが第1配線層の2倍以上である第2配線層15と、第2絶縁層14とが交互に積層された第1巨大配線構造部13aを設け、更に第1巨大配線構造部13a上に厚さが第1配線層の2倍以上である第3配線層17と、25℃における弾性率が第2絶縁層14より小さい第3絶縁層16とが交互に積層された第2巨大配線構造部13bを設ける。これにより、実装基板への搭載後に半導体装置に発生する応力を第1巨大配線構造部13a及び第2巨大配線構造部13bにおいて効果的に緩和し、微細配線構造部12にかかる応力を低減できる。

(もっと読む)

半導体装置及びその製造方法

【課題】 高抵抗素子を、半導体基板内の不純物拡散層を用いて形成することにより、サリサイドプロセスにおいても、構造的に、高抵抗素子部におけるシリサイド膜の形成を防止し、工程数を増大させることなく、高抵抗素子の形成を可能とする。

【解決手段】 シリコン基板11aの上の素子領域にゲート絶縁膜12aを介してポリシリコン配線12層を形成し、このポリシリコン配線12層の上から、不純物を拡散してポリシリコン配線12層の抵抗値を調整すると共に、このポリシリコン配線12層をマスクとしてシリコン基板11a上の素子領域内において、ポリシリコン配線12層に隣接する領域に不純物を拡散させN型不純物層11cを形成してこれを高抵抗素子とし、この高抵抗素子つまりN型不純物層11cの上にSiN膜14からなる絶縁膜を配置して、この上から、サリサイドを施して、ポリシリコン配線12の上にシリサイド膜17を形成することにより得られる。

(もっと読む)

複数の半導体層を備えた半導体デバイス

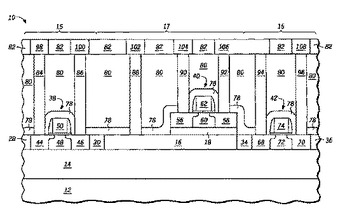

半導体デバイス構造(10)では、N及びPチャネルトランジスタキャリア移動度を別々に最適化するため、二つの半導体層(16、20)が使用される。これを決定する導電特性は、半導体の材料の種類、結晶面、配向性及び歪みの組み合わせである。シリコンゲルマニウムの半導体材料、圧縮性歪み、(100)の結晶面及び<100>の配向性を特徴とする導電特性の場合、Pチャネルトランジスタ(38)においてホール移動度が向上する。また、結晶面は(111)であってもよく、この場合、配向性は重要ではない。N型伝導に適した基板は、P型伝導に適した(又は最適)基板とは異なる。Nチャネルトランジスタ(40)は、好ましくは、引っ張り歪み、シリコン半導体材料及び(100)面を有する。別の半導体層(16、20)では、N及びPチャネルトランジスタ(38、40)はいずれもキャリア移動度に対し最適化される。  (もっと読む)

(もっと読む)

半導体装置の製造方法、及び本方法により製造される半導体装置

半導体装置を形成する方法は、半導体基板であって、パターニング済み配線層(120,520,1020,1620)が当該半導体基板の上に形成される構成の半導体基板(110,510,1010,1610)を設ける工程と、第1誘電体材料(130,530,1030,1630)を配線層の上に堆積させる工程と、第1電極材料(140,540,1040,1640)を第1誘電体材料の上に堆積させる工程と、第2誘電体材料(150,550,1050,1650)を第1電極材料の上に堆積させる工程と、第2電極材料(160,560,1060,1660)を第2誘電体材料の上に堆積させる工程と、第2電極材料をパターニングして第1キャパシタ(210,710,1310,1615)の上部電極(211,611,1111,1611)を形成する工程と、そして第1電極材料をパターニングして第2キャパシタ(220,720,1320,1625)の上部電極(221,721,1221,1621)を形成し、第1キャパシタの一の電極(212,712,1212,1612)を形成し、そして抵抗体(230,730,1330)を画定する工程と、を含む。  (もっと読む)

(もっと読む)

マイクロ波伝送線路

【課題】シリコン基板を信号伝播媒体とするマイクロ波伝送線路を長期安定性を維持しながら伝送損失の劣化を防止できるようにする。

【解決手段】高抵抗シリコンからなる基板1の主面上には、酸化シリコンからなる保護膜2、酸化アルミニウムからなる電位中和膜3及びストリップメタル4が順次形成されている。保護膜2は正の空間電荷を持ち、電位中和膜3は負の空間電荷を持ち、信号電界が基板1と保護膜2と電位中和とを伝播し、保護膜2及び電位中和膜3の各膜厚は、基板1の表面近傍における電位が中和されるように調整されている。

(もっと読む)

精密ポリシリコン・レジスタ・プロセス

【課題】 製造されるポリシリコン・レジスタのシート抵抗の許容誤差をより正確に制御する精密ポリシリコン・レジスタを製造するためのプロセスを提供する。

【解決手段】 プロセスは、一般に、部分的に形成されたポリシリコン・レジスタを有するウェハに対して、エミッタ/FET活性化高速熱アニール(RTA)を行うステップと、それに続いて、保護誘電体層をポリシリコン上に堆積させるステップと、ドーパントを該保護誘電体層を通して該ポリシリコンに注入して、ポリシリコン・レジスタの抵抗を定めるステップと、シリサイドを形成するステップとを含む。

(もっと読む)

基板上に多機能誘電体層を形成する方法

本発明は、多機能誘電体層を基板上、特に基板上に露出している金属配線系上に形成する方法に関する。本発明の目的は、銅による配線を形成するための多機能パッシベーション層を容易に形成する方法を提供するとともに、エレクトロマイグレーション、ストレスマイグレーション、および接着性を向上させる方法を提供することにある。本発明によれば、更なる金属層(5)を、露出した金属配線(3)の表面上に堆積することによって、本発明の目的は達せられる。この金属層は少なくともその一部が非導電性の金属酸化物に変換され、誘電体層となっている。  (もっと読む)

(もっと読む)

機密性を要する半導体製品、特にスマートカード・チップ

機密性を要する半導体製品、特にスマートカード・チップを提供するため、チップ設計によって実現されうる電気的に活性な構造(2、3、4、5、6)が、例えばシリコンからなるウェーハ(1)内及びウェーハ(1)上に、回路機能の形態で製造されるだけでなく、残りの領域に、それらの下に置かれた機密性を要する回路構造を解析するリバース・エンジニアを大幅に妨げる、互いに絶縁された充てん構造のさらなる導電性部分(42、61、62)(タイル)が設計プログラムによって形成される。形成された部分を説明された偶然の信号経路と連結するための形成された部分間のコンタクトは、「手で」、又は、当該設計プログラムと対応するルーティング・プログラムとの組合せによって配置されることができる。充てん導電性部分はさらに、さらなる回路機能(例えば解析回路)を提供するために、トランジスタ、ダイオード、抵抗器又はコンデンサなどの回路構成部品に接続されてもよい。  (もっと読む)

(もっと読む)

絶縁層及び接続孔の形成方法、配線構造及びその形成方法

【課題】 絶縁層及びヴィア形成において、形成された絶縁層の表面が非常に平滑となり、薄膜素子等を信頼性及び歩留り良く、高い自由度を以って形成でき、さらには微小なヴィア形成が可能である絶縁層及びヴィア(接続孔)の形成方法、及びそれを用いた多層配線基板並びにモジュール基板等の配線構造及びその形成方法を提供する。

【解決手段】 台座20を介してマスク基板21を配置し、この基板21とコア基板1との間に感光性エポキシ樹脂などの感光性絶縁材料3Aを介在させ、これをパターン露光して現像してヴィアホール7を形成する。この現像により、微小なヴィアホール7を形成できると同時に、マスク基板21のコア基板対向面21aによって絶縁材料(従って、絶縁層3)を平坦かつ滑らかな表面に、しかも常に設定された厚みに形成することができる。

(もっと読む)

201 - 216 / 216

[ Back to top ]