Fターム[5F033VV09]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | 受動素子 (1,084) | 抵抗 (216)

Fターム[5F033VV09]に分類される特許

101 - 120 / 216

半導体装置

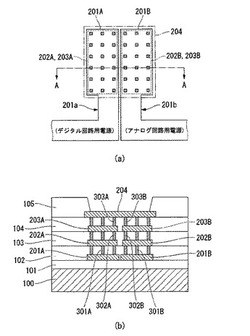

【課題】電源配線を介して伝播する電源ノイズを有効に抑制することができる半導体装置を提供すること。

【解決手段】異なる複数の回路に共通のパッド電極を介して給電するように構成された半導体装置において、前記パッド電極は、デジタル回路に給電するための電源配線の一部をなす導電膜(201A)と、前記導電膜から離間して形成され、アナログ回路に給電するための電源配線の一部をなす導電膜(201B)と、前記導電膜(201A,201B)の上層に絶縁膜を介して形成され、前記導電膜(201A,201B)の夫々と層間配線手段を介して電気的に接続された導電膜(204)とから構成される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】抵抗体の高抵抗化を妨げることなくレイアウト面積を小さくできるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】シリコン基板1にSTI層3を形成する工程と、STI層3を介してシリコン基板1上に第1ポリシリコン膜を形成する工程と、第1ポリシリコン膜を所定形状にパターニングして抵抗体11を形成する工程と、抵抗体11を覆うようにシリコン基板1上にシリコン酸化膜13を形成する工程と、シリコン酸化膜13を覆うようにシリコン基板1上に第2ポリシリコン膜を形成する工程と、第2ポリシリコン膜にドライエッチングを施して、抵抗体11の側面に沿ってバイアス用電極15を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】半導体チップに発生するクラックを検知することができ、さらに設計の自由度が向上するとともに配線のレイアウトの自由度やLSIのレイアウト効率およびパッケージ基板のレイアウト効率が向上した半導体装置を提供する。

【解決手段】本発明の半導体装置は、多層配線構造を有する半導体チップ10と、半導体チップ10上面において、半導体チップ10の外周縁に沿って形成された複数の電極パッド12と、複数の電極パッド12から選択された2つの第1電極パッド12aおよび第2電極パッド12bに接続するとともに、平面視において、半導体チップ10の全外周縁に沿って設けられた配線18とを備え、配線18は異なる層に形成された第1配線部14と第2配線部16とを含み、第1配線部14と第2配線部16とは接続プラグを介して直列に接続されている。

(もっと読む)

半導体装置の多層配線構造及び多層配線を有する半導体装置の水分検出方法

【課題】 多層配線を有する半導体装置において配線層内の水分の有無を直接評価することができる配線構造及び多層配線を有する半導体装置の水分検出方法を実現する。

【解決手段】 半導体装置1の多層配線構造において、第3配線層33より腐食されやすい材料により形成された薄膜抵抗体20a、20bが第3配線層33に配置され、薄膜抵抗体20a、20bの抵抗値を測定可能に構成されているため、水分の侵入などにより第3配線層33内に水分が存在する場合には、水分が第3配線層33内を移動して薄膜抵抗体20a、20bに到達し、薄膜抵抗体20a、20bが腐食されて抵抗が急増するので、薄膜抵抗体20a、20bの抵抗値を測定することにより第3配線層33内の水分の有無を直接検出することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 抵抗体を備えた半導体装置の小型化、集積化を図ること。

【解決手段】 半導体基板の表面に、半導体基板とは逆の導電型であるエピタキシャル層を形成し、抵抗となる部分以外にトレンチを形成し、前記トレンチに絶縁膜を埋め込むことで互いに分離された抵抗体を3次元的に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート形成溝内に埋め込んで形成される金属系ゲート電極を有するトランジスタ群と抵抗とを有する半導体装置で、抵抗値のばらつきをなくした抵抗形成を可能とする。

【解決手段】半導体基板11に、第1トランジスタ群と、これよりも低い動作電圧の第2トランジスタ群と、抵抗3とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介してシリコン系材料層71で形成された第1ゲート電極15を有し、第2トランジスタ群は、半導体基板11上の第1層間絶縁膜38に形成したゲート形成溝42内に第2ゲート絶縁膜43を介して金属系ゲート材料を埋め込むように形成された第2ゲート電極47、48を有し、抵抗3は、半導体基板11上に絶縁膜61を介してシリコン系材料層71と同一層で形成された抵抗本体部62と、この上部に形成された抵抗保護層63を有することを特徴とする。

(もっと読む)

半導体装置

【課題】銅めっき層をアンテナの導体に用いた、集積回路とアンテナが一体形成された半導体装置において、銅の拡散による回路素子の電気特性への悪影響を防止するとともに、密着性の良い銅めっき層を提供することを課題とする。また、集積回路とアンテナが一体形成された半導体装置において、アンテナと集積回路の接続不良に伴う半導体装置の不良を防止することを課題とする。

【解決手段】アンテナ101と集積回路100が一体形成された半導体装置において、アンテナ101として銅めっき層を用いるとともに、そのシード層107としてAg、Pd及びCuの合金を用い、バリア層116としてTiN又はTiを用いるものである。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生容量が低く、かつ、熱処理による抵抗値の変動が小さい抵抗素子を有する半導体装置を得ることのできる技術を提供する。

【解決手段】スパッタリングターゲット材料としてタンタルを用い、スパッタリングガスとしてアルゴンと窒素との混合ガスを用いた反応性直流スパッタリング法により、窒化タンタル膜からなる厚さ20nm、窒素濃度30原子%未満の第1抵抗層5a、及び窒化タンタル膜からなる厚さ5nm、窒素濃度30原子%以上の第2抵抗層5bを順次形成した後、第1及び第2抵抗層5a,5bを加工して抵抗素子R1を形成する。窒素濃度が30原子%以上の上部領域を設けることにより、配線工程において熱負荷が与えられても抵抗素子R1の抵抗変動率を1%未満に抑えることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】LCDドライバなどで小型化によるプラグの高抵抗化を抑制し、かつ、高耐圧MISFETのゲート電極と配線間の耐圧不良を改善できる技術を提供する。

【解決手段】LCDドライバにおいて、高耐圧MISFETでは、電界緩和用絶縁領域3上にゲート電極10bの端部が乗り上げている。そして、高耐圧MISFET上の1層目の層間絶縁膜上にソース配線あるいはドレイン配線となる配線HL1が形成されている。このとき、半導体基板1Sとゲート絶縁膜8の界面からゲート電極10bの上部までの距離をa、ゲート電極10bの上部から配線HL1が形成されている層間絶縁膜の上部までの距離をbとすると、a>bとなっている。このように構成されている高耐圧MISFETにおいて、配線HL1は、高耐圧MISFETのゲート電極10bと平面的な重なりを有しないように配置されている。

(もっと読む)

電気回路、その製造方法および電気回路製造装置

【課題】インクジェット方式を使用してパターン形成面に任意の電気回路を製造する。

【解決手段】基板1のパターン形成面100に、パターン形成用材料として導電性材料や絶縁性材料等を含んだ流動体10をインクジェット式記録ヘッド2より吐出する。そしてパターン形成面100に吐出された流動体10を固化させて電気回路102とする。材料を種々に変更しながら任意のパターンを作るために、コンデンサ、コイル、抵抗、能動素子等所望の回路素子を含んだ電気回路を製造できる。

(もっと読む)

半導体装置およびその製造方法

【課題】抵抗素子による半導体装置の厚みの増加や立体構造による導通不良、および抵抗素子と電極との間の界面によって生じる導通性の低下などに囚われない、接続信頼性の高い抵抗素子を備えた半導体装置を提供する。

【解決手段】第一電極1を一面に備える半導体基板2、半導体基板2の一面にあり、第一電極1と整合して第一開口部を設けた第一絶縁層3、第一絶縁層3に積層し、第一開口部と連通する第二開口部を配した第二絶縁層4、前記第一開口部と、前記第二開口部と、第二絶縁層4とを覆うように配したシード層5、および第一電極1と電気的に接続し、前記第二開口部を覆うようにシード層5上に配した第二電極6、を少なくとも備える半導体装置であって、シード層5は多層をなし、少なくとも第二電極6に接したシード層5上部は第二電極6と同じパターンであり、シード層5下部は抵抗素子として機能することを特徴とする半導体装置を提供する。

(もっと読む)

半導体装置

【課題】本発明は、ボンディングによって圧力を加えても抵抗値が変動しない半導体装置を提供することを目的とする。

【解決手段】N形半導体からなる第1の抵抗素子20及びP形半導体からなる第2の抵抗素子22は、直列接続されている。集積回路12に電気的に接続された電極14上にはバンプ18が設けられている。第1の抵抗素子20は、バンプ18とオーバーラップして第1の抵抗値を有する第1のオーバーラップ部24を含む。第2の抵抗素子22は、バンプ18とオーバーラップして第2の抵抗値を有する第2のオーバーラップ部26を含む。第1のオーバーラップ部24は、受ける荷重に比例して第1の抵抗値が低下する性質を有する。第2のオーバーラップ部26は、受ける荷重に比例して第2の抵抗値が増加する性質を有する。第1の抵抗値の低下率は、第2の抵抗値の増加率のx倍である。第1の抵抗値は、第2の抵抗値の1/x倍である。

(もっと読む)

半導体装置

【課題】電気特性の信頼性を向上させることができる半導体装置を提供する。

【解決手段】LCDドライバIC14(半導体装置)は、トランジスタ素子31と、トランジスタ素子31を電気的に分離するためのSTI分離層32と、STI分離層32及び拡散領域43上に跨って形成されたゲート配線34と、ゲート配線34とSTI分離層32との間に形成された絶縁膜41とを有する。絶縁膜41は、ゲート配線34に印加される高電圧に対して絶縁耐圧を確保するために用いられる。このような構成のLCDドライバIC14によれば、製造過程においてSTI分離層32に欠陥が生じた場合であっても、欠陥の影響を受けることなく、ゲート配線34に高電圧を印加することが可能となる。

(もっと読む)

半導体装置及び半導体装置製造方法

【課題】抵抗配線の配線幅のばらつきを抑えることで、抵抗値のばらつきを抑えることができる半導体装置及び半導体装置製造方法を提供する。

【解決手段】基板50上に配置される各種の素子を絶縁するフィールド酸化膜51と、フィールド酸化膜51上に線状の抵抗が列状に形成されてなる抵抗配線16とを備える半導体装置において、フィールド酸化膜51に底面2が平坦な凹部1と、凹部1の底面2の上方に抵抗配線16とを備えた。

(もっと読む)

半導体装置とその製造方法

【課題】ダマシンゲートプロセスを用いて抵抗素子を形成する場合、精度のよい抵抗素子を形成すされた半導体装置意およびその製造方法を提供する。

【解決手段】基板10に絶縁膜15が形成され、絶縁膜15に抵抗素子用溝15bが形成され、抵抗素子用溝15b内において抵抗素子用溝15bの全ての側壁面から少なくとも所定の距離A離間して抵抗素子17bが形成されている構成とする。

(もっと読む)

半導体装置

【課題】金属抵抗素子の形成位置を画定するための写真製版技術における露光時にレジスト膜中に定在波が発生するのを防止して金属抵抗素子の寸法バラツキを低減する。

【解決手段】金属抵抗素子27の下地絶縁膜23は、金属抵抗素子27の長手方向において、金属抵抗素子27の接続孔25,25間における上面の40%以上の部分を占める上側に凸の1つの曲面を備えている。金属抵抗素子27はその長手方向において下地絶縁膜23の曲面に起因して、コンタクト、コンタクト間における上面及び下面の40%以上の部分を占める上側に凸の1つの曲面を備えている。金属抵抗素子27の形成位置を画定するための写真製版技術における露光時に、金属抵抗素子27を形成するための金属膜の上面及び下面で露光光の反射光は上記曲面により散乱されるので、反射光と入射光によるレジスト膜中での定在波の発生が防止される。

(もっと読む)

半導体装置

【課題】電気特性の信頼性を向上させることができる半導体装置を提供する。

【解決手段】LCDドライバIC14(半導体装置)は、トランジスタ素子31と、STI分離層32と、LOCOS分離層33と、抵抗素子34とを有する。LOCOS分離層33は、STI分離層32と共に、トランジスタ素子31を電気的に分離するために用いられる。LOCOS分離層33上には、電気抵抗を得るために用いられる抵抗素子34が、ゲート絶縁膜37を介して形成されている。抵抗素子34は、例えば、ポリシリコン膜である。抵抗素子34は、例えば、層間絶縁膜42に形成されたコンタクトプラグ及び金属配線層を介して高電圧端子39(+15V)と接続されている。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコン抵抗素子内の不純物濃度の変動を抑制することを目的とする。

【解決手段】半導体装置の製造方法は、基板にポリシリコン膜を成膜する工程と、前記ポリシリコン膜に所定のパターンを形成する前に前記ポリシリコン膜に不純物を注入する第1注入工程と、前記ポリシリコン膜上に第1の拡散防止膜を成膜する工程と、前記ポリシリコン膜に注入した前記不純物を活性化させるための熱処理を行う工程と、を備える。

(もっと読む)

抵抗容量一体化構造

【課題】面積上の不利益を低減する事が出来る、抵抗容量構造体及びその製造方法を提供する。

【解決手段】抵抗容量構造体10はマイクロ電子回路内の少なくとも2つのノード間の電気容量を提供する。抵抗容量構造体の最下プレート12は電気抵抗層を含み、これは回路内の別のノードとの間の電気抵抗経路を提供する。抵抗容量構造体は、中間レベルの誘電体層14の上面又はその中に形成することができる。もしくは、電気抵抗層は、中間レベルの誘電体層の間に配置されたキャビティを充填して、結果的に中間レベルの誘電体層の間の電気抵抗経路を提供するために使用できる。

(もっと読む)

半導体装置の製造方法

【課題】抵抗変化型メモリ素子の抵抗変化の安定性と抵抗変化比を向上させた半導体装置の製造方法を提供する。

【解決手段】基板11を酸化物チャンバF3に搬入し、チタンを主成分とする第一ターゲットを酸素雰囲気の下でスパッタさせてチタン酸化物からなる酸化物層を形成し、酸化物層を有する基板11を照射チャンバF4に搬入し、酸化物層の表面にさらに酸素ラジカルを照射して可変抵抗体を形成した。

(もっと読む)

101 - 120 / 216

[ Back to top ]