Fターム[5F033XX25]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 基板と配線又は配線間の干渉防止 (1,198) | 基板と配線又は配線間の容量の低減 (1,039) | 同層間の容量の低減 (160)

Fターム[5F033XX25]に分類される特許

1 - 20 / 160

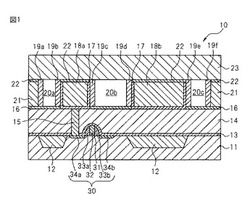

半導体装置及び半導体装置の形成方法

【課題】配線層間に絶縁物が堆積しない配線の形成方法を提供する。

【解決手段】半導体装置10は、第1絶縁体層14と、第1絶縁体層14上に間隔を空けて配置された複数の配線層18a、18bと、配線層18a、18bの側面上に形成された水素を吸蔵及び放出する水素吸蔵層19b、19c、19d、19eと、複数の配線層18a、18b上に、配線層間の溝20b上を跨ぐように形成された第2絶縁体層23と、を備えた配線を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】隣接する配線の間におけるリークを抑制することができる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、シリコンを含む基板11と、基板11の上に設けられた複数のメモリセルと、複数のメモリセルの上方に設けられた配線7と、配線7の上に設けられたリーク抑制層8と、前記リーク抑制層8の上方に設けられた層間絶縁膜10と、を備えている。そして、隣接するメモリセルの間、および、隣接する配線7の間には空隙12が形成され、リーク抑制層8の幅寸法は、配線7の幅寸法よりも短いこと、および、隣接するリーク抑制層8の間の寸法は、隣接する配線7の間の寸法よりも長いこと、の少なくともいずれかである。

(もっと読む)

半導体装置及びその製造方法

【課題】配線コーナーでの電子散乱を減らし、配線の抵抗率の増大を抑制する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に形成され、配線溝を有する層間絶縁膜とを備える。さらに、前記装置は、前記配線溝内に形成された配線を備える。さらに、前記配線溝の底面と側面との間の角部の曲率半径は、前記配線の配線幅の1/10以上である。

(もっと読む)

半導体装置およびその製造方法

【課題】良好なエアギャップを有する半導体装置およびその製造方法を提供する。

【解決手段】実施形態の半導体装置の製造方法は、基体上にライン・アンド・スペース構造を形成する工程と、前記ライン・アンド・スペース構造のラインの側壁および上面に絶縁膜材料で第1の膜を成膜する工程と、前記第1の膜を選択的に除去して前記ライン構造の頂面を露出させる工程と、前記ライン・アンド・スペース構造を跨ぐ第2の膜を塗布成膜法により成膜する工程と、前記第2の膜を熱処理により硬化させる工程と、を持つ。前記第1の膜の厚さは前記スペースの幅の1/2未満であり、前記第2の膜は、前記第1の膜に対する濡れ性が悪い材料で前記ライン・アンド・スペース構造を覆うことにより成膜される。

(もっと読む)

半導体装置の製造方法

【課題】高温化下でも安定な高信頼性を有する配線を容易に精度良く形成する方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板上方に窒化チタンからなる第1の絶縁層を形成し、第1の絶縁層に複数の溝を形成し、溝の底面及び側壁下部を覆う部分が溝の側壁上部を覆う部分よりも厚くなるように、溝の底面及び側壁を覆うバリアメタルを形成し、溝のバリアメタル上に金属膜を埋め込み、複数の配線を形成し、第1の絶縁層を除去して、隣り合う複数の配線の間に配線に接するような空隙を形成し、複数の配線の上面に、金属又は酸化物からなるキャップ膜を形成し、複数の配線の上面及び側壁を覆うようにシリコンナイトライドカーバイド膜又は窒化ボロン膜からなる拡散防止膜を形成し、複数の配線の上面を覆い、且つ、複数の配線間に空隙が形成されるように、第2の絶縁層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】信号速度の遅延を防止することができる半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、基板上に成膜された第1の絶縁膜と、配線と、第2の絶縁膜とを持つ。前記配線は、前記第1の絶縁膜に互いに平行に所定間隔で形成されたトレンチを埋め込むように金属で形成される。前記第2の絶縁膜は、前記第1の絶縁膜と前記配線とを覆うように前記第1の絶縁膜よりも誘電率の高い材料で成膜される。前記配線間の領域における前記第2の絶縁膜の下面は、前記配線の上面の周縁を互いに結ぶ面に対して上方へ離隔している。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】隣接するメモリセルゲート電極間に空隙を形成することで結合容量を抑制し、複数のコンタクト同士の短絡を防止しメモリの信頼性を向上する。

【解決手段】半導体記憶装置は、複数の選択ゲート電極間に形成され、選択ゲート電極に近接した側の側面と当該選択ゲート電極との第2間隔が第1間隔より広い層間絶縁膜11と、複数のメモリセルゲート電極間に空隙AGを備えるよう当該空隙AGの上部を被覆し、複数の選択ゲート電極間においては当該選択ゲート電極の側面および層間絶縁膜11の側面に沿って形成され、その上部に窪部Rを備えて形成されたエアギャップ形成膜12と、複数のメモリセルゲート電極上のエアギャップ形成膜12上に形成され、複数の選択ゲート電極間ではエアギャップ形成膜12の窪部Rの内側に埋込まれたリフィル膜13と、複数の素子領域に接触するように層間絶縁膜11に形成された複数のコンタクトCBa,CBbを備える。

(もっと読む)

電子部品の製造方法

【課題】導電膜を含む層の加工によって密の配線と疎の配線とが混在して形成された配線層で、所望の配線間の領域にのみ空隙を形成することができる電子部品の製造方法を提供する。

【解決手段】実施形態によれば、電子部品の製造方法は、まず、密の配線と疎の配線とを含む配線パターンとなるように、基板1上の導電性材料膜を含む加工対象を加工する。ついで、密の配線の形成領域にのみ配線間を埋め込む犠牲膜111を形成した後、基板1上に絶縁膜112を形成する。絶縁膜112上にレジスト113を塗布し、密の配線の形成領域上の一部と疎の配線の形成領域とが露出するようにレジスト113のパターニングを行った後、レジスト113をマスクとして絶縁膜112をエッチングする。さらに、密の配線の形成領域上の一部を通して、犠牲膜111を除去する。そして、疎の配線の形成領域で隣接する配線間を埋め込むように基板1上に埋込絶縁膜114を形成する。

(もっと読む)

配線の形成方法

【課題】配線が微細化された場合でも、所望の高さの配線を得ることができる配線の形成方法を提供する。

【解決手段】実施形態によれば、まず、絶縁膜11上に形成した犠牲導体膜12に配線形成用溝12a,12bを形成する。ついで、配線形成用溝12a,12bが形成された犠牲導体膜12上の全面にCuを堆積し配線形成用溝12a,12b内に流動するようにリフローさせて、配線形成用溝12a,12b内にCu膜14bを形成する。その後、犠牲導体膜12とCu膜14bを通電層としてめっき法によって配線形成用溝12a,12b内のCu膜14b上にCu膜14cを積み増す。ついで、Cu膜14b,14cからなるCu配線14をCMP処理して平坦化した後、犠牲導体膜12を除去する。その後、Cu配線14が形成された絶縁膜11上に絶縁膜15を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の金属配線の平坦化を行う場合、金属配線を下地層に形成した溝に埋め込むと、金属配線の配置をするとき、その変更工程が困難になるという問題があった。また、金属配線に寄生容量がついてしまい、電気信号の遅延などが発生してしまうという問題があった。

【解決手段】本発明の半導体装置の構造は、金属配線下の下地層である絶縁膜を加工して突起部を設ける。この突起部と所定の距離だけ離間して金属配線を設ける。この突起部により、平坦化のための研磨工程でも、不測の余剰研磨が発生しない。また、突起部と金属配線とが離間することにより、金属配線の配置の変更を容易に行うことができると共に、金属配線の寄生容量を低減できる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間容量を低減する。

【解決手段】半導体装置の製造方法は、基板の上方に絶縁膜を形成する工程と、絶縁膜を貫通する第1の溝及び絶縁膜の内部で終端する第2の溝を絶縁膜に形成する工程と、絶縁膜の内部で終端する配線溝を絶縁膜に形成する工程と、第1の溝の表面及び配線溝の表面に第1の金属膜を形成するともに、第2の溝の上方を覆うように第1の金属膜を形成する工程と、第1の溝及び配線溝に第2の金属膜を埋め込む工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】どのようなレイアウトの配線に対しても、個々の配線ごとにエアギャップ部を設ける。エアギャップ部によって、配線の寄生容量を低減する。

【解決手段】半導体装置は、層間絶縁膜と、層間絶縁膜内に埋め込まれた配線と、配線の側面と層間絶縁膜との間に設けられたエアギャップ部と、を有する。半導体装置の製造方法は、配線の側面上に第2のサイドウォール膜を形成した後、第2のサイドウォール膜の一部が露出するように第1の絶縁膜を形成する。次に、第2のサイドウォール膜を除去することによりサイドスペースを形成した後、サイドスペースが埋め込まれないように第2の絶縁膜を形成することによりサイドスペースから構成されるエアギャップ部を形成する。

(もっと読む)

半導体集積回路およびそのパターンレイアウト方法

【課題】CMP処理においてダミーパターンに機械的ストレスが作用しても、ダミーパターンが折れ曲がったり、ダミーパターンの一部が欠落したりすることを抑制できる半導体集積回路およびそのパターンレイアウト方法を提供する。

【解決手段】半導体集積回路は、所定の機能領域と、空き領域SP1に形成されたダミーパターンDMP1とを備える。空き領域SP1は、所定の機能領域同士の間に位置する。ダミーパターンDMP1は、枠状に形成されるとともに、ダミーパターンDMP1の外縁EDを規定する第1メタル部MT1と、第1メタル部MT1の内周側に位置し、第1メタル部MT1に連続するように形成された第2メタル部MT2と、第1メタル部MT1の内周側において第2メタル部MT2が形成されていない領域に位置する複数の非形成領域NTと、を有する。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

マンガン含有低誘電率膜及びその製造方法、半導体装置の製造方法並びに成膜装置

【課題】マンガン含有材料を利用して、低誘電率膜への銅の拡散を防止する。

【解決手段】成膜装置100では、制御部70の制御に基づき、処理容器1内を真空にして、ヒーター6によりウエハWを加熱しつつ、シャワーヘッド11のガス吐出孔13a,13bからウエハWへ向けて低誘電率材料とマンガン含有材料とを含む成膜ガスを供給する。高周波電源23からシャワーヘッド11に高周波電力を供給することにより、成膜ガスを解離させ、処理容器1内に成膜ガスのプラズマを生成させる。このプラズマによって、ウエハWの表面にMnを含有するSiCOH膜を成膜する。

(もっと読む)

半導体装置およびその製造方法

【課題】 デュアルダマシン法による配線構造の製造において、接続プラグ用のホールを通じて下層配線の表面に凹部をエッチング形成するとき、上層配線用の溝の底部が過剰エッチングされないようにする。

【解決手段】 TaNなどからなり、接続プラグに対応する開口を有する導電性膜パターン112をSiOCなどからなる層間絶縁膜111と113との間に設けた後、配線溝114、ホール115を形成する。次にTaN、Taなどからなる積層導電性膜116を堆積し、ホール115の底部の積層導電性膜116を除去し、さらに下層配線を構成するCu膜109を掘り込むエッチングを行う。このとき、導電性膜パターン112があるために配線溝114の底部の下にある層間絶縁膜111のエッチングを防止できる。その後、配線溝114およびホール115内にCuなどの導電性膜117を埋め込む。

(もっと読む)

半導体装置、及びその製造方法

【課題】配線の導通信頼性を損なうことなく、エアギャップを形成でき、配線間容量Cが低減した配線膜構造を有する半導体装置を提供することである。

【解決手段】 半導体装置の製造方法において、第1絶縁膜を形成する第1絶縁膜形成工程と、前記第1絶縁膜に配線膜を形成する配線膜形成工程と、前記配線膜が形成されてない箇所の前記第1絶縁膜にドライエッチングで溝を形成するドライエッチング工程と、前記ドライエッチング工程の後、前記溝が埋め尽くされることが無いよう、前記配線膜および前記溝上に第2絶縁膜を形成する第2絶縁膜形成工程とを具備する。

(もっと読む)

1 - 20 / 160

[ Back to top ]