Fターム[5F033XX35]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 成膜時の膜厚の制御 (46)

Fターム[5F033XX35]に分類される特許

1 - 20 / 46

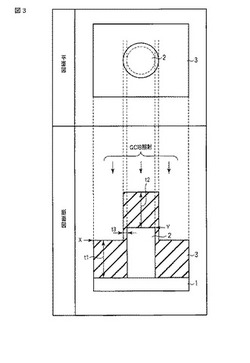

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】微細配線においてボイドの発生を確実に防ぐ。

【解決手段】層間絶縁膜102、103に形成された開口部12の底面及び側壁、並びに、開口部12以外の層間絶縁膜103上にあるフィールド部に、第一の金属を含むシード膜を形成し、シード膜上にレジストを形成して、開口部12をレジストで埋め込んだ後、開口部12の底面上に形成されたシード膜にレジストを残しつつレジストの一部を除去して、開口部12の側壁202A、Bの上部からフィールド部203にわたって形成されたシード膜を露出させ、開口部12の側壁の上部、及び、フィールド部203に位置するシード膜上に、第一の金属よりも抵抗率が高い第二の金属を含むカバー膜を形成した後、レジストを除去してシード膜を露出させ、露出させたシード膜に、第一の金属を含むめっき膜を形成するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホール内にめっき層から成るコンタクト層を埋め込んで上下層の電気的接続を行うときの、コンタクト層の埋め込み性を良好にする構造の半導体装置を提供する。

【解決手段】配線層12,16と、少なくとも底部において、三角形の平面形状であるコンタクトホール14と、めっき層から成り、コンタクトホール14の内部を埋めて形成され、配線層12,16に接続されたコンタクト層15とを含む、半導体装置を構成する。

(もっと読む)

半導体装置の製造方法

【課題】めっき膜厚の制御を精度よく行う。

【解決手段】半導体基板上に形成された絶縁膜に設けられた複数の凹部をめっき処理により導電性材料で埋め込むめっき工程を含む半導体装置の製造方法において、めっき工程は、複数の凹部のうち所定幅以下の微細な凹部が導電性材料で埋め込まれる際に、所定の第1の基準電流密度を半導体基板全面における各複数の凹部の側壁の面積を含む第1の表面積S1と各複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2に基づき補正した第1の電流密度でめっき処理を行う工程(S104)を含む。

(もっと読む)

半導体装置とその製造方法

【課題】配線加工時のエッチングレートの極端な上昇を抑え、プロセスを安定化させる。

【解決手段】炭化珪素基板1上に形成された炭化珪素層20の上に、ソース電極8、ゲート電極9、層間絶縁膜10、層間絶縁膜10上に形成されたソース電極上部配線11およびゲート電極上部配線12とが形成され、ソース電極上部配線11とゲート電極上部配線12の下には、これらの上部配線を構成する金属が炭化珪素層20に拡散することを抑制するためのバリアメタル16が形成されている。層間絶縁膜10には、炭化珪素層20上に形成されたソース電極8およびゲート電極9に到達するようにコンタクトホール13、15が形成されており、バリアメタル16はコンタクトホール内の電極と上部配線との界面、層間絶縁膜10の側壁と上部配線との界面、および側壁の上端部近傍と上部配線との界面にのみ形成されている。

(もっと読む)

タングステンスパッタリングターゲットおよびその製造方法

【課題】基板上に成膜したW膜の膜厚面内均一性を向上させることが可能であり、さらにはパーティクルの発生を減少させることが可能なWスパッタリングターゲットおよびその製造方法を提供する。

【解決手段】Wスパッタリングターゲットは、スパッタリングされる面のX線回折により得られた結晶面(110)のピークの半値幅が0.35以下であることを特徴とする。また、本発明の高純度Wスパッタリングターゲットの製造方法は、高純度W粉末を加圧焼結後、得られた焼結体をターゲット形状に加工後、ロータリー研磨およびポリッシングの少なくとも1種の研磨を施し、さらにエッチングおよび逆スパッタリングの少なくとも1種の研磨を施すことにより仕上げ加工することを特徴とする。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンの成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜を形成する工程と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】高容量・高精度なMIM静電容量素子を少ない工程で製造する技術を提供する。

【解決手段】第1層間絶縁膜17上に静電容量素子の下部電極21と第2層配線22とを同時に形成した後、第1層間絶縁膜17上に堆積した第2層間絶縁膜24に開口部34を形成する。次に、開口部34内を含む第2層間絶縁膜24上に順次堆積した容量絶縁膜27、第2金属膜および保護金属膜29を順次堆積し、第2層間絶縁膜24上の保護金属膜29、第2金属膜および容量絶縁膜27をCMP法で研磨・除去することによって、開口部34内に容量絶縁膜27、第2金属膜からなる上部電極28および保護金属膜29を残す。

(もっと読む)

スパッタリング用ターゲットおよび半導体装置の製造方法

【課題】スパッタリング用ターゲットから垂直方向に叩き出されるターゲット原子の個数を増大させる。

【解決手段】薄膜形成に用いられるターゲット原子Pから構成されたターゲット5において、ターゲット5から斜め方向に叩き出されたターゲット原子Pを側壁に衝突させることでターゲット原子Pがターゲット5から放出されるのを遮る凹部5aを表面に形成する。

(もっと読む)

膜形成用組成物、絶縁膜および半導体装置

【課題】低誘電率で、安定した絶縁性を示し、かつ、強度に優れ、膜厚や特性の不本意なばらつきが抑制された絶縁膜の形成に好適に用いることができる膜形成用組成物を提供すること。

【解決手段】本発明の膜形成用組成物は、分子内に、アダマンタン型のかご型構造を含む部分構造a1と、重合性の官能基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含むものであって、アセチレン結合を含むアセチレン系反応基を、分子内に複数個備えたオリゴアセチレン体を前記重合性化合物として含むとともに、前記オリゴアセチレン体が有する前記アセチレン系反応基の少なくとも一部が水素原子で置換された構造を有する水素化体を含み、前記重合性化合物が重合していない状態とした場合における、前記オリゴアセチレン体と前記水素化体の総モル数に対する、前記水素化体のモル分率が0.01〜10モル%であることを特徴とする。

(もっと読む)

成膜方法及びプラズマ処理装置

【課題】シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させることが可能な成膜方法である。

【解決手段】真空排気が可能になされた処理容器22内で被処理体Wの表面に対して薄膜を形成する成膜方法において、原料ガスを用いて処理容器内でプラズマCVD法により薄膜としてチタンを含む金属膜8を形成する金属膜形成工程と、処理容器内で金属膜に対してアニール処理を行うアニール工程とを有する。これにより、シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させる。

(もっと読む)

導電膜パターン及び導電膜パターンの形成方法

【課題】膜厚のばらつき及び表面の平坦性に優れ、基材との十分な密着性を有する導電膜パターンを、複雑、高価な設備、工程を必要とせずに形成する導電膜パターン及びその形成方法を提供する。

【解決手段】金属微粒子含有インクを基材上に配置し、焼成することにより形成される導電膜パターンにおいて、前記基材のインク被配置面に、有機塩あるいは無機塩の含有されたプライマー層が形成されているものであることを特徴とする導電膜パターン。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

小臨界次元のタングステン接点装置及び相互接続子の製法

【課題】高縦横比の特徴部のボイドなしの充填方法を提供する。

【解決手段】種々の実施例に於いて、この方法は低温化学蒸着工程によるタングステンでの特徴部の充填に関する。或る実施例に於いて、工程温度は特徴部充填の化学蒸着の間約350°C以下に維持される。この低温化学蒸着タングステン充填により、標準の化学蒸着充填と同様は薄膜抵抗を達成する一方、高縦横比の特徴部への向上された充填と下地層へとのフッ素移動への向上されたバリヤが得られる。発明は更に低抵抗を有するタングステンフィルムの堆積方法に関する。種々の実施例に於いて、この方法ではタングステンバルク層の堆積及び/或は低温化学蒸着によるバルク層の堆積の前に堆積された核形成層に低温低抵抗処理を実施し、その後高温化学蒸着を実施する。

(もっと読む)

半導体装置及びその製造方法

【課題】ウェハ面内の再配線層の厚みのばらつきを低減し、所望の電気的特性を得ることのできる多層再配線構造を有するWCSP型の半導体装置及びその製造方法を提供する。

【解決手段】第1の再配線層を形成する工程において、第1の導電材料をめっき法により成長させて第1の再配線層より厚い第1の導電材料層を形成し、第1のレジスト膜及び第1の導電材料層を主面側から研磨して表面を平坦化して、第1の再配線層を形成する処理、及び、第2の再配線層を形成する工程において、第2の導電材料をめっき法により成長させて第2の再配線層より厚い第2の導電材料層を形成し、第2のレジスト膜及び第2の導電材料層を主面側から研磨して表面を平坦化して、第2の再配線層を形成する処理の少なくとも一方の処理を行う。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いた薄膜トランジスタにおいて、電界効果移動度を向上させることを課題の一とする。また、薄膜トランジスタの電界効果移動度を向上させても、オフ電流の増大を抑制することを課題の一とする。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とゲート絶縁層の間に、該酸化物半導体層より導電率が高く、膜厚が薄い半導体層を形成することによって、該薄膜トランジスタの電界効果移動度を向上させ、且つオフ電流の増大を抑制することができる。

(もっと読む)

半導体装置、パターン形成方法および半導体装置の製造方法

【課題】開口部の間口部分の拡大を抑制しつつ、開口部内に埋め込み導体を埋め込みやすくする。

【解決手段】半導体ウェハW1の中心から左側に離れたチップ領域C1a、C1bでは、開口部13a、13b内の左右の壁面のうち右側の壁面にのみ深さ方向に沿って傾斜面を設け、半導体ウェハW1の中心から右側に離れたチップ領域C1d、C1eでは、開口部13d、13e内の左右の壁面のうち左側の壁面にのみ深さ方向に沿って傾斜面を設け、半導体ウェハW1の中心の近傍のチップ領域C1cでは、開口部13c内の左右の壁面には傾斜面を設けないようにする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線とバリア膜との密着性の低下、エレクトロマイグレーション耐性の低下、及び工程数の増加を抑制しつつ、めっき膜の膜厚がウェハ中心部とウェハ周辺部で異なることを抑制できる半導体装置の製造方法を提供する。

【解決手段】絶縁膜100に形成された溝102の側面及び底面に、添加元素を含む金属バリア膜120を形成する。次いで、金属バリア膜120上にシード膜142を形成し、さらにシード膜142をシードとしてめっき層(Cu膜144)を形成することにより、溝102内に金属膜140を埋め込む。次いで、金属バリア膜120及び金属膜140を熱処理することにより、金属バリア膜120と金属膜140の間に、金属バリア膜120を構成する金属、添加元素、及び金属膜140を構成する金属を含む合金層を形成し、かつ添加元素を金属膜140中に拡散させる工程とを備える。

(もっと読む)

パターン形成方法、デバイスおよび電子機器

【課題】幅が細く、かつ厚さが均一な断面形状を有するパターン形成方法、デバイスおよび電子機器を提供する。

【解決手段】本発明のパターン形成方法は、基板を所定の温度に加熱する第1の工程と、基板を所定の温度に保持しつつ、パターン形成材料を分散または溶解させた液体材料を基板上に滴下し、乾燥させる第2の工程と、液体材料を所定の温度の基板に滴下させたときの蒸発速度よりも蒸発速度を遅くさせる第3の工程と、液体材料が乾燥してなる乾燥体上に、液体材料を滴下する第4の工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】平坦性の良好な絶縁膜を所望の膜厚に精度良く且つ容易に形成可能な半導体装置の製造方法を提供すること。

【解決手段】複数の凸パターンが配置された半導体基板上に第1の絶縁膜を堆積する第1の工程と、凸パターンの上面に対応した領域の第1の絶縁膜を凸パターンの上面をストッパとして異方性エッチングにより除去し、凸パターンを露出させるとともに第1の絶縁膜からなる凸部を形成する第2の工程と、半導体基板上に、凸パターンおよび第1の絶縁膜からなる凸部を覆うように第2の絶縁膜を堆積する第3の工程と、第1の絶縁膜からなる凸部および該凸部を覆う第2の絶縁膜を少なくとも凸パターン上の第2の絶縁膜の表面高さまでCMP処理により除去することで平坦化し、凸パターン上に堆積された第2の絶縁膜と、隣接する凸パターン間の領域上に堆積された第1の絶縁膜と、を有する絶縁層を形成する第4の工程と、を含む。

(もっと読む)

1 - 20 / 46

[ Back to top ]