Fターム[5F038CA16]の内容

Fターム[5F038CA16]に分類される特許

1 - 20 / 320

可変インダクタ

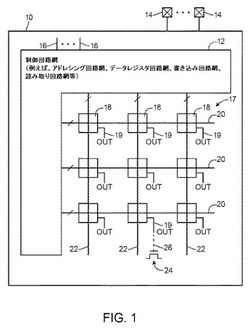

リレーデバイスを有するメモリ要素

【課題】メモリ要素有する集積回路を提供すること。

【解決手段】上記集積回路は、基板において形成された回路網と、回路網の上における複数の機械的リレーメモリ回路とを含む。集積回路は、回路網と複数の機械的リレーメモリ回路との間に配置された誘電スタックをさらに含む。誘電スタックは、複数の金属ルーティング層およびビア層を含む。回路網は、相補型金属酸化物半導体回路網を含む。回路網は、複数の機械的リレーメモリ回路に対する制御信号を生成するように動作可能である。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

半導体装置

【課題】半導体基板の上方にコイルが設けられた半導体装置において、コイル直下の半導体基板に回路を形成することができる半導体装置を提供する。

【解決手段】半導体装置は、一面11を有する半導体基板10と、半導体基板10の一面11に形成された絶縁層20と、絶縁層20の上方に形成されたコイル30と、を備えて構成されており、半導体基板10はコイル30の直下にスリット12を備えている。このスリット12は、コイル30のうち、半導体基板10の一面11に平行な面方向のうちの一方向に沿って形成された部分の直下に位置している。これにより、スリット12を境界として半導体基板10の渦電流面積が小さくなるので、半導体基板10に発生する渦電流による損失が低減し、コイル30の下部に位置する半導体基板10に回路を形成することが可能となる。

(もっと読む)

半導体装置および半導体パッケージ

【課題】パッドが設けられた面の向きを変えても、パッドを基板に接続するボンディングワイヤが交差しない半導体装置を提供する。

【解決手段】複数のパッドを含む第1のパッド群と、第1のパッド群に平行に一列に配置された複数のパッドを含む第2のパッド群と、第1のパッド群を基準にして第2のパッド群とは反対側に設けられた複数のバッファ回路を含む第1のバッファ回路群と、第2のパッド群を基準にして第1のパッド群とは反対側に設けられた複数のバッファ回路を含む第2のバッファ回路群と、第1のパッド群の複数のパッドのそれぞれを第2のバッファ回路群の複数のバッファ回路のそれぞれに対応して接続する複数の第1の配線と、第2のパッド群の複数のパッドのそれぞれを第1のバッファ回路群の複数のバッファ回路のそれぞれに対応して接続する複数の第2の配線と、を有する。

(もっと読む)

半導体装置

【課題】 貫通ビアを用い積層した半導体装置においては、信号を伝送する貫通ビアがオープンやショートした場合に、その貫通ビアを回避して積層チップ全体を正常動作させるために、複雑な回路を構成が必要であった。

【解決手段】 信号を伝送する貫通ビアにおいて、ビアの内壁を構成するシリコンに高い不純物の領域を形成して貫通導体とシリコン基板が接触したときに基板に接続されているVSSなどの基準電位に誘導する。故障モードを固定できるため、冗長化/復号化回路が簡単になるうえ、必要な冗長貫通ビアの本数を削減することができる。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体装置

【課題】積層チップシステムにおいて、各チップのIO回路の大きさを、そのドライブ能力やESD耐性能力を維持した上で、従来のサイズから縮小し、積層システムでは積層数に応じてIO数を変化させることができる半導体装置を提供する。

【解決手段】積層チップシステムにおいて、各チップは、各IO用の貫通ビア接続用パッド201に接続するIO回路202、スイッチ回路206にてIOチャネル207を構成し、このIOチャネル207を最大積層予定数のIOチャネル分まとめて接続してIOグループを構成し、このIOグループを1個以上持つ。各IO用の貫通ビア接続用パッド201は、貫通ビアにて別層のチップの同一位置のIO端子と接続される。インターポーザにおいては、実際の積層数が最大積層予定数に満たない場合はインターポーザ上で隣接するIOグループ内のIO用の接続用パッドが導体で接続されている。

(もっと読む)

スタックエラーを測定することのできる三次元集積回路

【課題】スタックエラーを測定することのできる三次元集積回路を提供する。

【解決手段】三次元集積回路100は、第1ウェハ110および第2ウェハ120を含む。第1ウェハ110は、第1導電パターン112を含む。第2ウェハ120は、第2導電パターン122を含み、第1導電パターン112に電気接続される。第1ウェハ110と第2ウェハ120の間の変位は、第1導電パターン112と第2導電パターン122の抵抗に基づいて決定される。

(もっと読む)

トランジスタ回路、双方向スイッチ回路、ダイオード回路及びトランジスタ回路の製造方法

【課題】トランジスタのゲートへの電流を防ぐ。

【解決手段】ノーマリーオン型の第1トランジスタと、ドレインが、第1トランジスタのソースと接続され、第1トランジスタとカスコード接続されたノーマリーオフ型の第2トランジスタと、第2トランジスタのソースと第1トランジスタのゲートとの間に設けられた、第2トランジスタのソースから第1トランジスタのゲートへと流れる電流を抑制する第1電流抑制部とを備えるトランジスタ回路を提供する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体層を用いた素子を配線層間に形成し、かつ、ゲート電極の材料を、配線の材料以外の導電体にする。

【解決手段】第1配線層150の表層には、第1配線210が埋め込まれている。第1配線210上には、ゲート電極218が形成されている。ゲート電極218は、第1配線210に接続している。ゲート電極218は、第1配線210とは別工程で形成されている。このため、ゲート電極218を第1配線210とは別の材料で形成することができる。そしてゲート電極218上には、ゲート絶縁膜219及び半導体層220が形成されている。

(もっと読む)

半導体装置

【課題】昇圧効率を向上させた昇圧回路を提供することを課題の一とする。または、昇圧効率を向上させた昇圧回路を用いたRFIDタグを提供することを課題の一とする。

【解決手段】単位昇圧回路の出力端子に当たるノード、または当該ノードに接続されたトランジスタのゲート電極をブートストラップ動作により昇圧することで、当該トランジスタにおけるしきい値電位と同等の電位の低下を防ぎ、当該単位昇圧回路の出力電位の低下を防ぐことができる。

(もっと読む)

基板導通を利用した積重ねダイ式の構成をもつ集積回路

【課題】積重ねダイ式の集積回路で使用するのに適した基板導通技術を提供すること。

【解決手段】集積回路が、積み重ねて配置された複数の集積回路のダイを備え、積重ねの頂部のダイを除く任意のダイが、それ自身および追加のダイ少なくとも1つのための電流を基板導通により担持する。1つの形態では、積重ねの底部のダイを除く各ダイが、下側のダイのバスまたはその他の電源導体を介して基板導通によりその電源電流を担持する。

(もっと読む)

半導体集積回路装置

【課題】高周波回路に於いては、トランジスタ等の能動素子間および能動素子と外部端子の間を直流的に遮断する必要がありため、MIMキャパシタ等が多用される。これらのMIMキャパシタのうち、外部端子に接続されたものは、外部からの静電気の影響を受けやすく、静電破壊等の問題を発生しやすい。

【解決手段】本願発明は、半絶縁性化合物半導体基板上に形成された半導体集積回路装置であって、外部パッドに電気的に接続されたMIMキャパシタの第1の電極は前記半絶縁性化合物半導体基板に電気的に接続されており、一方、前記MIMキャパシタの第2の電極は前記半絶縁性化合物半導体基板に電気的に接続されている。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】スイッチング用のパワーMOSFETと、そのパワーMOSFETよりも小面積でかつそのパワーMOSFETに流れる電流を検知するためのセンスMOSFETとが1つの半導体チップCPH内に形成され、この半導体チップCPHはチップ搭載部上に導電性の接合材を介して搭載され、樹脂封止されている。半導体チップCPHの主面において、センスMOSFETが形成されたセンスMOS領域RG2は、センスMOSのソース用のパッドPDHS4よりも内側にある。また、半導体チップCPHの主面において、センスMOS領域RG2は、パワーMOSFETが形成された領域に囲まれている。

(もっと読む)

半導体装置

【課題】半導体装置において、少なくとも容量素子とトランジスタとを有する回路要素が占める面積を小さくする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを有する半導体装置において、第2のトランジスタよりも上方に第1のトランジスタ及び容量素子を配置する。そして、第1のトランジスタのソース又はドレインの一方と、容量素子の一方の電極とを兼ねる共通電極を設ける。さらに、容量素子の他方の電極を共通電極よりも上方に配置する。

(もっと読む)

半導体装置

【課題】プログラマブルなアナログデバイスを提供する。また、電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルにおいて、ユニットセルのスイッチとして、第1乃至第4のトランジスタを用い、第1のトランジスタと第2のトランジスタとが接続された第1のノード、及び、第3のトランジスタと第4のトランジスタが接続された第2のノードの電位を制御することで、ユニットセルの出力を導通状態、非導通状態、又はアナログ素子を介した導通状態のいずれかに切り替える半導体装置を提供する。

(もっと読む)

半導体集積回路

【課題】電源が遮断されてもデータが保持される新規な論理回路を提供する。また、消費電力を低減できる新規な論理回路を提供する。

【解決手段】2つの出力ノードを比較する比較器と、電荷保持部と、出力ノード電位確定部とを電気的に接続することにより、論理回路を構成する。それにより、電源が遮断されてもデータが保持される論理回路を得ることができる。また、論理回路を構成するトランジスタの総個数を低減させることができる。更に、酸化物半導体を用いたトランジスタとシリコンを用いたトランジスタを積層させることで、論理回路の面積の削減が可能になる。

(もっと読む)

撚り合わされた導線を有する集積回路インダクター

【課題】集積回路インダクターを提供すること。

【解決手段】第1の端子と、第2の端子と、第1の端子と第2の端子との間に連結された伝導性経路とを備え、伝導性経路は、集積回路上に複数の撚り合わされた伝導性線を含む、インダクター。撚り合わされた伝導性線は、集積回路上に少なくとも1つの金属層から形成された少なくとも第1の伝導性線と、集積回路上に少なくとも1つの金属層から形成された少なくとも第2の伝導性線とを含む、インダクター。

(もっと読む)

1 - 20 / 320

[ Back to top ]