Fターム[5F038DF05]の内容

半導体集積回路 (75,215) | 集積回路機能及び回路ブロック構成 (8,544) | 特定機能回路(単一機能) (5,304) | メモリ (1,792)

Fターム[5F038DF05]に分類される特許

81 - 100 / 1,792

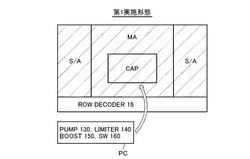

不揮発性半導体記憶装置

【課題】チップ面積を削減することのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施形態に係る不揮発性半導体記憶装置は、半導体基板と、半導体基板上に積層され、垂直方向に直列接続された複数のメモリセルを含むメモリセルアレイと、半導体基板上に設けられ、所望の電圧をメモリセルアレイに供給する電源回路とを備える。電源回路は、電圧を生成するポンプ回路と、ポンプ回路の出力端子に接続され、出力端子の電圧値が所定の値を下回った場合にポンプ回路へ制御信号を出力するリミッタ回路と、出力端子に一端が接続され、出力端子の電圧を調整するように構成されたキャパシタと、キャパシタの他端に接続され、制御信号に基づき所定の電流値の定電流を用いてキャパシタを充電するブースト回路と、ブースト回路の充電動作を停止させるスイッチとを備える。キャパシタは、メモリセルアレイの直下に設けられる。

(もっと読む)

半導体装置

【課題】 本実施形態は、出力ドライバのドライブ能力のキャリブレーション精度を向上することが可能な半導体装置を提供する。

【解決手段】 第1、第2のプルアップドライバユニットPUDUa、PUDUbは、プルアップドライバを調整する。プルダウンドライバユニットPDDUbは、プルダウンドライバを調整する。キャリブレーション回路CBCは、プルアップドライバのキャリブレーション時、基準電圧VREFと、基準抵抗RZQに基づく第1のプルアップドライバの出力電圧を比較して第1、第2のプルアップドライバユニットのドライブ能力を決定し、プルダウンドライバのキャリブレーション時、基準電圧と、第2のプルアップドライバとプルダウンドライバの接続ノードの電圧を比較してプルダウンドライバのドライブ能力を決定する単一の比較器COMPを有している。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体集積回路

【課題】突入電流が周辺の回路へ及ぼす影響を低減しつつ、停止状態にある回路を短時間に動作状態とすることが可能な半導体集積回路を提供することである。

【解決手段】本発明にかかる半導体集積回路1は、領域PD1と、制御回路25と、回路26と、を備える。領域PD1には、電源線VDDと電源線VSDとの間にそれぞれ接続されたスイッチ21_1、22_1、23_1と、電源線VSDと電源線VSSとの間に接続された回路35と、が配置されている。回路26は、電源線VDDおよび電源線VSSから電源が供給され、回路35よりも最低動作電圧が高い回路である。スイッチ22_1はスイッチ21_1よりもオン抵抗が低い。スイッチ22_1は領域PD1のうち回路26と最も離れた頂点の近傍に配置されている。

(もっと読む)

半導体チップのクラックのチェックテスト構造を有する半導体装置

【課題】半導体チップ積層後に、チップごとにクラックの有無検出可能な半導体装置の提供。

【解決手段】積層半導体装置において、半導体チップ21〜24は、基板10とこの表裏面の対向する位置に形成した対のテスト端子と配線61を備える。これらは、一対の(表側)第1のテスト端子621h、(裏側)第1のテスト端子621t及び複数対の(表側)第2のテスト端子622〜625h、(裏側)第2のテスト端子622〜625tで、貫通電極TSVT1が(表側)第1のテスト端子と(裏側)第1のテスト端子を接続し、貫通電極TSVT2〜5が対の(表側)第2のテスト端子と(裏側)第2のテスト端子同士を接続し、配線は、一端が第1のテスト端子と、他端が第2のテスト端子の一つに接続され、基板の外周に沿って延びる。また異なる半導体チップの上下に隣接する第2のテスト端子同士も接続する。

(もっと読む)

昇圧回路を備えた半導体装置

【課題】回路面積を縮小でき、昇圧効率の高い昇圧回路を備える半導体装置を提供する。

【解決手段】出力電圧を監視するモニタ電圧MON1に基づいて、出力電圧を所定電圧に制御する制御回路と、出力電圧を通常動作時に第1電圧に設定し、評価時に第1電圧より高い第2電圧に設定するトランジスタTR4,TR5と、出力電圧の振幅をクロック信号の振幅としてクロック信号を発生するクロックドライバ11と、コンデンサ及びダイオードを含む単位回路21が直列に複数段接続され、コンデンサに入力されるクロック信号により電源電圧VCCを昇圧するチャージポンプ12とを備える。

(もっと読む)

半導体装置及びこれを備えたメモリシステム

【課題】電源の瞬断および過渡状態での急激な電圧変動を起こさずに電源電圧を切り替えできる半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、電源スイッチと、降圧型の第1のレギュレータと、を備える。前記半導体装置は、入力端子に供給された外部電源電圧に基づいて内部電源電圧を出力端子から出力する。前記電源スイッチは、一端が前記入力端子に接続され、他端が前記出力端子に接続されている。前記第1のレギュレータは、前記電源スイッチの前記一端に接続された電源端子と、前記電源スイッチの前記他端に接続された電圧出力端子と、を有し、前記電源端子の電圧に基づいて前記電圧出力端子の電圧を目標電圧に近づくように制御する。前記目標電圧は、前記電源端子の電圧以上の第1電圧又は前記電源端子の電圧より低い第2電圧に切り替えられる。

(もっと読む)

半導体デバイスの電気的にプログラミング可能なヒューズモジュール

【課題】より小型なeヒューズモジュールを提供する。

【解決手段】半導体デバイスが、eヒューズモジュールおよびプログラミング電流生成器を有する。eヒューズモジュールが電気的にプログラミングするeヒューズ素子(226)のアレイを含む。プログラミング電流発生器が、複数の基準トランジスタ素子(M0〜M6)のセットと、基準トランジスタ素子(M0〜M6)を活性化させて、選択された基準電流を生成するセレクタ(254)と、アレイの選択されたeヒューズ素子(226)に、選択された基準電流に応じたプログラミング電流を印加して、eヒューズ素子(226)の抵抗をプログラミングするカレントミラー(M7、M8、M9)とを有する。

(もっと読む)

半導体試験装置及びそのテスト方法

【課題】メモリのテスト時の消費電流を抑え、メモリテスト時の周波数を高速化する。

【解決手段】制御回路103は、第1及び第2のテストパタンジェネレータ104、105によるテストがともにライトの場合、一方のテストパタンジェネレータによるテストシーケンスの実行を許可し、他方のテストパタンジェネレータに対してテストシーケンスの実行を不許可とし、一方のテストパタンジェネレータからメモリグループ101、102の対応する一方のグループに対してライトのテストパタンを出力し、他方のグループに対するライトの実行を、一方のグループのライトのテストサイクル単位で時間的にずらし、一方のテストパタンジェネレータによる一方のグループのライトの終了後、他方のテストパタンジェネレータによるテストシーケンスの実行を許可し、他方のテストパタンジェネレータから対応する他方のグループに対するライトのテストパタンを出力する。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

プログラマブルLSI

【課題】低消費電力で、動的コンフィギュレーションにも対応可能なプログラマブルLSIを提供する。

【解決手段】複数のロジックエレメントを有し、複数のロジックエレメントそれぞれは、コンフィギュレーションメモリを有する。複数のロジックエレメントそれぞれは、コンフィギュレーションメモリに記憶されたコンフィギュレーションデータに応じて、異なる演算処理を行い、且つ、ロジックエレメント間の電気的接続を変更する。コンフィギュレーションメモリは、揮発性の記憶回路と、不揮発性の記憶回路との組を有し、不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、当該トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子と、を有する。

(もっと読む)

半導体装置

【課題】実行するプログラムの種類又は発生する異常の種類などの、動作開始後の状況に合わせて外部端子の状態をプログラマブルに設定する。

【解決手段】プログラム処理回路によるデータ処理状態、プログラム処理回路が実行するプログラム若しくはデータ処理の種類、あるいはデータ処理による異常の種別毎に、異常発生時の入出力端子の端子状態を制御する制御データを予め不揮発性記憶部(140)に保存する。プログラム実行前若しくはプログラムの実行時に逐次に不揮発性記憶部に制御データを特定する検索キーを設定し、異常が発生した場合は、当該検索キーに基づいて参照された制御データに従って、入出力端子の状態をプルアップ、プルダウン、ハイインピーダンス又は前値保持の状態に設定する。

(もっと読む)

半導体集積回路及び誤動作防止方法

【課題】実システム動作中に電源状態を監視できる手段を提供する。

【解決手段】半導体集積回路は、発振器14と、電源電圧に応じて発振周波数が変化するリング発振器11と、発振器14の信号に基づいて、所定の判定期間を計測するインターバルタイマ13と、判定期間にリング発振器11が発振する発振周波数を測定する周波数測定用カウンタ12と、発振周波数の上限値と下限値とを保持する不揮発性メモリ15と、カウンタが測定した発振周波数が、不揮発性メモリ15が保持する上限電圧/下限電圧の判定コードの範囲内であるかを判定し、判定結果を出力する電圧判定回路16と、を備える。

(もっと読む)

データ保持装置及びこれを用いた論理演算回路

【課題】マスクパターンの疎密に起因する強誘電体素子の特性ばらつきを適切に低減することが可能なデータ保持装置及び、これを用いた論理演算回路の提供。

【解決手段】データ保持装置において、不揮発性記憶部に含まれる複数の強誘電体素子X(素子幅m)は、各々よりも素子幅の小さいダミー素子Y(素子幅n、ただしn<m)によって包囲されている。これによってマスクパターンの疎密に起因するエッチングのローディング効果を抑制する事が可能となる。

(もっと読む)

半導体装置

【課題】半導体装置の電源線および接地線の高抵抗化を抑制する。

【解決手段】第1の方向に延伸された第1の回路セル列及び第2の回路セル列と、第1の方向に延伸され、第1の回路セル列上に配置され、第1の電源線には第1の電源電位が供給される、第1及び第2の電源線と、第1の方向に延伸され、第2の回路セル列上に配置され、第2の電源電位が供給される第3の電源線と、第2の電源線と第3の電源線との間に接続され、導通状態において第2の電源線と第3の電源線とを接続して第3の電源線から第2の電源線に第2の電源電位を供給し、非導通状態において第2の電源線と第3の電源線とを電気的に切り離す第1のトランジスタと、第1の回路セル列に配置され、第1の電源線から供給される第1の電源電位と第2の電源線から供給される第2の電源電位との間の電源電圧で動作する第1の回路素子とを備える。

(もっと読む)

半導体装置

【課題】多層配線構造を有する半導体装置にダミーパタンを配線空隙に効率よく製造容易的に形成する。

【解決手段】多層配線構造の半導体装置において、狭い配線空隙(Area_S1)に、広い配線空隙(Area_S2)に形成されたダミーパタン(22,23)と異なる向きのダミーパタン(21)が形成されている。

(もっと読む)

半導体集積回路装置

【課題】低電源電圧が入力された際に昇圧動作を行い、高電源電圧が入力された際に該高電源電圧と同じ程度の電圧を出力する。

【解決手段】インバータ11にLo信号が入力されるとインバータ12〜14の出力がLo信号となる。そして、トランジスタ15がONし、静電容量16、ダイオード17の逆バイアス容量に電源電圧VCC2の電荷が充電され、ノードXの電位は電源電圧VCC2となる。続いて、インバータ11にHi信号が入力されると、トランジスタ14aがONし、ノードXとノードX’との電位が略同じとなる。インバータ13を構成するPチャネルMOSトランジスタがONし、静電容量16の容量カップリングによりノードX,X’が昇圧されて出力される。ここで、ダイオード17は、電源電圧VCC1が高電圧領域の電圧レベルの際には、電源電圧VCC1の電圧レベルがダイオード17を介して直流的に出力される。

(もっと読む)

半導体集積回路

【課題】不揮発性メモリを搭載した半導体集積回路において、外部端子を通して不揮発性メモリの特性テストを実施し、更に、その外部端子にサージ電圧が印加された場合であっても、そのサージ電圧が不揮発性メモリに伝わることを防止する。

【解決手段】半導体集積回路は、不揮発性メモリと、不揮発性メモリに対するデータ書き込み時、書き込み電圧が印加される書き込み制御線と、書き込み制御線に接続された第1ノードと、第1スイッチ回路を介して第1ノードに接続された外部端子と、スイッチ回路を介さずに外部端子に接続された第1ESD保護回路と、動作モードに応じて第1スイッチ回路をON/OFF制御する制御回路と、を備える。動作モードは、外部端子を用いて不揮発性メモリの特性テストを行うテストモードと、外部端子を使用しないユーザモードと、を含む。テストモードにおいて、制御回路は、第1スイッチ回路をONする。ユーザモードにおいて、制御回路は、第1スイッチ回路をOFFする。

(もっと読む)

半導体装置

【課題】本発明は、第1状態と第2状態との二つの状態のうち、第1状態に初期化し、初期化した第1状態に対応する電位の信号を生成することが可能な半導体装置を提供する。

【解決手段】本発明は、“0”(第1状態)と“1”(第2状態)との二つの状態のうち、“0”に初期化し、初期化した“0”に対応する電位の信号Aを生成することが可能な半導体装置10である。半導体装置10は、並列に複数接続され、“0”と“1”との二つの状態を保持することが可能なフリップフロップ回路2と、複数のフリップフロップ回路2と接続し、複数のフリップフロップ回路2のうち、少なくとも一つのフリップフロップ回路2で保持する状態が“0”の場合、“0”に対応する電位の信号を生成し、出力するAND回路3とを備える。

(もっと読む)

半導体集積回路

【課題】内蔵された回路の状態を確認する機能を備えた半導体集積回路を更に小型化することができる技術を提供

【解決手段】半導体集積回路1では、コアLSI11と周辺LSI12との間の内部配線WIが異常であると判定回路15が判定すると、判定回路15は、リングオシレータ16Aを発振させることを指示する情報(第1発振指示情報)をリングオシレータ制御部17へ出力する。そしてリングオシレータ制御部17が第1発振指示情報を取得すると、リングオシレータ制御部17が、発振周波数f1で発振するように構成されたリングオシレータ16Aを発振させる。そして、半導体集積回路1内で発生している磁界を近磁界プローブで測定し、発振周波数f1で大きさが変動する磁界を検出した場合に、リングオシレータ16Aが動作していると判断することができる。

(もっと読む)

81 - 100 / 1,792

[ Back to top ]