Fターム[5F038DF05]の内容

半導体集積回路 (75,215) | 集積回路機能及び回路ブロック構成 (8,544) | 特定機能回路(単一機能) (5,304) | メモリ (1,792)

Fターム[5F038DF05]に分類される特許

21 - 40 / 1,792

半導体装置

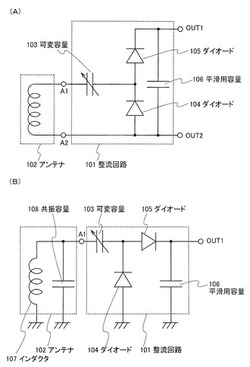

【課題】半導体素子が有する寄生容量や寄生インダクタンスによる電力の損失を抑えるこ

とが出来る、整流回路の提供を課題とする。

【解決手段】入力された交流電圧の振幅に従い、前段の回路と該整流回路の間におけるイ

ンピーダンスを整合または不整合にする。入力される交流電圧が規定の振幅以下である場

合は、インピーダンスを整合にし、該交流電圧をそのまま整流回路に印加する。逆に入力

される交流電圧が規定の振幅よりも大きい場合は、インピーダンスを不整合にし、反射に

より該交流電圧の振幅を小さくしてから整流回路に印加する。

(もっと読む)

半導体装置

【課題】スタンバイ状態時における第1導電型のトランジスタでの劣化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、第1導電型のトランジスタを含み縦列接続された複数の回路と、複数の回路の其々の入力端子のうち他の回路と接続された接続入力端子と接続し接続入力端子の電圧を制御するための制御信号の活性化に応じて、接続入力端子に、該接続入力端子から電圧を受け付ける回路内の第1導電型のトランジスタを非導通状態とする第1の電圧を供給する制御回路と、を備える。

(もっと読む)

半導体記憶素子及び半導体記憶装置

【課題】LSI素子の性能劣化及びヒューズ素子の欠陥の増加を抑制できる半導体記憶素子及び半導体記憶装置を提供する。

【解決手段】半導体記憶素子100は、第1ヒューズ線111と、第1ヒューズ線111と並列接続された第2ヒューズ線112とを有し、切断されているか否かによって2値のデータを保持するヒューズ素子110と、一端がワード線130に接続されており、ヒューズ素子110に電流を流すか否かを選択する選択素子120と、を備える。

(もっと読む)

半導体装置

【課題】直流電源配線に電流が流れたか否かを検出可能な回路を備えた半導体装置を提供する。

【解決手段】半導体装置において、駆動回路BLDU,BLDD,BLBDU,BLBDDは、電流磁界またはスピン注入によってトンネル磁気抵抗素子TMR,TMRBを第1の磁化状態に初期設定するために、制御信号線BL,BLBに直流電流を流す。電源配線DLは、トンネル磁気抵抗素子TMR,TMRBに近接して設けられる。ここで、トンネル磁気抵抗素子TMR,TMRBは、電源配線DLに直流電流が流れるときに生じる電流磁界によって第2の磁化状態に変化する。センスアンプ10は、トンネル磁気抵抗素子TMR,TMRBが第1の磁化状態から第2の磁化状態に変化したか否かを判定するために、制御信号線BL,BLBを介してトンネル磁気抵抗素子TMR,TMRBに流れる電流を検出する。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体装置及びこれを備える半導体モジュール

【課題】データ出力バッファの正確なインピーダンスキャリブレーション動作を行う。

【解決手段】電源ラインVL1とデータ端子24との間に接続されたP型トランジスタユニット201と、電源ラインVL1とキャリブレーション端子ZQとの間に接続されたP型トランジスタユニット111〜114と、キャリブレーション端子ZQの電位が基準電位VREFと一致するよう、P型トランジスタユニット111〜114インピーダンスを調整し、一致した状態におけるP型トランジスタユニット111〜114の一つのインピーダンスをP型トランジスタユニット201に反映させるインピーダンス制御回路とを備える。これにより、基準電位VREFが電源電位VDDの半分のレベルからオフセットしたレベルに設定されている場合であっても、正確なキャリブレーション動作を行うことができる。

(もっと読む)

半導体装置

【課題】配線間の寄生容量を削減可能にした半導体装置を提供する。

【解決手段】X方向に配列する複数のトランジスタについて、夫々が、対応するダミーゲートDG1,DG2を挟む複数のソース拡散層S1,S2に接続する第2及び第3の金属配線M12,M13は、2つのS1,2つのS2に夫々接続する複数の第1のビアV1の両方を含む第1の幅L1と、V1を含まず、L1よりも短い第2の幅L2と、を有する。ドレイン拡散層D1に接続する第1の金属配線M11と、M12との間、並びにM11及びM13の間の夫々は、L1に対応する第1のギャップSP1と、L2に対応する、L1よりも大きな第2のギャップSP2と、を有する。好ましくは、M11〜M13の夫々と第2のビアV2を介して接続される第4〜第6の金属配線M24〜M26の夫々は、L1よりも短い第3の幅L3を有する。

(もっと読む)

半導体装置

【課題】半導体チップの面積を縮小することが可能な半導体装置を提供する。

【解決手段】半導体チップを有する半導体装置では、半導体チップに設けられた内部回路のテストを行うテスト回路と、そのテストが行われている間は内部回路を駆動せず、テストが行われた後に内部回路を駆動する駆動回路とを有し、内部回路に接続された信号線が、テスト回路と駆動回路とで共用される。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。

【解決手段】薄膜トランジスタ119と、薄膜トランジスタ上に第1の層間絶縁膜156と、第1の層間絶縁膜上の、ソース領域またはドレイン領域の一方に電気的に接続される第1の電極114と、ソース領域またはドレイン領域の他方に電気的に接続される第2の電極110と、第1の層間絶縁膜、第1の電極、及び第2の電極上に形成された第2の層間絶縁膜135と、第2の層間絶縁膜上の、第1の電極または第2の電極の一方に電気的に接続される第1の配線177と、第2の層間絶縁膜上の、第1の電極または第2の電極の他方に電気的に接続されない第2の配線178とを有し、第2の配線と前記第1の電極または第2の電極の他方は、第2の層間絶縁膜中の分断領域169によって、電気的に接続されない半導体装置及びその作製方法に関するものである。

(もっと読む)

半導体装置

【課題】適切に電源電圧を負荷回路に供給することができる、半導体装置を提供する。

【解決手段】電圧トランスファ20及びセンスノード配線33が設けられており、電圧トランスファ20は、各Sub−Arrayに応じて設けられたNMOSトランジスタTRにより、ノード32とノード30との間が接続される。電圧トランスファ20のトランジスタTRは、ソース及びドレインの一方が電源線31の各Sub−Arrayに応じた位置に接続されており、ソース及びドレインの他方がセンスノード配線33に接続されている。また、トランジスタTRのゲートには、対応するSub−Arrayのデコード信号A0〜AXが入力される。

(もっと読む)

半導体設計方法及び半導体設計装置

【課題】フリップフロップ追加による利益と、スキャンFFの段数増加による不利益と、を考慮に入れ、スキャンテスト回路の設計を行う半導体設計方法が、望まれる。

【解決手段】複数のスキャンFFから構成されるスキャンテスト回路の設計方法は、複数のスキャンFF間の遅延値を抽出することで、スキャンテスト回路の動作レート候補値を複数算出する第1の工程と、中継用フリップフロップの追加を仮定し、複数の動作レート候補値をそれぞれ使用して、スキャンテストの実施に必要な時間をスキャンシフト時間として算出し、スキャンシフト時間に基づき、中継用フリップフロップを追加することの効果が最も高い動作レート候補値を、中継用フリップフロップの追加後のスキャンテスト回路に適用する動作レートとして選択する第2の工程と、動作レートを満たすように、複数のスキャンFF間に中継用フリップフロップを追加する第3の工程と、を含んでいる。

(もっと読む)

半導体装置

【課題】

実施形態は、解析が簡便な半導体装置を提供する。

【解決手段】

本実施形態の半導体装置は、内部信号を伝送可能な第1配線101と、第1配線101

と電気的に接続された測定電極100と、測定電極100と隣接するように配置され、内

部信号を計測するときに接地電位VSSが印加され、内部信号を計測する以外のときに所

望の電圧が印加されたダミー電極102,103とを備える。

例えば、測定電極100は、環状に形成されており、ダミー電極は、第1電極102と

第2電極103とを有し、第1電極102は、測定電極100の内側に形成された空間に

隣接するように配置され、第2電極103は、測定電極100の外側に隣接するように配

置される。

(もっと読む)

半導体装置

【課題】寿命が長い半導体装置を提供する。

【解決手段】このLSIは、2つのCPU1,2と、CPU1,2のうちのいずれか1つのCPUを示す論理レベルのデータ信号が書き込まれた記憶回路4と、リセット信号REが非活性化レベルにされてLSIのリセットが解除された場合、記憶回路4の記憶データの論理レベルに対応するCPUのみに電源電圧を供給するとともに、記憶回路4の記憶データを現在の論理レベルと異なる論理レベルのデータ信号に書き換える制御回路3,5とを備える。したがって、故障の検知や、厳密なタイミング制御を必要とせずに、CPUの長寿命化を図ることができる。

(もっと読む)

半導体装置

【課題】残渣による配線間のショートの発生を防ぐ。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

(もっと読む)

半導体集積回路及びその制御方法

【課題】デカップリング容量素子の信頼性と、フラッシュメモリの動作モードに対応した供給電流の補償を損なわずに、フラッシュメモリの面積増加を抑制する。

【解決手段】本発明に係る半導体集積回路10は、フラッシュメモリ部12と、フラッシュメモリ部12に電圧を供給する昇圧回路13と、昇圧回路13の出力に一端が接続されたデカップリング容量素子15と、フラッシュメモリ部12の動作モードに応じて、デカップリング容量素子15の他端の電位を制御する制御回路14とを備える。

(もっと読む)

半導体装置及びこれを備える情報処理装置

【課題】安定したチャージポンプ動作を行う。

【解決手段】ノードA,Bを有するコンデンサC1と、VDDレベルからVSSレベルの間で振幅するポンピング信号PUMP1をコンデンサC1のノードAに供給するポンピング回路110と、コンデンサC1のノードBをVPPextレベルにプリチャージし、ポンピング信号PUMP1がVSSレベルからVDDレベルに変わった時に、コンデンサC1のノードBをVPPextレベルよりも高いレベルに駆動する出力回路120とを備える。本発明によれば、コンデンサC1のノードAをポンピングするための電圧と、コンデンサC1のノードBをプリチャージするための電圧が異なっていることから、昇圧電圧を効率よく生成することできる。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

半導体集積回路

【課題】設計する回路の中で電流の多く流れる信号線を容易に見つけ出すことができ、容

易にその部分の電流を測定できるスタンダードセルを提供することを課題とする。

【解決手段】電流検出用テストパッドを少なくとも2つ有するスタンダードセルを自動レ

イアウトで配置する。そして、2つのテストパッド間を接続する配線を切断することで、

該2つのテストパッドを電流測定用テストパッドとして利用する。なお、スタンダードセ

ル内の2つのテストパッド間は、過電流が流れることにより電流の流れる経路が遮断され

る配線によって接続される構成としてもよい。また、2つのテストパッド間をつなぐ配線

部にメモリ又はアナログスイッチを設ける構成としてもよい。

(もっと読む)

再構成可能な集積回路ユニットを備えた論理回路及びその論路回路のエラー修正方法

【課題】エラー箇所の特定を実施する際に、システムを停止しないでエラー発生前の高信頼性までシステム性能を復帰させる。

【解決手段】同一動作を行う複数個の再構成可能な集積回路ユニットを備え、複数の該集積回路ユニットのそれぞれに複数のバンクを有する論理回路において、入力されたデータを、複数個の前記集積回路ユニットの各バンクに振り分けて入力する入力データ制御部と、複数個の集積回路ユニットの各バンクから出力されるデータを比較して、データ間の不一致を検出するエラー解析部と、エラー解析部から、データ間の不一致の通知を受けた場合に、複数個の集積回路ユニットの該当するバンクの再構成を行う構成情報制御部と、を備える。

(もっと読む)

半導体チップ

【課題】チップ面積が小さく低コストで誤動作が発生し難い半導体チップを提供する。

【解決手段】半導体チップ1をパッケージ3に搭載する場合は80個のパッドPAをパッケージ3の80個の端子TAに接続し、半導体チップ1をパッケージ5に搭載する場合は100個のパッドPA,PB,PCをパッケージ5の100個の端子TAに接続する。半導体チップ1の内部回路は、電極E1,E2が絶縁されている場合は80端子のマイクロコンピュータ4として動作し、電極E1,E2がボンディングワイヤWの端部によって短絡されている場合は100端子のマイクロコンピュータ4として動作する。したがって、パッケージの端子数を設定する専用パッドが不要となる。

(もっと読む)

21 - 40 / 1,792

[ Back to top ]