Fターム[5F038DF05]の内容

半導体集積回路 (75,215) | 集積回路機能及び回路ブロック構成 (8,544) | 特定機能回路(単一機能) (5,304) | メモリ (1,792)

Fターム[5F038DF05]に分類される特許

41 - 60 / 1,792

半導体装置及びその製造方法

【課題】トランジスタの集積度が高い半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、を備える。そして、前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なる。

(もっと読む)

メモリ電圧制御装置およびメモリ電圧制御方法

【課題】メモリを低電圧で制御して省電力制御を図ることおよびエラーの発生を防止することを改善できるメモリ電圧制御装置およびメモリ電圧制御方法を提供する。

【解決手段】メモリ電圧制御装置10およびメモリ電圧制御方法は、デバイス13,14と、デバイス13,14の異常を検出する電気機器11と、を備え、電気機器11は、デバイス13,14の異常を検出した時に、デバイス13,14に対して動的または静的に駆動電圧を昇圧する制御を行う。

(もっと読む)

昇圧回路

【課題】負荷電流に応じて昇圧能力を調整することにより、過剰な昇圧回路出力リップルを抑制する。

【解決手段】昇圧回路1は、昇圧部出力CPOの電圧を変動させて昇圧回路出力VPPを生成し、昇圧回路出力VPPの負荷電流の大きさに応じて制御電圧CON1を生成する制御部2と、制御電圧CON1に応じて電源VDDP1の電圧を変動させることにより昇圧部電源VDDPを生成する電源降圧部3と、昇圧回路出力VPPの電圧と目標電圧との差分に応じて昇圧部電源VDDPの電圧を変動させることにより昇圧部出力CPOを生成する昇圧部4とを備える。

(もっと読む)

半導体装置

【課題】出力端子に接続される内部回路の動作開始を早く行うことができる定電圧発生回路を備えた半導体装置を提供する。

【解決手段】クロック信号VOSCが入力されると、内部の複数のノードにおいてポンピング動作を行い、入力端子に供給される電荷を複数のノードを介して出力端子へと順次転送し、出力端子から出力電圧を発生する昇圧回路20と、出力電圧が予め設定された電圧に達した場合、非活性レベルの検知信号VUPTを出力する電圧検出回路30と、検知信号が活性レベルの場合、クロック信号を昇圧回路へ出力し、検知信号が非活性レベルの場合、クロック信号の昇圧回路への出力を停止するクロック信号制御回路40と、を備え、クロック信号制御回路は、検知信号が非活性レベルであっても、入力される制御信号RESETTのレベルに応じてクロック信号を昇圧回路へ出力する。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑えつつ、多数の配線間の時定数を一致させる。

【解決手段】半導体装置は、第1のサイズを持つ第1の外部端子と、第1のサイズよりも小さな第2のサイズを持つ複数の第2の外部端子と、第1の外部端子及び複数の第2の外部端子が、前記第1のサイズを基準として配列される外部端子領域と、外部端子領域に隣接して形成され、複数の第2の外部端子にそれぞれ対応付けられる複数の回路と、複数の第2の外部端子とそれら対応付けられた複数の回路との間をそれぞれ接続する複数の配線とを備える第1のチップを含む。複数の第2の外部端子及びそれらに接続された複数の配線は複数のインタフェースを構成し、複数のインタフェースの夫々は、互いに実質的に等しい時定数を持つように、時定数を調整する調整部を少なくとも一つ含む。調整部の少なくとも一部は、外部端子領域内の第1のサイズと第2のサイズとの差により生じるマージン領域に配置される。

(もっと読む)

検証装置、検証方法及びプログラム

【課題】検証する範囲を少なくして、検証コストや検証時間の増大を抑制する。

【解決手段】抽出部12が、第1のクロック信号で動作する回路部21と、第2のクロック信号で動作する回路部22とを含む検証対象回路(論理回路20)から、ハンドシェイクの手順に従って回路部21と回路部22間でのデータの送受信を行うハンドシェイク部23を抽出し、検証部13が抽出されたハンドシェイク部23の信号が、その手順を満たすかを検証し、手順を満たさない信号があるとき、回路部21と回路部22のうち当該信号を出力する側で、当該信号が手順を満たさなくなる条件が回路動作時に起こり得るか検証する。

(もっと読む)

半導体装置

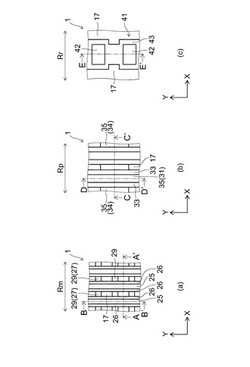

【課題】Y方向に隣接する2つの回路ブロックに対しX方向に延在する制御線からタイミング信号を同時に供給する。

【解決手段】例えば、Y方向に配列されたポートPT1,PT2と、ポートPT1,PT2にそれぞれ接続された回路C1,C2と、X方向に延在し回路C1,C2それぞれに含まれるサブ回路SC1,SC2を共通に制御する制御線CTL1を備える。サブ回路SC1,SC2のY方向における中間座標である座標Y1は、ポートPT1,PT2のY方向における中間座標Y0とは異なる。制御線CTL1からサブ回路SC1,SC2へのY方向における距離は互いに等しい。本発明によれば回路C1,C2の動作タイミングを正確に一致させることが可能となる。しかも、複数の制御線を必要とする場合であっても、制御線ごとに対応するサブ回路までの距離を一定とすることが可能となる。

(もっと読む)

駆動回路、ドライバICチップ、駆動装置、プリントヘッド、画像形成装置、表示装置及び制御方法

【課題】被駆動素子に対する補正データを記憶する補正データメモリ(MEM)を少ない素子で構成する。

【解決手段】補正データメモリ(MEM)が、第1及び第2のインバータ(224、223)で構成されるメモリセルと、第1のインバータ(224)の入力端子に接続され、メモリセルへデータを伝達する第1導電形の第1のスイッチ素子(231,232)と、第1のインバータ(224)の出力端子と、グランドの間に接続された第1導電形の第2のスイッチ素子(500)とを備え、第1のインバータの出力端子が第2のインバータの入力端子に接続され、第2のインバータの出力端子が第1のインバータの入力端子に接続されている。

(もっと読む)

半導体装置

【課題】昇圧効率を向上させた昇圧回路を提供することを課題の一とする。または、昇圧効率を向上させた昇圧回路を用いたRFIDタグを提供することを課題の一とする。

【解決手段】単位昇圧回路の出力端子に当たるノード、または当該ノードに接続されたトランジスタのゲート電極をブートストラップ動作により昇圧することで、当該トランジスタにおけるしきい値電位と同等の電位の低下を防ぎ、当該単位昇圧回路の出力電位の低下を防ぐことができる。

(もっと読む)

半導体集積回路装置

【課題】部品点数を増加させることなく、低コストでかつ効率的に半導体集積回路装置の高信頼性化を実現させる。

【解決手段】ユーザプログラムの実行時において、周期タイマ2からタイマカウンタ信号が出力されると、CPUコア6,7はASEメモリ3に格納されたテスト用プログラムを実行し、そのチェック結果をトレースメモリ11に格納する。デバッグ回路10は、トレースメモリ11に格納されたチェック結果のコンペア処理を行い、CPUコア6,7が正常か否かを判定する。正常の場合、CPUコア6,7は、再びユーザプログラムを実行する。異常の場合、デバッグ回路10は、状態信号をシステム停止回路12に出力する。この状態信号を受けると、システム停止回路12は、動作制御信号をCPUコア6,7にそれぞれ出力し、半導体集積回路装置1の再起動処理が行われる。

(もっと読む)

半導体装置及び半導体装置の試験方法

【課題】不良電流パスの選別に要する時間を短縮する。

【解決手段】半導体装置は、それぞれ少なくとも1つの貫通電極を含み、インターフェイスチップ内に第1のノードn1を有する複数の電流パス101Xと、互いに異なる複数の電圧値からなる比較電圧DACOUTを生成する比較電圧生成部102と、複数の電流パス101Xそれぞれの第1のノードn1の電圧TSVCXと、比較電圧DACOUTの上記複数の電圧値それぞれとを比較し、比較の結果を示す比較結果信号CMPXを電流パス101Xごとに出力する比較部103と、比較結果信号CMPXに応じて、複数の電流パス101Xのそれぞれが高抵抗化しているか否かを示す結果信号RESLTXを生成する結果信号生成部104とを備える。

(もっと読む)

半導体装置

【課題】データの誤書換を防止することが可能な低消費電力の半導体装置を提供する。

【解決手段】マイクロコンピュータ1は、電源電圧VCCが正常範囲から外れた場合にリセット信号REを出力する電圧検出器2と、各々がデータを不揮発的に記憶する複数のメモリセルを含むメモリアレイ5と、イレーズコマンドまたはプログラムコマンドに応答して、電圧検出器2の応答時間TR以上の保留時間TSだけ経過した後にデータのイレーズまたはプログラムを実行し、リセット信号REに応答してリセットされる制御部7とを備える。したがって、電圧検出器2の応答時間TRが長い場合でも、データの誤書換を防止できる。

(もっと読む)

半導体装置

【課題】誤ってテストモードにエントリされたとしても、正常に動作させる。

【解決手段】半導体装置は、内部回路をテストするテスト回路2に対してテストを開始させるテストモードエントリ信号が入力されたことに応じて、内部のラッチ10をセットすることにより、テスト回路2に対し、テスト回路2の駆動を許可するテストイネーブル信号をラッチ10から出力するテスト信号発生回路1を備える。テスト信号発生回路1が、ラッチ10がテストイネーブル信号を出力している場合、テストイネーブル信号を遅延させて、ラッチ10をリセットするリセット信号を生成するリセット信号生成回路30と、ラッチ10がテストイネーブル信号を出力している場合に、外部から供給されるトグル信号に基づいて、リセット信号生成回路30によるリセット信号を生成する動作を初期化する遅延初期化信号を出力する遅延初期化回路40と、を有している。

(もっと読む)

半導体集積回路装置の試験方法及び半導体集積回路装置

【課題】 半導体集積回路装置の試験方法及び半導体集積回路装置に関し、所定の回路動作を行った状態のまま半導体集積回路装置側の操作で所望の温度に制御する。

【解決手段】 スクリーニング試験前の工程にて測定された半導体集積回路装置の回路毎の電源電流値或いは電流ランクのいずれかにより、前記半導体集積回路装置全体毎または個別の回路動作毎に、適切な周波数に周波数設定し、所望の発熱量になるよう発熱量の制御を行い、スクリーニング試験時に、所定の回路動作を行った状態のまま所望の温度に制御する。

(もっと読む)

低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法

【課題】低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法を提供する。

【解決手段】NMOS素子及びPMOS素子が何れもアナログ及びデジタルモードのような相異なるモードで動作される半導体素子において、これら素子の要求される動作モードによって特定素子にストレスエンジニアリングを選択的に適用する。フォトレジスト160をデジタル回路領域のPMOSトランジスタのみを覆うように形成し、Ge、Siなどのイオン162をストレスコントロール膜150に注入する。デジタル回路領域のPMOSトランジスタを除くあらゆる領域でストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換され、デジタル回路領域のPMOSトランジスタのチャネル104bだけに圧縮応力が印加される状態が残る。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】実際の強誘電体メモリセルについて疲労特性を直接に測定する試験方法を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に形成された強誘電体キャパシタの疲労特性の面内分布を取得する第1の工程と、前記面内分布に基づいて、半導体装置を製造する第2の工程と、を含み、前記第2の工程は、前記半導体装置が形成される基板上に複数の強誘電体キャパシタを形成し、前記第1の工程で取得された疲労特性の面内分布から、前記半導体装置が形成される基板上の特定領域を指定し、前記特定領域に形成された前記強誘電体キャパシタについて疲労特性を測定し、前記特定領域の強誘電体キャパシタについて測定した前記疲労特性に基づき、前記特定領域の強誘電体キャパシタについて良否判定を行い、前記良否判定の結果が良であれば、前記複数の強誘電体キャパシタの全てについて良と判定する。

(もっと読む)

半導体装置の製造方法

【課題】スループットを低下させずに異なるメモリセルの誘電体膜とキャパシタの誘電体膜を同時に形成するための半導体装置の製造方法を提供する。

【解決手段】第1酸化膜18、窒化膜19、第2酸化膜20を順に形成した第1の誘電体膜を第1の半導体膜16上に形成する工程と、第1領域I内の第1の誘電体膜21をエッチングする工程と、第1領域Iの半導体基板1の表面に第3酸化膜25を形成する工程と、第1領域VI及び第2領域IIIに開口部28a、28bを有し、さらに第3領域II内の第1の誘電体膜21を覆う形状を有するマスク28を半導体基板1の上方に形成する工程と、マスク28の開口部28a、28bを通して、第1領域VI内の前記第3酸化膜25と前記第2領域III内の第1の誘電体膜21の第2酸化膜20を同時にエッチングする工程を含む。

(もっと読む)

縦構造キャパシタを備える半導体装置

【課題】縦構造キャパシタの剥離を防止し、チップサイズの増加を抑制した半導体装置を提供する。

【解決手段】半導体装置には、第1の回路の機能素子として使用される第1の縦構造キャパシタと、第2の回路の機能素子として使用され、第1の縦構造キャパシタよりも容量値の大きい第2の縦構造キャパシタと、が含まれている。半導体装置では、第1の縦構造キャパシタを、第2の縦構造キャパシタに隣接、又は、包含させるようにレイアウトする。

(もっと読む)

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

半導体装置

【課題】半導体装置において、少なくとも容量素子とトランジスタとを有する回路要素が占める面積を小さくする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを有する半導体装置において、第2のトランジスタよりも上方に第1のトランジスタ及び容量素子を配置する。そして、第1のトランジスタのソース又はドレインの一方と、容量素子の一方の電極とを兼ねる共通電極を設ける。さらに、容量素子の他方の電極を共通電極よりも上方に配置する。

(もっと読む)

41 - 60 / 1,792

[ Back to top ]