Fターム[5F038DF05]の内容

半導体集積回路 (75,215) | 集積回路機能及び回路ブロック構成 (8,544) | 特定機能回路(単一機能) (5,304) | メモリ (1,792)

Fターム[5F038DF05]に分類される特許

141 - 160 / 1,792

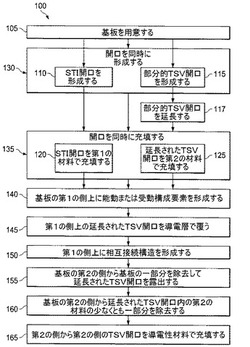

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

半導体装置

【課題】不良解析が容易な半導体装置を提供する。

【解決手段】実施形態によれば、待機状態と動作状態とを有する半導体装置が提供される。前記半導体装置は、機能素子部と、電荷供給部と、を備える。前記機能素子部は、前記動作状態において動作する第1機能素子を含む。前記電荷供給部は、前記第1機能素子に接続される。前記電荷供給部は、前記待機状態において第1制御信号が入力されたときに前記第1機能素子に電荷を供給する。

(もっと読む)

半導体装置

【課題】出力バッファにおいて発生したノイズが、他の出力バッファに伝搬することを防止し、且つ各出力バッファに安定した電源供給を行うことが可能な半導体装置を提供する。

【解決手段】外部電圧が供給される複数の電源パッド111,112と、複数のデータ出力パッド113,114と、複数の電源パッド111,112に共通接続された電源幹線411,412と、電源幹線から分岐した複数の分岐電源配線411B,412Bと、それぞれ対応する分岐電源配線411B,412Bから供給される電源電圧によって動作し、それぞれ対応するデータ出力パッド113,114を駆動する複数の出力バッファ72と、複数の分岐電源配線411B,412Bにそれぞれ設けられたローパスフィルタ回路1000とを備える。

(もっと読む)

電力の島を使用した集積回路での電力の管理

【課題】集積回路において、消費電力を効率的に利用することを目的とする。

【解決手段】システム及び方法は、電力の島を使用して集積回路の電力を管理する。集積回路は、消費電力が電力の島のそれぞれで独立して制御される複数の電力の島を有する。電力マネージャは、電力の島のうち1つの目的の電力レベルを決定する。電力マネージャは、電力の島のうち1つの消費電力レベルを目的の電力レベルに変更する動作を決定する。電力マネージャは、電力の島のうち1つの消費電力レベルを目的の電力レベルに変更する動作を実行する。

(もっと読む)

自己修正可能な半導体、および自己修正可能な半導体を備えたシステム

【課題】歩留りの向上を実現できる、自己修正可能な半導体を提供する。

【解決手段】自己修正可能な半導体は、同じ機能を実行しかつ副機能ユニットを有する、多数の機能ユニットを備える。半導体は、完全または部分的な1つ以上のスペア機能ユニットを備え、当該スペア機能ユニットは、半導体へと集積される、副機能ユニットの欠陥が検出されると、その副機能ユニットは、切り替えられて、完全または部分的なスペア機能ユニットにおける副機能ユニットと、置き換えられる。この再構成は、副機能ユニットと関連付けられたスイッチング・デバイスによって実現される。欠陥のある機能ユニットや副機能ユニットは、組立後に電源を投入している最中に動作中に周期的に検出されてよく、および/又は手動で検出してもよい。

(もっと読む)

半導体チップ、半導体装置及びLSI設計装置

【課題】チップコストの低下とチップ歩留りの向上とを同時に実現する。

【解決手段】実施形態に係わる半導体チップは、パッド領域11及び方形でないゲート領域12を備える第1のレイアウトL1と、第1のレイアウトL1を180°回転させた第2のレイアウトL2とを備える。第1及び第2のレイアウトL1,L2は、点対称かつ重なり合わずに結合されることによりチップレイアウトを構成する。チップレイアウトは、方形のチップ領域内に配置され、第1及び第2のレイアウトL1,L2は、それぞれ独立に動作するLSIを構成する。

(もっと読む)

フリップチップ半導体ダイのパッドレイアウトを形成する半導体素子および方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】主に半導体ダイの周辺領域中に位置する信号パッドと、主に前記信号パッドから半導体ダイの内部領域中に位置する電力パッドおよび接地パッドとを伴う、ダイパッドレイアウトを有する半導体ダイを提供するステップと、前記信号パッド、電力パッド、および接地パッド上に複数のバンプを形成するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、相互接続部位よりも幅広い、ステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】良好な伝送性能と小さい配置面積を両立可能なデータバスを備える半導体装置を提供する。

【解決手段】本発明の半導体装置は、配線層M1、M2と、複数のデータ入出力端子と、N本のデータ線(DU、DL)を含むデータバスとを備え、N本のデータ線は所定の配線長の長短に応じた2種類のデータ線群を含む。配線層M1、M2にはデータ線(DL、DU)の各々に隣接する複数のシールド線(Sa、Sb、Sc)が配置され、各データ線(DL、DU)は、配線層M1、M2の積層方向で互いに重ならない位置に配置される。このような配線構造により、各データ線(DL、DU)の間のカップリング容量を抑え、データバスのクロストークを防止することができる。

(もっと読む)

可変容量素子、及び液晶表示装置

【課題】制御性が良く、安定して動作する可変容量素子を提供する。消費電力が少なく、表示品位の良い液晶表示装置を提供する。

【解決手段】印加される電界により、n型またはi型となる半導体、もしくは、p型またはi型となる半導体を用いて可変容量素子を構成する。容量素子を構成する第1の電極と第2の電極の間に、誘電体層として絶縁層と上記半導体層の積層を設ける。第1の電極を誘電体層側に設け、第2の電極を半導体層側に設けた時に、第1の電極と半導体層が重畳する面積C1よりも、第1の電極と半導体層と第2の電極が重畳する面積C2の方を小さくなるようにする。動画像表示と静止画像表示で駆動方法を切り替える液晶表示装置に可変容量素子を適用することで、消費電力が少なく、表示品位の良い液晶表示装置を実現できる。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置

【課題】チップ面積を拡大することなく信頼性の高い配線レイアウトを実現する。

【解決手段】信号線S1〜S3と電源線VDD1,VSS1がY方向に延在する下層配線層と、信号線S4〜S6と電源線VDD2,VSS2がX方向に延在する上層配線層と、対応する信号線が重なり合うオーバーラップ領域OL1に設けられたビア導体VE1と、対応する電源線が重なり合うオーバーラップ領域OL2,OL3に設けられたビア導体VE2,VE3とを備える。領域OL1のX方向における幅は、領域OL2,OL3のX方向における幅よりも広く、これにより、領域OL1には複数のビア導体VE1a,VE1bが設けられる。また、電源線VDD1,VSS1は、領域OL1との干渉を避けるようY方向に分断されている。複数の下層配線は、一つのビアを含むミニマムピッチで2つのビアを配置している。

(もっと読む)

半導体装置

【課題】並列駆動構成のI/Oバッファから出力される信号を安定化し、信頼性を向上する。

【解決手段】I/Oセル2は、1つの出力信号を正転信号と反転信号からなる相補信号として出力する相補型I/Oセルからなり、2つのI/Oセル2が並列接続された構成からなる。2つのI/Oセル2の出力部となるインバータ6の出力部は、配線17によってそれぞれ接続されており、2つのI/Oセル2の出力部となるインバータ7の出力部は、配線18によってそれぞれ接続されている。配線17は、I/Oセル2の下辺側に2つのI/Oセル2を横断するように形成され。配線18は、該配線17の上方に形成されており、2つのI/Oセル2を横断するように形成されている。また、配線17の配線長と配線18の配線長は、略同等となるようにレイアウトされている。

(もっと読む)

半導体装置及びその制御方法

【課題】様々な導通状態にある複数の電気ヒューズを有する半導体装置において、複数の電気ヒューズによりプログラミングされた結果を誤判定なく読み出すことのできる半導体装置及び半導体装置の制御方法を提供する。

【解決手段】其々がプログラム状態又は非プログラム状態である複数のヒューズ素子と、複数のヒューズ素子のプログラム状態又は非プログラム状態に対応する判定結果信号FLDa,FLDbを其々出力する複数のヒューズ判定回路92a,92bと、第1のタイミング信号LOAD_ENDを共通に受け、第1のタイミング信号LOAD_ENDに同期して複数の判定結果信号FLDa,FLDbを其々ラッチ及び出力する複数のラッチ回路93a,93bとを備える。

(もっと読む)

半導体パッケージ

【課題】ボンディングワイヤのループインダクタンスを低減した半導体パッケージを提供する。

【解決手段】所定の方向に交互に配置された信号用パッドおよび補助パッドのそれぞれが複数設けられた半導体装置と、信号用ボンドフィンガー、電源電圧用ボンドフィンガーおよび接地電位用ボンドフィンガーのそれぞれが複数設けられたパッケージ基板と、を有する。複数の信号用パッドのそれぞれが複数の信号用ボンドフィンガーのそれぞれと第1のワイヤを介して接続され、複数の電源電圧用ボンドフィンガーおよび複数の接地電位用ボンドフィンガーのそれぞれが複数の補助パッドのそれぞれと第2のワイヤを介して接続されている。第1のワイヤが、電源電圧用ボンドフィンガーに接続された第2のワイヤと接地電位用ボンドフィンガーに接続された第2のワイヤとの間に配置されている。

(もっと読む)

半導体集積回路及びその制御方法

【課題】テストモードにおいて、複数の内部回路のうち所望の内部回路のみを動作させて消費電流測定を行うことが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、電源スイッチ7,8と、電源スイッチ7を介して電源が供給される内部回路4と、電源スイッチ8を介して電源が供給される内部回路5と、電源スイッチ7,8のオンオフを制御する電源制御信号を出力する制御回路2と、を備える。制御回路2は、電源スイッチ7,8のオンオフを制御するための制御信号n2,n3を生成する通常動作モード用電源制御回路21と、電源スイッチ7,8のオンオフを制御するための制御信号t2,t3を生成するテストモード用電源制御回路22と、制御信号n2,n3及び制御信号t2,t3のいずれかを、モードに応じて選択的に電源制御信号p2,p3として出力するセレクタ25,26と、を有する。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】半導体装置に用いられるキャパシタを効率よく、しかも少ない占有床面積で行うことができる半導体装置の製造方法および基板処理装置を提供する。

【解決手段】基板200上に下電極を形成する工程(S104)と、下電極の上に、それぞれ異なる金属元素を含む3種の金属酸化膜を積層して誘電膜を形成する工程(S106、S108、S110)と、誘電膜の上に、上電極を形成する工程(S112)と、を有し、各工程は同一の装置で行う。

(もっと読む)

半導体装置及びその制御方法

【課題】内部電圧生成回路を活性化させる際又は非活性化させる際における内部電圧の急激な変動を防止する。

【解決手段】外部電圧VDDから生成した内部電圧VPPを内部電源配線110aに供給する内部電圧生成回路110と、内部電圧生成回路110の動作を制御する制御回路300と、前記第1の電圧のレベルを検出する電圧検出回路330とを備える。例えば、制御回路300は、内部電圧生成回路110を活性化させる場合、内部電圧VPPの供給能力を第1の速度で段階的に上昇させ、内部電圧生成回路110を非活性化させる場合、内部電圧VPPの供給能力を第1との速度と異なる第2の速度で段階的に下降させる。これにより、内部電圧生成回路110を活性化/非活性化させる際の内部電圧VPPの大幅な変動をそれぞれ最適に防止することが可能となる。

(もっと読む)

半導体装置

【課題】テスト信号を誤動作なく発生するテスト回路を備えた半導体装置を提供する。

【解決手段】動作指定コマンドがテスト動作モードの設定を示すときに、コマンド信号CMD1及びコマンド信号CMD2に応じて、第1のテスト信号(テスト信号DFT1〜DFTn)のうち所定の信号を活性化するコマンドデコーダ106と、動作指定コマンドがテスト動作モードの設定を示すときに第1のテスト信号を受け取り、第2のテスト信号(制御用テスト信号DFTF1〜DFTFn)として並列に出力し、テスト動作モードの設定以外の動作を指定するときに、スキャンチェーン接続され、第1のテスト信号を第3のテスト信号としてスキャン出力端子TSOUTへ直列に出力するレジスタ部107と、テスト動作モードの設定を示すときに、第2のテスト信号に応じてメモリセルアレイの動作を制御する読み出し及び書き込み制御部104と、を備える。

(もっと読む)

半導体装置

【課題】 半導体装置のレイアウト面積を大きくすることなく、内部電源回路の電流供給能力の向上を可能にする。

【解決手段】 半導体装置は、主領域12と、第1の方向に沿って主領域に形成された複数の第1の電源配線15と、第1の電源配線と交差しかつ電気的に接続されるように第2の方向に沿って主領域に形成された複数の第2の電源配線16と、第1の方向に関して主領域の一方の側に隣接する第1の隣接領域13に設けられ、第1の電源配線の一端にそれぞれ接続された第1の内部電源回路17と、第2の方向に関して主領域の一方の側に隣接する第2の隣接領域14に設けられ、複数の第2の電源配線のうち最も第1の電源配線の他端に近い電源配線の一端に接続された第2の内部電源回路18と、を備える。

(もっと読む)

141 - 160 / 1,792

[ Back to top ]