Fターム[5F038EZ09]の内容

Fターム[5F038EZ09]に分類される特許

61 - 80 / 704

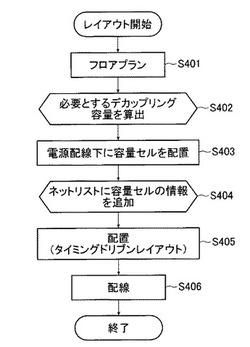

半導体集積回路の設計方法

【課題】設計フローの負荷を増大させることなく、それぞれの回路モジュールに必要十分な容量セルを、それぞれの回路モジュールに近接配置することができる半導体集積回路の設計方法を提供する。

【解決手段】本発明は、それぞれが複数の論理セルを含む複数の回路モジュールからなる半導体集積回路の設計方法であって、複数の回路モジュールのそれぞれの、複数の論理セルおよび複数の論理セルの端子間の接続の情報を記述するネットリストに、複数の論理セルに電源を供給する電源配線間に接続されるセルであり、複数の論理セルのいずれとも独立で、かつ、複数の論理セルの端子と接続される端子を持たない容量セルの記述を追加し、複数の論理セルおよび複数の容量セルのレイアウトデータが格納されたセルライブラリを備えた設計支援システムを利用して、回路モジュールのそれぞれに対応する、複数の論理セルおよび容量セルを配置する配置領域を設定し、複数の論理セルおよび容量セルを対応する配置領域内に配置する工程を含む。

(もっと読む)

半導体集積回路のレイアウト方法及びプログラム

【課題】パワードメインを自動作成する。

【解決手段】設計された回路が仕様を満たしているか否かを評価するための機能シミュレーション処理(9)と、上記機能シミュレーション処理の結果に基づいて、活性化タイミングが所定の範囲内で揃う論理ブロック毎にクラスタ分割することでパワードメインを得るクラスタ分割処理(10)とがコンピュータで行われる。これにより、パワードメインは、コンピュータで行われる処理によって得られるため、人手(設計者の手作業)によって求める場合に比べてパワードメインの最適化を図ることができる。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】LSIのレイアウト設計において、TAT(Turn Around Time)を増加させることなくタイミング収束を実現する。

【解決手段】LSIのレイアウト設計方法は、レイアウト対象の集積回路のネットリストに基づいて、前記集積回路をクロックドメインに分けることでクロックドメイン回路集合体に区分する工程と、前記クロックドメイン回路集合体の各々に対するタイミング制約を作成する工程と、所定の基準に基づいて前記クロックドメイン回路集合体間の配置順序を決定する工程と、前記クロックドメイン回路集合体を前記配置順序に従って配置し配線することにより前記集積回路のレイアウトを作成する工程とを備える。レイアウト設計後のタイミング収束のTATを短縮することが可能となる。

(もっと読む)

半導体集積回路及び半導体集積回路の設計方法

【課題】電位ドロップに起因するセルの動作不良を防止すること。

【解決手段】本発明に係る半導体集積回路は、チップ1上に配置された電源パッド2aと、電源配線構造10を介して電源パッド2aに接続された回路群21,22とを備える。その電源配線構造10は、異なる配線層に形成され複数の交差点IS1,IS2においてオーバーラップする複数の第1電源配線11及び複数の第2電源配線12と、それら複数の第1電源配線11と複数の第2電源配線12を接続するビア13とを有する。上記回路群は、第1領域R1に配置された機能ブロック21を含む。ビア13は、第1領域R1と電源パッド2aの間の第2領域R2における複数の交差点IS2の一部に配置されていない。

(もっと読む)

半導体集積回路のレイアウト設計方法、レイアウト設計装置及びレイアウト設計プログラム

【課題】長さが均一で直線的な配線を配置することができる半導体集積回路のレイアウト設計方法、レイアウト設計装置及びレイアウト設計プログラムを提供すること。

【解決手段】半導体集積回路のレイアウト設計方法は、第1の配線ピッチで配線を行う高速配線処理と、第1の配線ピッチより狭い第2の配線ピッチで配線を行う通常配線処理と、を有する。高速配線処理は、所定の高速バス配線上の複数のネットを第1の配線ピッチで略平行、かつ、略等長となるように自動配線を行う。通常配線処理は、高速配線処理より前に実行されない。

(もっと読む)

半導体集積回路、半導体チップ、及び半導体集積回路の設計手法

【課題】容易な設計により、小規模な構成でクロックスキューを抑制させる半導体集積回路を提供する。

【解決手段】ラッチ回路31〜316のデータ入力端子とデータビットの供給元PDとの間に、クロック信号CLLの供給元PCD及びラッチ回路のクロック入力端子間のクロック信号経路中に含まれている論理素子の個数と同一数だけ当該論理素子を直列に接続してなる第1遅延部51,52と、クロック信号経路中の配線の配線長に対応した配線遅延時間と同一長の遅延時間を有する第2遅延部53と、を備える。

(もっと読む)

スキャンチェーン回路、スキャンチェーン構築方法及び試験装置

【課題】スキャンF/Fの遷移する回数を抑えて消費電力を削減することができるスキャンチェーン回路及びスキャンチェーン構築方法を提供すること

【解決手段】本発明にかかるスキャンチェーン回路は、複数のフリップフロップ21〜26を有し、複数のフリップフロップ21〜26のうち、それぞれのフリップフロップが保持しているデータを先頭方向から後尾方向に対してシフトするスキャンチェーン回路であって、複数のフリップフロップ21〜26は、スキャンチェーン回路の先頭方向から後尾方向に対して、保持しているデータの遷移回数が少ない方から昇順となるように配置されるものである。

(もっと読む)

半導体集積回路のテスト設計支援装置、テスト設計支援方法及びプログラム

【課題】チップ上の機能ブロックを実動作よりも、広範囲かつ同時に動作させても、チップを誤動作させないテストパターンを作成できる半導体集積回路テスト設計支援装置を提供する。

【解決手段】本発明の半導体集積回路テスト設計支援装置は、機能ブロックを単独で動作させて、IRドロップ解析を行うIRドロップ解析部と、チップ上の小領域を示す番地(X,Y)単位に量子化したIRドロップ量Zを算出して、マッピング値(X,Y,Z)を作成するマッピング値作成部と、前記機能ブロックを、複数動作させた場合の前記マッピング値(X,Y,Z)を、同一の前記番地(X,Y)の前記量子化したIRドロップ量Zを加算することによって算出し、同時動作させた場合の各前記番地(X,Y)の前記量子化したIRドロップ量Zが、許容値以内であれば、同時動作可能な機能ブロックとしてグルーピングするグルーピング部とを備える。

(もっと読む)

半導体設計装置および半導体装置

【課題】簡易かつ容易に、非同期データパスを含む半導体装置を設計することができる半導体設計装置、および、非同期データパスを含む半導体装置を提供する。

【解決手段】FF挿入部9は、非同期データパスにフリップフロップ(FF1)を挿入する。遅延設定部8は、非同期データパスの受信側のFF(FF2)においてメタステーブル収束時間Trがクロックツリー(CT)のレイテンシTclよりも短いときには、CTのあるノードから出力される第1のクロックをFF1の入力クロックに設定し、CTの別のノードから出力され、かつ第1のクロックよりもTrだけ遅延した第2のクロックをFF2の入力クロックに設定する。遅延設定部8は、TrがTcl以上のときには、第1のクロックをFF1の入力クロックに設定し、第1のクロックをTrだけ遅延回路で遅延させた第2のクロックをFF2の入力クロックに設定する。

(もっと読む)

半導体装置

【課題】テストパターンの内容、あるいは回路規模によらず、動作試験が短時間且つ高効率で行える半導体装置の実現。

【解決手段】フリップフロップ回路37と、試験モード時に、フリップフロップ回路に所定の値を設定すると共にフリップフロップ回路の保持する値を読み出すスキャンチェーンと、通常モード時に非動作で、試験モード時には、フリップフロップ回路の値が変化する場合に動作状態となり、前記フリップフロップ回路の値が変化するタイミングで非動作状態になる電流消費回路37A,37Bと、を有する半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率の絶縁膜を有するnチャネル型トランジスタやpチャネル型トランジスタを有する半導体装置の製造方法において、nチャネル型トランジスタのゲート絶縁膜の側面への異物の付着を抑制する。

【解決手段】半導体基板の主表面上の、p型不純物領域PWLに機能用nチャネル型トランジスタが、n型不純物領域NWLに機能用pチャネル型トランジスタが形成される。p型不純物領域PWLの、平面視における機能用nチャネル型トランジスタ以外の領域に形成される複数の第1の周辺用トランジスタは、周辺用n型ゲート構造体と周辺用p型ゲート構造体とが混在するように形成される。

(もっと読む)

半導体集積回路、スキャンテスト回路設計方法

【課題】スキャンテスト時間を短縮する半導体集積回路のスキャンテスト回路、スキャンテスト回路設計方法を提供する。

【解決手段】スキャンフリップフロップを示すセル間を接続するシフトパスを生成するステップと、信号伝達の制約条件を満たすようにリピータセルをシフトパスに挿入するステップと、スキャンフリップフロップを示すセル及びリピータセルの間のセル間遅延時間を求めるステップと、リピータセルをフリップフロップを示すセルに置換してシフトパスを分割したときのシフトパスの遅延時間を示すシフトパス遅延時間を算出するステップと、シフトパスを分割したときの、スキャンチェーンにテストデータをシフトさせて供給するスキャンシフト時間を算出するステップと、スキャンシフト時間が最短になるシフトパスの分割位置を求めるステップと、シフトパスの分割位置のリピータセルをフリップフロップを示すセルに置換した回路データを生成するステップとを具備する。

(もっと読む)

半導体集積回路装置

【課題】メーカーの設計負担を増加させることなくセルタイプの異なるICを実現することができるとともに、チップサイズおよび消費電力並びに動作速度が最適化された半導体集積回路を容易に実現可能な設計技術を提供する。

【解決手段】所望の機能を有する回路セルの設計情報を目的別にオブジェクトとして記述し、所定のオブジェクトの情報の削除もしくは追加のみで基体電位固定型セルと基体電位可変型セルのいずれをも構成可能なセル情報として、セルライブラリに登録するようにした。

(もっと読む)

半導体装置

【課題】裏面FIB加工における場所特定を容易にする。

【解決手段】半導体装置は、第1方向および前記第1方向に直交する第2方向の平面内に広がる第1導電型の半導体基板60の表面上に形成された回路部65と、前記半導体基板内の表面側に形成され、前記回路部を構成し、素子として機能する、前記第1導電型と異なる第2導電型の複数のウェル61と、前記半導体基板内の表面側に形成され、前記回路部を構成せず、素子として機能しない、前記第2導電型の複数のダミーウェル62と、を具備する。

(もっと読む)

半導体集積回路のレイアウト設計装置、半導体集積回路のレイアウト設計方法及びプログラム

【課題】信号の遅延調整を柔軟に行なうことができる半導体集積回路レイアウト設計装置を提供する。

【解決手段】図1に示す半導体集積回路レイアウト設計装置は、配線部と遅延調整部を備える。配線部では、第1の配線層の配線上に、第2の配線層では接続先となる配線がないビア(未接続ビア)を形成する。その後、遅延調整部において、遅延時間の調整が必要であれば、未接続ビアから、遅延調整に適したビアを選択し、第1の配線上のビア間の配線を削除する。その後、第2の配線層において第1のビアと第2のビアを配線する。その結果、信号配線の抵抗は、ビアの持つ抵抗値の分上昇し、遅延時間の調整を行なうことができる。

(もっと読む)

半導体チップ、半導体装置及びLSI設計装置

【課題】チップコストの低下とチップ歩留りの向上とを同時に実現する。

【解決手段】実施形態に係わる半導体チップは、パッド領域11及び方形でないゲート領域12を備える第1のレイアウトL1と、第1のレイアウトL1を180°回転させた第2のレイアウトL2とを備える。第1及び第2のレイアウトL1,L2は、点対称かつ重なり合わずに結合されることによりチップレイアウトを構成する。チップレイアウトは、方形のチップ領域内に配置され、第1及び第2のレイアウトL1,L2は、それぞれ独立に動作するLSIを構成する。

(もっと読む)

半導体装置

【課題】チップ面積を拡大することなく信頼性の高い配線レイアウトを実現する。

【解決手段】信号線S1〜S3と電源線VDD1,VSS1がY方向に延在する下層配線層と、信号線S4〜S6と電源線VDD2,VSS2がX方向に延在する上層配線層と、対応する信号線が重なり合うオーバーラップ領域OL1に設けられたビア導体VE1と、対応する電源線が重なり合うオーバーラップ領域OL2,OL3に設けられたビア導体VE2,VE3とを備える。領域OL1のX方向における幅は、領域OL2,OL3のX方向における幅よりも広く、これにより、領域OL1には複数のビア導体VE1a,VE1bが設けられる。また、電源線VDD1,VSS1は、領域OL1との干渉を避けるようY方向に分断されている。複数の下層配線は、一つのビアを含むミニマムピッチで2つのビアを配置している。

(もっと読む)

絶縁破壊寿命シミュレーション方法及びシリコンウェーハ表面の品質評価方法

【課題】実際のデバイスの絶縁破壊寿命に適合する精度の良いシミュレーションを行って、正確な絶縁膜の絶縁破壊寿命を求めることで、実測データとの対比で欠陥種、欠陥の大きさ等を正確に解析できる絶縁破壊寿命シミュレーション方法及びシリコンウェーハ表面の品質評価方法を提供することを目的とする。

【解決手段】前記シミュレーションする構造における、前記シリコンウェーハと前記絶縁膜の界面及び前記絶縁膜と前記金属電極の界面に、及び/又は、前記絶縁膜中に予め欠陥を組み込み、該欠陥を組み込んだ構造において、前記絶縁膜中に欠陥を乱数にて発生させて前記絶縁膜の絶縁破壊寿命を求める絶縁破壊寿命シミュレーション方法。

(もっと読む)

スキャンテスト回路、テスト回路生成方法およびテストパタン生成方法

【課題】異なるクロックドメインに属する回路間でデータの授受がある回路において、半導体集積回路のスキャンパスを用いてクロストークの影響を考慮した遅延試験を行うことができる。

【解決手段】第1回路群は、第1のクロックドメインに属する複数のスキャンフリップフロップ(F12、F14)を備え、信号の伝達遅延を測定する第1データパス(102)を含む。第2回路群は、第2のクロックドメインに属する複数のスキャンフリップフロップ(F11、F13、F15)を備え、第1データパス(102)に対してクロストークにより影響を与える第2データパス(101)を含む。第3データパスは、第1回路群・第2回路群間でデータを授受する。クロック切り換え回路(M10)は、制御信号に応答して、第2回路群に供給される第2クロック信号(CK2)を、第1回路群に供給される第1クロック信号(CK1)に替えて第2回路群に供給する。

(もっと読む)

半導体集積回路

【課題】外部電源電圧を降圧するレギュレータを内蔵することによるチップ面積の増大を抑え且つ降圧電圧の安定化を実現できる半導体集積回路を提供する。

【解決手段】外部電源電圧(Vext)よりも低い内部電源電圧(Vint)で動作する内部回路を持つ半導体集積回路において、内部電源電圧を生成するレギュレータ(150〜157)を、バッファ及び保護素子を配置するための第2の領域(2)に配置することにより、降圧電源回路のオンチップ化による面積オーバヘッドを低減する。降圧電圧を伝達するループ状の電源幹線(L20)を用い、電源幹線に外付け安定化容量を接続するための電極パッドを設ける等により、低消費電力を更に促進する。

(もっと読む)

61 - 80 / 704

[ Back to top ]