Fターム[5F038EZ16]の内容

Fターム[5F038EZ16]に分類される特許

61 - 80 / 340

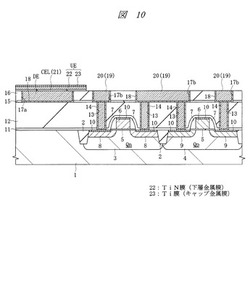

半導体装置

【課題】MIM構造の容量素子を有する半導体装置において、容量素子の信頼性を向上させることのできる技術を提供する。

【解決手段】下部電極DEと、容量絶縁膜CELと、上部電極UEとからなる容量素子において、下部電極DEを、半導体基板1の主面上の絶縁膜に形成された電極溝17aの内部に埋め込まれた金属膜によって構成し、上部電極UEを、TiN膜(下層金属膜)22と、TiN膜(下層金属膜)22上に形成されたTi膜(キャップ金属膜)23との積層膜によって構成する。

(もっと読む)

トランス素子とその製造方法

【課題】マイクロトランス素子を小型化することと、マイクロトランス素子の特性を確保することとを両立する。

【解決手段】 トランス素子は、第1導電型の半導体層を備えた半導体基板と、第1導電型の半導体層の表面側に設けられた第2導電型の半導体層からなる半導体層コイルと、半導体層コイルと並列に接続されており、半導体層コイルのコイル配線間の第1導電型の半導体層に形成されたトレンチと、トレンチ内面に設けられたトレンチ絶縁膜と、そのトレンチ絶縁膜によって被覆されている導電層有するトレンチコイルと、第1導電型の半導体層の表面側に設けられ、半導体層コイルおよびトレンチコイルを被覆するコイル絶縁層と、コイル絶縁層の表面に設けられており、半導体層コイルおよびトレンチコイルと対向している金属層コイルとを備えている。並列接続された半導体層コイルとトレンチコイルによって、第1コイルの抵抗が低減し、トランス素子の小型化と特性確保を両立できる。

(もっと読む)

半導体装置、半導体装置の製造方法および半導体装置の判別方法

【課題】装置に固有な所望の情報を、新たな製造工程を増やさず容易に記録することができる半導体装置を提供する。

【解決手段】第1面に複数の第1電極端子11を備える第1装置10と、第1面と向かい合う第2面に、複数の第2電極端子21を備える第2装置20と、複数の第1電極端子11と複数の第2電極端子21との間に配置され、情報を記録する記録部30とを具備する。記録部30は、複数の第1電極端子11に含まれる第3電極端子11aと、複数の第2電極端子21に含まれる第4電極端子21aとを電気的に接続する導通部31と、複数の第1電極端子11に含まれる第5電極端子11bと、複数の第2電極端子21に含まれる第6電極端子21bとに接触し、第5電極端子11bと第6電極端子21bとの電気的な接続を阻害する高抵抗部32とを備える。

(もっと読む)

半導体装置

【課題】絶縁層上の半導体層に形成された部分空乏型のトランジスターにおいて、高いON/OFF比と、安定動作を同時に実現できるようにした半導体装置を提供する。

【解決手段】絶縁層上の半導体層に形成された部分空乏型の第1トランジスターと、前記半導体層に形成された第2トランジスターと、前記半導体層に形成された第3トランジスターと、を備え、前記第1トランジスターは、第1導電型の第1ソース又は第1ドレインを有し、前記第2トランジスターは、第1導電型の第2ソース又は第2ドレインを有し、前記第3トランジスターは、第2導電型の第3ソース又は第3ドレインを有し、前記第1ソース又は第1ドレインの一方と、前記第2ソース又は第2ドレインの一方とが電気的に接続され、前記第2ソース又は第2ドレインの他方と、前記第1トランジスターのボディ領域と、前記第3ソース又は第3ドレインの一方とが互いに電気的に接続されている。

(もっと読む)

半導体装置の製造方法及び半導体装置並びにその半導体装置を内蔵する多層基板

【課題】dv/dtサージにより、寄生容量を充放電する変位電流の発生を抑制できる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】低電位基準回路部LV、高電位基準回路部HV、レベルシフト回路部LSを形成したSOI基板の半導体層の主面上にサポート部材を貼り付け、支持基板を除去する。次いで、回路部と対向するように絶縁部材を半導体層の裏面上に固定した後、サポート部材を剥がす工程と、チップ内にLV,HV,LSが含まれるように絶縁部材の固定された半導体層をダイシングする工程を経る。そして、サポート部材を剥がし、チップ化した半導体層を、絶縁部材を挟んで、第1のリードがLVと、第2のリードがHVと対向するように、第1リード及び第2リード上に固定するとともに、第1のリードとLVにおける第1の電位が印加される部位を電気的に接続し、第2のリードとHVにおける第2の電位が印加される部位を電気的に接続する。

(もっと読む)

半導体装置及びその設計方法並びに半導体装置の製造方法

【課題】良好な電気的特性を有する半導体装置及びその設計方法並びに半導体装置の製造方法を提供する。

【解決手段】第1のトランジスタが形成される第1の活性領域のパターンと、第2のトランジスタが形成される第2の活性領域のパターンとを配置するステップS2と、第1の活性領域及び第2の活性領域と交差するゲート配線のパターンを配置するステップS3と、第1の活性領域とゲート配線とが重なり合う領域である第1の領域を抽出するステップS4と、第1の活性領域を含む領域上に、圧縮応力膜のパターンを配置するステップS5とを有し、第2の活性領域を含む領域上に、圧縮応力膜に隣接する引っ張り応力膜のパターンを配置するステップS6とをコンピュータに実行させることにより、半導体装置のレイアウトパターンを取得する工程を有し、圧縮応力膜のパターンを配置するステップでは、第1の領域の縁部の位置に基づいて、圧縮応力膜のパターンの縁部の位置が設定される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バンドギャップが狭い高誘電率膜を用いたキャパシタにおいて、リーク電流を低減するとともに、製造コストを削減することができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】ウエハ2上に形成された下部電極としてのTiN膜100と、TiN膜100上に形成された第1の高誘電率絶縁膜としてのHfO2膜110と、HfO2膜110上に形成され、HfO2膜110のバンドギャップよりも狭いバンドギャップを有する第2の高誘電率絶縁膜としてのTiO2膜120と、TiO2膜120上に形成され、非貴金属であって4.8eVよりも高い仕事関数を有する上部電極膜としてのCo膜130と、により構成されている。

(もっと読む)

抵抗素子を有する半導体装置及びその製造方法

【課題】基準電圧を調整する回路を構成する抵抗素子を有するフラッシュ記憶素子である半導体装置及びその製造方法を提供する。

【解決手段】フラッシュ記憶素子である半導体装置の製造方法は、半導体基板上にトレンチを定義する鋳型パターンMLDPを形成し、鋳型パターンMLDP上にトレンチを横切る抵抗パターンRPを形成し、抵抗パターンRP上に互いに離隔された第1及び第2導電パターン210、220を形成し、第1及び第2導電パターン210、220に各々接続する第1及び第2配線UL1,UL2を形成する段階を有し、第1及び第2導電パターンUL1,UL2は鋳型パターンMLDPの上部に各々形成される。

(もっと読む)

半導体装置の製造方法

【課題】外部から印加される電源電圧の仕様に対応した、半導体装置の製造方法を提供する。

【解決手段】チャネルイオン注入工程、ゲート酸化膜形成工程、および、ゲート電極パターニング工程の少なくとも1つの工程を、外部から第1の電源電圧が供給されて動作する第1の半導体装置を製造する場合には第1の電源電圧で動作する素子を形成する工程で行い、外部から第2の電源電圧が供給されて動作する第2の半導体装置を製造する場合には第2の電源電圧で動作する素子を形成する工程で行い、また、第1の半導体装置の製造の場合と第2の半導体装置の製造の場合とで少なくとも拡散領域形成工程を共通に行うものである。

(もっと読む)

半導体装置

【課題】レーザートリミングによって除去される金属配線を有した半導体装置において、金属配線の下層の素子分離領域においてクラックの発生を抑止する。

【解決手段】例えばP型の半導体基板10には、N−型の半導体層11と隣接するP+型の素子分離領域12と、それを覆うLOCOS絶縁膜13が形成されている。これらは第1の層間絶縁膜21に覆われている。第1の層間絶縁膜21上には、ヒューズ配線として、並行して延びる金属配線23A,23B,23Cが形成されている。第1の層間絶縁膜21の貫通孔21TH内には、タングステン等からなる高融点金属層22が形成されている。この高融点金属層22は、レーザートリミングの際に生じる余分な熱を吸収するため、第1の層間絶縁膜21にクラックが生じにくくなる。

(もっと読む)

半導体装置

【課題】レーザートリミングによって除去されるポリシリコン層を有した半導体装置において、ポリシリコン層を覆う層間絶縁膜の開口部の広がりを抑止する。

【解決手段】例えばP型の半導体基板10には、N−型の半導体層11と隣接するP+型の素子分離領域12が形成されている。素子分離領域12を覆うLOCOS絶縁膜13上には、ヒューズ配線として複数のポリシリコン層15A,15B,15Cが形成されている。これらのヒューズ配線は層間絶縁膜16に覆われており、層間絶縁膜16に設けられた貫通孔16THには、タングステン等からなる高融点金属層17が形成されている。この高融点金属層17は、レーザートリミングの際に生じる余分な熱を吸収するため、層間絶縁膜16の開口部16Aの広がりを抑えることができる。

(もっと読む)

電子装置とその製造方法

【課題】

電子装置とその製造方法を提供する。

【解決手段】

電子装置は、ガラス基板と、少なくとも一つの開口を有し、ガラス基板上に設置されるパターン化半導体基板と、第一導電層と第二導電層を有し、第一導電層が、パターン化半導体基板とガラス基板間に設置される少なくとも一つの受動素子と、からなる。

(もっと読む)

電子デバイスおよびその製造方法

【課題】抵抗値を精度よく容易に設定可能な構造の抵抗素子を有する電子デバイスを実現する。

【解決手段】半導体等の基板に形成された積層構造における絶縁層間の導電膜配置階層の1つに、抵抗素子の抵抗値を規定する抵抗膜(金属薄膜11)が配置されている。この金属薄膜11は、2種類以上の抵抗率をもつ。この金属薄膜11は、望ましくは、抵抗率が異なる複数の面領域(高抵抗面領域RHと低抵抗面領域RL1,RL2)をもつ複抵抗領域型の金属薄膜11Wである。

(もっと読む)

半導体装置

【課題】ヒューズ用開口部からガードリング外への水分等の伝達をより強固に防止する。

【解決手段】下地絶縁膜3上に第1シリコン膜パターンからなるシリコンヒューズとシリコン配線パターン7が形成されている。第1シリコン膜パターンとは別途形成された第2シリコン膜パターンからなり、上方から見てヒューズ5の周囲を取り囲み、一部分がシリコン配線パターン7上を跨いで下地絶縁膜上に環状に形成されたシリコンガードリング11が形成されている。シリコンガードリング11と交差している部分のシリコン配線パターン7表面にシリコン表面絶縁膜9が形成されている。シリコン配線パターン7とシリコンガードリング11はシリコン表面絶縁膜9により互いに絶縁されている。シリコンガードリング11上に金属材料からなる環状のガードリング17,19,25,27が上方から見てヒューズ5の周囲を取り囲んで形成されている。

(もっと読む)

誘電体膜、誘電体膜を用いた半導体装置の製造方法及び半導体製造装置

【課題】高誘電率を有する誘電体膜の製造方法を提供する。

【解決手段】薄いシリコン酸化膜を形成したSi基板上に、HfN/Hf積層膜を形成し、アニール処理によりHf、Si、O、Nの混合物からなる金属酸窒化物とする誘電体膜の製造する。(1)EOTの低減が可能であり、(2)リーク電流がJg=1.0E−1A/cm2以下に低減され、(3)固定電荷の発生によるヒステリシスが抑制され、(4)700℃以上の熱処理を行ってもEOTの増加が無く耐熱性に優れる。

(もっと読む)

電子素子及び電子素子の製造方法

【課題】簡易な構成でリーク電流の抑制された電子素子及びその製造方法を提供する。

【解決手段】基板上に設けられ、Mo−Nb合金から構成された第1の電極と、前記第1の電極上に配置された絶縁膜と、前記第1の電極に対して少なくとも前記絶縁膜を介して配置された第2の電極と、を備えた電子素子とする。

(もっと読む)

半導体装置の製造方法

【課題】金属薄膜抵抗体を備えた半導体装置において、金属薄膜抵抗体の抵抗値及び配線パターンとの接触抵抗の安定化を実現する。

【解決手段】下地絶縁膜5上に、金属薄膜抵抗体23の両端部の形成予定領域に対応して配線パターン11を形成する。配線パターン11上を含む下地絶縁膜5上に平坦化された絶縁膜19を形成する。平坦化された絶縁膜19に、金属薄膜抵抗体23の両端部の形成予定領域及び配線パターン11に対応して接続孔21を形成する。接続孔21内を含み絶縁膜19に対してArスパッタエッチング技術によりエッチング処理を施して、接続孔21の内壁にサイドウォール22を形成するとともに、接続孔21の上端部21aをテーパー形状にする。接続孔21内及び絶縁膜19上に金属薄膜抵抗体23を形成するための金属薄膜を形成する。接続孔21にも金属薄膜を残存させるように金属薄膜をパターニングして金属薄膜抵抗体23を形成する。

(もっと読む)

半導体装置

【課題】半導体素子の温度を迅速に、且つ感度よく検出できる温度検出用ダイオードを備えた半導体装置を提供することである。

【解決手段】本発明にかかる半導体装置は、半導体層1aに形成された半導体素子と、半導体層1aが有する凹部11に絶縁膜5aを介して形成された温度検出用のダイオード7と、を備える。半導体素子は、半導体素子の表面に設けられ、且つ半導体素子の出力を取り出す出力パッドSPを有し、ダイオード7は、半導体素子の平面視において、出力パッドSPの周囲に配置されている。

(もっと読む)

半導体装置の製造方法

【課題】被保護素子部、保護素子部及び周辺トランジスタ部を備える半導体装置において、周辺トランジスタ部のゲート絶縁膜と該ゲート絶縁膜よりも膜厚が薄い保護素子部の界面絶縁膜とを同一の工程において形成できるようにする。

【解決手段】半導体基板1の上に、被保護素子用ゲート絶縁膜2を形成し、保護素子部に形成された被保護素子用ゲート絶縁膜2の一部を除去して、開口部14を形成し、半導体基板1の上部に開口部14を通して不純物を注入して、保護素子部にダイオードを形成し、ダイオードの上部に酸化抑制材を注入して、酸化抑制層9を形成し、半導体基板1における周辺トランジスタ部の少なくとも一部とを露出し、露出した半導体基板1の上にゲート絶縁膜11を形成すると共に、酸化抑制層9の上に界面絶縁膜12を形成し、被保護素子用ゲート絶縁膜2、ゲート絶縁膜11及び界面絶縁膜12の上にゲート電極13を形成する。

(もっと読む)

不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置

【課題】高速動作が可能で、しかも可逆的に安定した書き換え特性を有し、半導体製造プロセスと親和性の高い不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置の提供を目的とする。

【解決手段】第1電極103と、第2電極105と、第1電極103と第2電極104との間に介在させ、両電極103,105間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層104とを備えている。この抵抗変化層104は少なくともハフニウム酸化物を含み、当該ハフニウム酸化物をHfOxと表した場合に、0.9<x<1.6を満足するように抵抗変化層104が構成されている。

(もっと読む)

61 - 80 / 340

[ Back to top ]