Fターム[5F038EZ16]の内容

Fターム[5F038EZ16]に分類される特許

21 - 40 / 340

半導体装置及び半導体装置の製造方法

【課題】素子分離領域での電流リークを低減する。

【解決手段】抵抗素子5用の多結晶シリコン膜50の第2領域52にはドーパントがイオン注入されている。抵抗素子6用の多結晶シリコン膜60の第2領域62には窒素等がイオン注入されている。第2領域52,62は第1領域51,61よりも結晶欠陥密度が高い。抵抗素子7用の多結晶シリコン膜70中の結晶欠陥密度はシリサイド膜73付近においてより高い。抵抗素子8用の多結晶シリコン膜80は素子分離絶縁膜3の開口内のシリサイド膜を介して基板2に接している。当該シリサイド膜付近の基板表面2S内の結晶欠陥密度は周辺よりも高い。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗素子について、レイアウト面積の増大を防ぎつつ、周辺の電荷の影響を受けずに安定した抵抗値を得ることができ、しかも、抵抗体に印加できる電位の極性に制限のない半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1上のLOCOS酸化膜3上に形成された抵抗素子10と、を備え、抵抗素子10は、LOCOS酸化膜3上に形成されたシールド用ポリシリコン膜11と、シールド用ポリシリコン膜11上に形成されたシリコン酸化膜13と、シリコン酸化膜13上に形成されたポリシリコン抵抗体15と、ポリシリコン抵抗体15の一方の端部に接合された第1の電極21と、ポリシリコン抵抗体15の他方の端部に接合された第2の電極22と、シールド用ポリシリコン膜11に接合された第3の電極23と、を有し、第1の電極21及び第2の電極22うちの一方が、配線25を介して第3の電極23と電気的に接続されている。

(もっと読む)

半導体装置

【課題】正確にメインセルに流れる電流を検出することができると共に、電流検出の直線性を向上させられ、高い電圧が用いられる場合でもその影響を受け難い半導体装置を提供する。

【解決手段】センスセルの両側にメインセルを配置し、センスセルのエミッタがメインセルのエミッタに挟まれた構造にする。これにより、センスセルのエミッタに流れる電流密度とセンスセルのエミッタに流れる電流密度とを近づけることができ、ミラー比がメインセルとセンスセルそれぞれのエミッタの長手方向における長さの比に近くなる。また、センスセルのエミッタに流れる電流密度とセンスセルのエミッタに流れる電流密度とを近づけられるため、スイッチング時や大電流が流れる時に流れる単位面積当たりの電流量がメインセル側と比較してセンスセル側において大きくなることを抑制できる。このため、電流の偏りを抑制することができ、破壊耐量を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタとESD保護素子とを有する半導体装置において、製造工程が簡単であるとともに、所望の特性を確保しつつ従来に比べてより一層の高密度化が可能な半導体装置及びその製造方法を提供する。

【解決手段】LDMOSトランジスタ形成領域のゲート電極18aと素子分離膜11bの重なり幅をA1、ゲート電極18aとドレイン領域23bとの間隔をB1とし、ESD保護素子形成領域のゲート電極18と素子分離膜11cとの重なり幅をA2、ゲート電極18bとアノード領域22cとの間隔をB2としたときに、A1≧A2、且つB1<B2の関係を満足するように、ゲート電極18a、素子分離膜11b、ドレイン領域20a、ゲート電極18b、素子分離膜11c及び前記アノード領域22cを形成する

(もっと読む)

半導体装置およびその製造方法

【課題】ダミーアクティブ領域の配置に伴うチップ面積の増大を引き起こすことなく、半導体基板の表面の平坦性を向上させる。

【解決手段】ダミーアクティブ領域であるn型埋込み層3の上部には、厚い膜厚を有する高耐圧MISFETのゲート絶縁膜7が形成されており、このゲート絶縁膜7の上部には、内部回路の抵抗素子IRが形成されている。n型埋込み層3と抵抗素子IRとの間に厚いゲート絶縁膜7を介在させることにより、基板1(n型埋込み層3)と抵抗素子IRとの間に形成されるカップリング容量が低減される構造になっている。

(もっと読む)

保護素子及び保護素子を備えた半導体装置

【課題】比較的小さい面積で形成することができ、かつ、素子サイズの微小化が進んでも保護素子として動作させることを可能にする、保護素子を提供する。

【解決手段】半導体基板1に形成された、第1導電型のウェル領域3と、この第1導電型のウェル領域3に隣接して形成された、第2導電型のウェル領域4と、第1導電型のウェル領域3に形成された、第2導電型チャネルのMOSトランジスタと、第1導電型のウェル領域3とMOSトランジスタのソース領域とMOSトランジスタのゲートとに電気的に接続された第1の配線と、MOSトランジスタのドレイン領域と第2導電型のウェル領域4とに電気的に接続された第2の配線とを含む保護素子を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】実用上限温度をより向上させた炭化珪素半導体装置の製造方法を提供する。

【解決手段】ゲート窓6が形成された炭化珪素基板1の表面に、前駆酸化シリコン膜を成膜する工程と、前駆酸化シリコン膜を酸化窒素ガス雰囲気で熱処理して第1の酸化シリコン膜(O)とする工程と、窒化シリコン膜(N)を積層する工程と、窒化シリコン膜を酸化させて、表面から所定の深さまで第2の酸化シリコン膜(O)を形成して、ONO絶縁膜を形成する工程と、ONO絶縁膜の上にゲート電極を形成する工程とを備える。ゲート電極を形成する工程は、ONO絶縁膜の上に多結晶シリコン膜を成膜する工程と、所望のマスクを用いて、多結晶シリコン膜、第2の酸化シリコン膜、窒化シリコン膜、を連続的にエッチングして、ゲート電極と第2の酸化シリコン膜と窒化シリコン膜の外縁を定義する工程と、ゲート電極の側面及び上部と窒化シリコン膜の外縁を酸化する工程を備える。

(もっと読む)

半導体装置製造工程におけるチャージアップ検出方法

【課題】絶縁ゲート型電界効果トランジスタを製造する途中で、絶縁ゲート型電界効果トランジスタに悪影響を与えるチャージアップが生じているのを検出することができる半導体装置製造工程におけるチャージアップ検出方法を提供する。

【解決手段】絶縁体10上の半導体層12に、素子分離領域18によって素子分離された絶縁ゲート型電界効果トランジスタ用の第1の活性層16と検出素子用の第2の活性層16とを形成し、前記第1の活性層と第2の活性層上に第1および第2の絶縁膜22をそれぞれ形成し、少なくとも第1および第2の絶縁膜22上に第1および第2の導体24をそれぞれ形成し、第1および第2の導体24に電荷が供給される処理を行い、その後、第2の活性層16の形状を検出する。

(もっと読む)

半導体装置

【課題】半導体装置に損傷を与えることなく、単体の抵抗素子自体の抵抗値を精度良く微調整する。

【解決手段】P型の半導体基板10上にN型の半導体層11が形成されている。半導体層11の表面には薄い第2の絶縁膜13が形成され、第1の絶縁膜12及び第2の絶縁膜13上にフローティングポリシリコン層14が形成されている。フローティングポリシリコン層14は第3の絶縁膜15に覆われている。第3の絶縁膜15によって覆われたフローティングポリシリコン層14上にはポリシリコン抵抗層16が形成されている。そして、半導体層11とポリシリコン抵抗層16との間に電圧を印加することにより、第2の絶縁膜13を通してフローティングポリシリコン層14の中に電子が注入され、ポリシリコン抵抗層16の中に正孔蓄積層16Aが形成される。

(もっと読む)

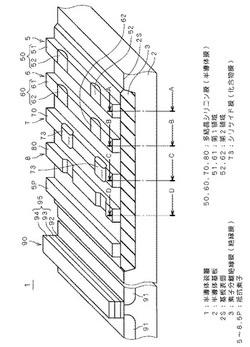

半導体装置

【課題】高出力の高周波信号の影響を抑制することが可能な半導体装置を提供する。

【解決手段】半導体装置は、電子回路が設けられた主面を有する半導体基板10と、前記主面の上に絶縁膜2,3,4を介して設けられたパッシブ回路30と、を備える。そして、前記半導体基板と前記パッシブ回路との間に前記パッシブ回路から絶縁されて設けられ、前記主面に平行な少なくとも1方向に流れる電流を遮断する間隙45を有した第1の導体層40と、前記第1の導体層と前記パッシブ回路との間に、前記第1の導体層および前記パッシブ回路から絶縁されて設けられ、前記主面に平行な少なくとも1方向に流れる電流を遮断する間隙55を有し、前記パッシブ回路から見た前記第1の導体層の間隙を覆う第2の導体層50と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】下部電極、上部電極およびそれらの間の絶縁膜により構成される容量素子の下部電極および上部電極間の耐圧を向上させる。

【解決手段】上部電極TEならびに上部電極TEのそれぞれの側壁の側壁酸化膜9およびサイドウォール10と下部電極BEとの間にONO膜IFを連続的に形成し、また、上部電極TEの側壁に、側壁酸化膜9を介して真性半導体膜からなるサイドウォール10を形成することにより、下部電極BEおよび上部電極TE間にリーク電流が発生することを防ぐ。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ヒューズ層を覆う絶縁膜の膜厚を精度良く調整する。

【解決手段】半導体基板10上の第2の層間絶縁膜17上にヒューズ層18Tが形成され、ヒューズ層18Tは第3の層間絶縁膜20で覆われる。第3の層間絶縁膜20上には、キャップメタル24に覆われたパッド電極23が形成され、それらは第1及び第2のパッシベーション膜25,26に覆われる。次に、ヒューズ層18T上で開口する第1のレジスト層27をマスクとして、ヒューズ層18T上で第2のパッシベーション膜26から第3の絶縁膜の厚さ方向の途中までをエッチングする。その後、パッド電極23上で開口する第2のレジスト層30をマスクとして、パッド電極23上で第1及び第2のパッシベーション膜25,26及びキャップメタル層24をエッチングしてパッド電極23の表面を露出する。その後、保護膜32を形成する。

(もっと読む)

半導体装置

【課題】トレンチゲート型パワーMOSFETのゲート電極の微細化に伴って、トレンチ底部の曲率が大きくなり、その部分に電界が集中し、ゲート酸化膜(絶縁膜)の劣化が起きる。このゲート絶縁膜の劣化は、Nチャネル型パワーMOSFETの場合、ゲート側バイアスが負である場合に起こりやすく、Pチャネル型パワーMOSFETの場合、ゲート側バイアスが正である場合に起こりやすい。

【解決手段】本願発明は、絶縁ゲート型パワー系トランジスタ等をチップ内に具備する半導体装置であって、ゲート保護素子は双方向ツェナーダイオードを具備し、前記双方向ツェナーダイオードは、そのゲート側がマイナスバイアスされたときの耐圧と、そのゲート側がプラスバイアスされたときの耐圧とは相互に異なるように、複数の濃度の異なるP型不純物領域(またはP型不純物領域)を有する。

(もっと読む)

半導体装置及びその検査方法並びにその設計方法

【課題】不良箇所を容易に特定し得る半導体装置及びその形成方法並びにその設計方法を提供する。

【解決手段】配線パターン32aと、ダミーパターン32bと、一方の端部が配線パターンに電気的に接続され、他方の端部がダミーパターンに電気的に接続されたヒューズ32cとを有している。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の小型化を図ること。

【解決手段】第1の領域IにフラッシュメモリセルFLを形成する工程と、第2の領域IIにキャパシタQの第1の電極11aを形成する工程と、第2の絶縁膜14として第1の酸化シリコン膜14a、窒化シリコン膜14b、及び第2の酸化シリコン膜14cをこの順に形成する工程と、第1の電極11aの一部領域CRにおける窒化シリコン膜14bと第2の酸化シリコン膜14cとを除去する工程と、第3の領域IIIHにおける第1の絶縁膜10と第2の絶縁膜14とをウエットエッチングする工程と、キャパシタQの第2の電極30aを形成する工程と、一部領域CRにおける第1の酸化シリコン膜14aをエッチングして除去する工程とを有する半導体装置の製造方法による。

(もっと読む)

MEMS装置

【課題】基板とMEMS素子との間の寄生容量、および基板の反りを抑えたMEMS装置を提供する。

【解決手段】

実施の形態のMEMS装置は、表面に開口する凹部と凹部内に、絶縁物、エアギャップ、または絶縁物およびエアギャップが形成された基板と、基板上の絶縁層と、絶縁層上に形成された信号線を有するMEMS素子とを有し、上記基板の表面に平行な方向の信号線の位置と上記平行な方向の凹部の位置に重なりがある。

(もっと読む)

容量素子の製造方法

【課題】基板上に耐圧が異なる容量素子を共通の工程で形成する際に、基板上に残渣を残さないようにする。

【解決手段】基板10の上に半導体不純物がドープされた第1ポリシリコン層40を形成し、第1ポリシリコン層40の上にCVD法により第1酸化膜41を層状に堆積する(図2(a))。これにより、1回目の酸化で第1酸化膜41を第1ポリシリコン層40の粒界部に入り込ませないようにする。そして、第1酸化膜41を第1ボトム膜24にパターニングした後(図2(b))、第1ポリシリコン層40の上に第2酸化膜42を形成する(図2(c))。2回目の酸化は短時間で終わるので、第1ポリシリコン層40の増速酸化が進行する前に第2酸化膜42の形成が完了する。このため、第1ポリシリコン層40をエッチングする際に第2酸化膜42の一部がマスクとならないようにすることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

21 - 40 / 340

[ Back to top ]