Fターム[5F038EZ16]の内容

Fターム[5F038EZ16]に分類される特許

41 - 60 / 340

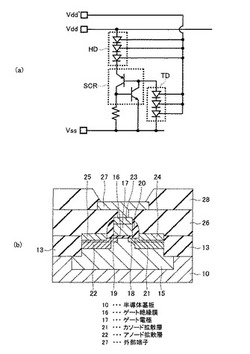

半導体装置

【課題】占有面積を増大させずに、電源投入開始後のチップ動作時にESD保護素子で発生するリーク電流を低減することができるESD保護素子を提供する。

【解決手段】電源ライン及び接地ラインを含む電子回路が形成された半導体基板10と、半導体基板10において電源ライン(Vdd)及び接地ライン(Vss)間に設けられ、サイリスタSCR及びサイリスタを駆動するトリガーダイオードTDを含む静電気放電保護素子とを有し、トリガーダイオードは、半導体基板10に形成されたアノード拡散層22と、アノード拡散層22から離間して半導体基板10に形成されたカソード拡散層21と、アノード拡散層22及びカソード拡散層21間において半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極17とを有し、外部電源に接続された外部端子(パッド電極27)がゲート電極17に電気的に接続されている構成とする。

(もっと読む)

電流検出回路およびそれを有するインバータ回路が備えられる半導体装置

【課題】電流値だけでなく電流の流れる向きまで検出できる電流検出回路およびそれを有するインバータ回路が備えられる半導体装置を提供する。

【解決手段】下アーム10b、10d、10fのIGBT11b、11d、11fおよびFWD12b、12d、12fに対してセンス素子を備えると共に、各センス素子に対して電流検出抵抗18a〜18fが直列接続させる。これにより、各センス素子および電流検出抵抗18a〜18fに基づいて、具体的には第1電位および第2電位を検出することにより、各相の電流経路に流れる電流の電流値の絶対値および向きを検出することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】高電圧仕様の受動素子と低電圧仕様の容量素子とを備える半導体装置の製造方法であって、低電圧仕様の容量素子の容量を確保できると共に、高電圧仕様の受動素子の当該高電圧仕様に対する耐圧を確保すると共に、製造時に高電圧仕様の受動素子の特性が変動することを防止できる半導体装置の製造方法を提供する。

【解決手段】半導体基板102上に絶縁膜116bを上部に有する下部電極110bと絶縁膜116aを上部に有する下部電極110aとを形成し、下部電極110b上の絶縁膜116bの膜厚を薄くし、半導体基板102上にゲート電極144を形成し、膜厚を薄くした第1の絶縁膜116b上に上部電極140を形成し、ゲート電極144および上部電極140を形成した後、全面に絶縁膜を形成し、絶縁膜を異方性エッチングしてゲート電極144の側面にサイドウォール148を形成する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多層配線構造を使って、キャパシタンスが大きく、かつキャパシタンス値が安定なキャパシタ素子を半導体基板上に集積化する。

【解決手段】多層配線構造18は、少なくとも第1層目の層間絶縁膜16と、第1層目の層間絶縁膜中に埋設された第1配線層と、を含み、第1配線層は、第1の電源に接続され前記第1の層間絶縁膜中に埋設された第1の配線パタ―ン15C1と、第2の電源に接続され前記第1の層間絶縁膜中に埋設された第2の配線パタ―ン15C2と、を含み、第1の配線パタ―ンと前記第2の配線パタ―ンとは容量結合して第1のキャパシタを形成し、第1の配線パタ―ンは積層配線パタ―ン13C上に形成されて、前記第4の電極パターン13Gと容量結合して第2のキャパシタを形成し、第4の電極パターンは第2の配線パタ―ンに電気的に接続されている。

(もっと読む)

薄膜キャパシタ

【課題】MIM構造の薄膜キャパシタにおいて、Ptに代わる上部電極を用いた場合であっても、IV特性や信頼性を維持する。

【解決手段】薄膜キャパシタ10は、基板12上に、下部電極14,誘電体層16,上部電極18を順次形成したMIM構造であり、上下の電極のうち、少なくとも上部電極18が、窒化物と金属を積層した積層電極となっている。窒化物としては、Ta,Tiなどの高融点金属を含むことが好ましく、また、窒化物と積層される金属が、前記窒化物に含まれる金属と同じであることが好ましい。更に、窒化物がSiを含んでいてもよい。少なくとも上部電極18に窒化物を含む積層電極を用いることで、Pt電極を用いる場合に必要だった特性回復のアニール処理の必要なく、同等のIV特性を得られるとともに信頼性も向上する。また、誘電体層16と上部電極18の密着性が改善され、剥離が生じない。

(もっと読む)

可変容量素子および可変容量素子の製造方法

【課題】 可変容量素子の動作不良を防止し、可変容量素子の信頼性を向上する。

【解決手段】 可変容量素子は、固定電極と、固定電極上に積層された絶縁層を含む絶縁部と、絶縁層上に絶縁層から離れる方向に移動可能に積層された可動部および可動部の一端を絶縁部に固定する固定部を含む可動電極と、可動電極に間隔を空けて対向する対向電極とを有している。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に含まれる静電気保護装置の面積を大きくすることなく、その破壊耐量及び維持電圧を大きくする。

【解決手段】第1導電型である半導体基板1と、半導体基板の上又は上部に形成された第2導電型である第1拡散層3と、第1拡散層の上部に形成され、第1導電型である第2拡散層5と、第2拡散層の上部に形成され、第2導電型である第3拡散層6と、第1拡散層の上部で且つ第2拡散層から間隔をおいて形成された第2導電型である第4拡散層8と、少なくとも第3拡散層の下に、第2拡散層と間隔をおき且つ下端部が第1拡散層の下端部よりも下に位置するように形成された第1導電型の第5拡散層2とを備えている。第3拡散層から第5拡散層までの最短距離と、第5拡散層から第4拡散層までの最短距離及び第1拡散層の下端部から第4拡散層までの最短距離のいずれか短い方の距離との和は、第3拡散層から第4拡散層までの最短距離よりも小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】オフトラ型ESD保護素子のESD耐量を増加する。

【解決手段】第2導電型ドレイン高濃度拡散層となる領域にトレンチを備え、トレンチ内に第2導電型の多結晶シリコン膜を埋め込むことで、第2導電型ドレイン高濃度拡散層の実効的な体積を増加することを実現する。これより、ゲート電極からドレインコンタクト孔の距離を大きくしたことと同じ効果が得られ、本発明の半導体装置はオフトラ型ESD保護素子として、素子サイズを変更しなくてもESD耐量の増加が可能となる。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体装置の製造における工程数を増加させることなく、抵抗素子の厚さの均一性を良好に維持できるようにした半導体装置の製造方法及び半導体装置を提供することを目的とする。

【解決手段】ポリシリコン抵抗素子20とゲート電極16とを同一基板に有する半導体装置の製造方法であって、フィールド酸化膜4を形成する工程とゲート酸化膜6を形成する工程とポリシリコン膜8を形成する工程とブロック用シリコン酸化層10を形成する工程とタングステンシリサイド膜12を形成する工程とポリシリコン抵抗素子20とゲート電極16とを形成する工程とサイドウォールスペーサー用絶縁膜26を形成する工程とサイドウォールスペーサー28を形成する工程とを含み、タングステンシリサイド層18a、18bよりもサイドウォールスペーサー用絶縁膜26の方がエッチングされ易い条件でサイドウォールスペーサー用絶縁膜26をエッチバックする。

(もっと読む)

半導体装置およびその製造方法

【課題】高温熱処理をせずに形成可能、かつ、信頼性劣化が少なく、かつ、従来のトレンチキャパシタと同様に、安定した容量値の供給、及び、大容量化が可能な、半導体キャパシタ、及び、その製造方法を提供する。

【解決手段】半導体基板の表面にLOCOS法およびウェットエッチングを用いて台形状トレンチを設け、台形状トレンチ表面に下部電極層5を形成し、下部電極層の上に容量絶縁膜6と上部電極7を順次積層する。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体膜の表面をレジストに曝すことなく、特性が異なる複数のキャパシタを有する半導体装置を製造する。

【解決手段】半導体装置の製造方法は、基板上方に絶縁膜を形成する工程、絶縁膜上方に下部電極層を形成する工程、下部電極層上に強誘電体膜を形成する工程、強誘電体膜上に第1上部電極層を形成する工程、第1上部電極層上に、第1領域を覆う第1レジストを形成する工程、第1レジストをマスクとしてエッチングを行うことにより、第2領域の第1上部電極層を除去するとともに、第2領域の強誘電体膜を削る工程、第1領域の第1上部電極層上及び第1領域以外の強誘電体膜上に、第2上部電極層を形成する工程、第1領域及び第2領域に第2レジストを形成する工程、第2レジストをマスクとして第1上部電極層、第2上部電極層、強誘電体膜及び下部電極層をエッチングし、第1のキャパシタ及び第2のキャパシタを形成する工程、を有する。

(もっと読む)

半導体装置

【課題】体格の増大が抑制された半導体装置を提供する。

【解決手段】絶縁分離トレンチによって半導体基板が複数の素子形成領域に区画され、各素子形成領域に少なくとも1つの電子素子が形成された半導体装置であって、半導体基板の厚さ方向に垂直な平面方向において、1本の絶縁分離トレンチを介して、2つの素子形成領域が互いに隣接するように、絶縁分離トレンチの平面方向に沿う形状が、格子状となっている。

(もっと読む)

半導体回路装置の製造方法

【課題】MOSトランジスタ、容量素子を有する半導体装置の製造コストを削減できる製造方法を提供する。

【解決手段】MOSトランジスタのゲート電極が第1のポリシリコン膜から成り、容量が第1のポリシリコン膜と容量膜と第2のポリシリコン膜から成り、ノーマリーオフトランジスタと容量下部電極の低抵抗化を同時に行い、N型MOSトランジスタと容量上部電極の低抵抗化を同時に行うことを特徴とする半導体回路装置の製造方法。

(もっと読む)

集積回路をDCおよびRF遮蔽する方法構造

【課題】集積回路をDCおよびRF遮蔽する方法と構造を提供すること。

【解決手段】組み合わせられて集積回路デバイスを形成する回路を電磁気的に遮蔽するための方法であって、導電性材料によって横方向および下方を囲まれた隔離型のシリコン・アイランドを供給する。

(もっと読む)

半導体集積装置及び半導体集積装置の製造方法

【目的】耐放射線特性を高めることが可能な半導体集積装置及び半導体集積装置の製造方法を提供することを目的とする。

【構成】半導体支持基板上の絶縁層の上面に形成されているシリコン薄膜層内における上記絶縁層との境界に隣接する境界近傍領域中に、この境界に近いほど不純物の濃度が高くなる領域が形成されている。

(もっと読む)

保護トランジスタおよび半導体集積回路

【課題】占有面積が小さく、所望の耐圧と熱破壊の防止を両立した保護トランジスタを提供する。

【解決手段】ゲート長方向の一方の側でゲート直下の領域に隣接しているゲート・ドレイン間領域REgdが、ゲート幅方向に互いに隣接する領域として、第1領域REgd1と第2領域REgd2とを有する。第1領域は、ドレイン耐圧が相対的に大きく、第2領域は、ドレイン電極(ドレインコンタクト部に設けられているシリサイド層10D)からの距離が平面視で第1領域より遠く、ドレイン耐圧が相対的に小さい。このため、耐圧が低いゲート・ドレイン間領域REgd2の加熱部分Aからドレインコンタクト部が遠いが、面積は小さく(または拡大しない)構造となっている。

(もっと読む)

半導体装置

【課題】ノイズが高周波である場合においても、多層配線層を介してデジタル回路とアナログ回路の間でノイズが伝播することを抑制する。

【解決手段】回路分離領域40は第1回路領域20と第2回路領域30の間に位置している。回路分離領域40には複数の第1導体及び複数の第1ビアが設けられている。複数の第1導体は、電源ライン110より下層に設けられ、電源ライン110に対向しており、かつ繰り返し配置されている。複数の第1ビアは多層配線層の中に、複数の第1導体それぞれごとに設けられており、各第1導体を電源ライン110に接続している。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】製造効率を向上すると共に、内部回路の保護を的確に行うことを容易に可能にする。

【解決手段】ESD保護素子101の高濃度不純物領域121SH,120DH,122SHを、ゲート電極111G,112Gの下方に形成しない。高濃度不純物領域121SH,120DH,122SHを、半導体基板100の面(xy面)にて、少なくとも低濃度不純物領域121SL,121DL,122DL,122SLを介してゲート電極111G,112Gの側部に位置するように形成する。また、高濃度不純物領域121SH,120DH,122SHを、低濃度不純物領域121SL,121DL,122DL,122SLおよび不純物領域121SM,120DM,122SMよりも深い位置まで形成する。

(もっと読む)

半導体装置、高周波集積回路、高周波無線通信システムおよび半導体装置の製造方法

【課題】SOS基板の異方性を低減して半導体装置のデバイス特性の面内均一性を向上する。

【解決手段】絶縁体基板101の主面上にSi層(またはSi基板)100を有する半導体装置10において、絶縁体基板101はサファイア基板101であり、絶縁体基板101の主面はc面である。サファイア基板101において異方性の少ないc面にSi層100を形成するので、Si層100上に形成された半導体装置10のデバイス特性の面内均一性を向上することができる。

(もっと読む)

41 - 60 / 340

[ Back to top ]