Fターム[5F044RR18]の内容

ボンディング (23,044) | ワイヤレスボンディング関連事項 (2,154) | 容器・封止 (1,675) | 封止構造 (460)

Fターム[5F044RR18]に分類される特許

381 - 400 / 460

配線基板およびアンダーフィル方法並びに半導体装置

【課題】 バンプが高密度に形成された半導体チップをフリップチップ接続により配線基板に搭載する際に、容易にアンダーフィルすることができる配線基板を提供する。

【解決手段】 フリップチップ接続により半導体チップ20を搭載する配線基板10であって、前記半導体チップ20の搭載領域の内外で一方の開口部16aと他方の開口部16bとが各々開口し、前記一方の開口部16aと前記他方の開口部16bとが、基板10の内部を通過して設けられた連通流路16cにより連通する通気孔16が設けられていることを特徴とする。

(もっと読む)

電子デバイス装置およびその製造方法

【課題】 接合荷重を低減して接合部および基板の破損を防止でき、デバイス機能部の動作信頼性の向上をも図ることができる電子デバイス装置およびその製造方法を提供する。

【解決手段】 本発明の電子デバイス装置20は、デバイス機能部Pが形成された第1基板21と、デバイス機能部Pを封止する中空部30を形成するためのシール用バンプ23および電気的接続のための導通用バンプ24がそれぞれ形成された第2基板22とが接合されることで製造され、第1基板21と第2基板22との接合が、シール用バンプ23を加熱溶融させる工程と、導通用バンプ24を第1基板21上に熱圧着させる工程とを有する。この構成により、接合荷重は主として導通用バンプ24の熱圧着接合に要する荷重だけで足りるのでトータル荷重が大幅に低減され、接合部の破損を防止できる。また、接合部のシール性が高められるのでデバイス機能部の動作信頼性を高めることができる。

(もっと読む)

半導体装置、回路基板及び半導体装置の製造方法

【課題】 半導体素子と回路基板の電気的な接合と接合部分の封止とを1工程で行うとともに、半導体装置における電気的な接続抵抗を安定的に低減させる。

【解決手段】 回路基板200上に半導体素子300がフリップ実装される半導体装置100を製造するにあたり、回路基板200の最上層配線202に保護膜400を設ける工程と、保護膜400を選択的に除去して最上層配線202が露出するホール402を形成する工程と、ホール402に最上層配線202の露出部から上方へのメッキ成長によりプラグ204を形成する工程と、加熱により半導体素子300の電極パッド302とプラグ204とを接合しつつ保護膜400の上面と半導体素子300の底面とを接合する工程と、により製造するようにした。

(もっと読む)

半導体装置用実装基板及び半導体装置の実装構造

【課題】フリップチップ接合された半導体装置との間にアンダーフィル樹脂が装填される半導体装置用実装基板及び半導体装置の実装構造に関し、アンダーフィル樹脂内にボイドが発生することを防止する。

【解決手段】表面にソルダーレジスト22が配設されると共に、このソルダーレジスト22の半導体装置25が実装される部位に半導体装置25を実装するための第1の開口部23が形成されてなる半導体装置用実装基板において、前記ソルダーレジスト22の第1の開口部23の周辺部に、アンダーフィル樹脂配設時におけるアンダーフィル樹脂の流れ速度を調整する速度調整用開口部30Aを設ける。

(もっと読む)

電子装置及びその製造方法

【課題】 実装部品をはんだを用いて基板に実装する構造を有した電子装置及びその製造方法に関し、加熱時に電極パターン間に短絡が発生したり、封止樹脂内にクラックが発生したりすることを防止しうる電子装置及びその製造方法を提供する。

【解決手段】 フットパターン24A,24B及びソルダーレジスト25が設けられると共にソルダーレジスト25の開口部からフットパターン24A,24Bが露出する構成とされた基板23と、はんだ26により基板23に実装される実装部品20A,20Bと、基板23上に形成されて実装部品20A,20Bを封止する封止樹脂29とを有し、かつ、はんだ26の一部(乗り上げ部26A,26B)が実装部品20A,20Bの下部においてソルダーレジスト25の上部に乗り上げた構成とする。

(もっと読む)

電気光学装置の製造方法、異方性導電材、及び異方性導電材の製造方法

【課題】 ICチップ等といった被接続部材と、ガラス基板等といった基板とを、異方性導電材を用いて常に安定して導電接続できるようにする。

【解決手段】 端子38aを有する対象物M1と、端子38bを有する対象物M2と、端子38aと端子38bとを導電接続する異方性導電材8’とを有する液晶表示装置を製造するための製造方法である。この製造方法において異方性導電材8は、第1基材31及び第2基材32と、これら第1基材31と第2基材32との間に配置された熱で溶融する半田層33aと、第1基材31、第2基材32及び半田層33aを貫通する貫通孔35とを有する。この製造方法は、対象物M1と対象物M2との間に異方性導電材8’を配置する工程と、異方性導電材8’を加熱及び加圧して半田33を貫通穴35に流動させて、端子38aと端子38bとを導電接続する導通部33bを形成する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置における品質および信頼性の向上を図る。

【解決手段】 ポリイミド樹脂からなるテープキャリア1と表面にポリイミド樹脂の保護膜2eを有した半導体チップ2の接続において、テープ本体1aの半導体チップ2の電極列より内側の領域にダミーパターン1dが設けられていることにより、テープ本体1aをダミーパターン1dが支えるため、テープ本体1aと半導体チップ2の表面との間に隙間を確保できる。これにより、封止工程でアンダーフィル材8を充填する際に、テープ本体1aと半導体チップ2の間の未充填部分の発生を防ぐことができ、ボイドが形成されることを防止できる。その結果、ポリイミド樹脂の保護膜2eの剥離や、チップクラックの発生を阻止することができ、半導体装置の品質および信頼性の向上を図ることができる。

(もっと読む)

圧電振動子

【課題】圧電振動子に形成される外部接続用電極の形成寸法精度公差が比較的大きいため、圧電振動子の小型化が進むにつれ、圧電振動子内に搭載する圧電振動板に形成される外部接続用電極と、圧電振動子を構成する容器体に形成される電極パッドとの間に形成位置ズレが生じる場合がある。

【解決手段】電極パッドと外部接続用電極の間に、電極パッド及び外部接続用電極に対向する両主面上に両主面間で電気的に接続している導通用電極が形成された平板状の絶縁基板が配置されており、この導通用電極を介して電極パッドと外部接続用電極が電気的に接続且つ固着されている圧電振動子。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体チップの電極と配線との高精度のフリップ・チップ接続を図る。

【解決手段】 上面及び下面に所定パターンの配線を有し上面及び下面の前記配線の一部は上下面を貫通する配線で接続される配線基板と、配線基板の上面配線に半田を介して電極がフリップ・チップ接続される半導体チップと、配線基板の下面配線に重ねて形成される外部電極端子とを有する半導体装置であって、電極が接続される配線表面部分はその周囲の配線部分よりも窪みかつ窪み上の半田は他の配線表面の半田よりも厚くなっている。また、配線基板の上面と半導体チップの下面の隙間には絶縁性樹脂が充填されて封止体が形成され、封止体によって隙間が塞がれている。

(もっと読む)

半導体装置の製造装置およびその製造方法

【課題】半導体素子をフリップ実装する回路実装基板の配線電極と半導体素子の電極パッドに形成した金属バンプとの接続不良を大幅に軽減することができる半導体装置の製造装置およびその製造方法を提供することを目的とする。

【解決手段】半導体装置の製造装置であって、半導体素子をフリップ実装する回路実装基板1の配線電極2上に凹部10を形成する加工手段と、前記凹部に導電性接着剤を塗布する塗布手段を含むことにより、回路実装基板の配線電極と半導体素子の電極パッドに形成した金属バンプとの接続不良を大幅に軽減することができる。

(もっと読む)

両面粘着テープ

【課題】 ブロッキングや糊はみ出しがなく打ち抜き特性などの加工特性が良好であり、高温にさらされても優れた粘着力及び凝集力を維持することができる両面粘着テープを提供する。

【解決手段】 20μm以下の厚さの不織布からなる芯材、前記芯材の両面に配置されたガラス転移点(Tg)が−20℃〜20℃でありかつ重量平均分子量が100万以上であるアクリル系ポリマーを含む粘着剤層、を含む両面粘着テープであって、前記両面粘着テープの総厚が60μm以下である、両面粘着テープ。

(もっと読む)

中空半導体パッケージの製造方法

【課題】 加熱により反りが発生する脆性な基板を利用した場合でも基板の破損を防止することができ、生産性の高い中空半導体パッケージの製造方法を提供する。

【解決手段】 半導体素子2の回路面を配線基板側にして、半導体素子を基板1にフリップチップ実装し、光硬化性封止用部材15を、半導体素子が搭載された基板側から半導体素子及び基板に被せ、光硬化性封止用部材を、真空下で、半導体素子及び基板へ弾性体17を介した加圧押し当てにより貼り付けて半導体素子と基板との間の隙間に中空部4を形成し、真空状態を維持したまま、光硬化性封止用部材に樹脂硬化用光線を照射して光硬化性封止用部材を硬化させる。半導体素子を、基板上にマトリクス状又は直線状に複数配置し、光硬化性封止用部材に樹脂硬化用光線を照射して光硬化性封止用部材を硬化させた後、各々の半導体素子を基板とともに個別に切断してもよい。

(もっと読む)

インターポーザおよびそれを用いた半導体装置、ならびに半導体装置の製造方法

【課題】 半導体装置の組み立て工程後の有機樹脂基板の素子搭載面の反り上がりを抑制し、製造歩留まりを向上させる半導体装置の製造方法を提供する。

【解決手段】 半導体装置100は、有機樹脂基板101により構成されるインターポーザの素子搭載面111に半導体チップ105がはんだ接合されてなる。インターポーザは、有機樹脂基板101により構成されて、一方の面に半導体チップ105が搭載されるインターポーザであって、半導体装置100の組み立て工程前の状態において、素子搭載面111の裏面113の側が凸状に湾曲した反りを有する。

(もっと読む)

フリップチップの実装構造

【課題】バンプピッチを300μm以下に微細化した場合でも、補強用樹脂の注入性を良好にする。

【解決手段】バンプピッチが300μmでチップサイズが10mm□のフリップチップ4をセラミック多層基板1上に実装する場合に、注入口間隔hを40μm以上にした。注入口間隔をそのような大きさにすることにより、フリップチップ実装部の中央部にボイドを発生させることなく補強用樹脂8を良好に注入することができるようになる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 半導体実装プロセスにおいて、LSI素子と回路基板とのギャップを十分に確保し、シード層上へのハンダの濡れ広がりを防止し、接合の信頼性を向上する事を特徴とする半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法において、半導体素子を構成する第1基板または回路配線を有する第2基板のいずれか一方の基板上に、ドライフィルムレジストを用いて、アスペクト比が1以上の開口パターンを有するレジストマスクを形成する。次に、前記開口内に、第1の金属膜を前記膜厚の1/2以上の高さに形成する。次に、前記開口内の第1の金属膜に重ねて、第2の金属膜を、前記レジストマスクの膜厚を越え、かつ隣接する開口の第2金属膜と接触しないように形成する。次に、レジストマスクを残したまま、レジストマスクから突出する第2金属膜を、他方の基板上の電極に対して、フラックスレス接合する。接合の後に、レジストマスクを剥離する。

(もっと読む)

基板実装構造および表示装置

【課題】 接着層から回路基板および半導体基板を剥離しにくくし、また、回路基板の第1の端子と半導体基板の第2の端子との間の電気的な接続をより確実にする基板実装構造を提供することにある。

【解決手段】 本発明の基板実装構造(60)は、第1の端子(42)が設けられた第1の基板(40)と、第2の端子(52)が設けられた第2の基板(50)と、第1の端子(42)と第2の端子(52)とが電気的に接続するように第1の基板(40)と第2の基板(50)とを接着する接着層(20)とを備え、接着層(20)は、樹脂(21)と、樹脂(21)中に分散された絶縁性粒子(22)とを有し、絶縁性粒子(22)は、所定の平均粒径を有し、第1の端子(42)は、第1の端子(42)から第2の端子(52)への電気的な経路において、第2の端子(52)に最も近い最近接部分(43)を有し、最近接部分(43)は、絶縁性粒子(22)の所定の平均粒径よりも短い幅を有する。

(もっと読む)

撮像装置

【課題】気密性及び接続信頼性を向上させるとともに、不要光によるノイズを低減させた撮像装置およびセンサーユニットを提供すること。

【解決手段】表面に配線導体3が形成された基板1と、配線導体3に導電性バンプ5を介して接合された電極を有する撮像素子2と、導電性バンプ5を覆うように撮像素子2と基板1との間に設けられた接着剤層8とを有する。接着絶縁粒子7は、無機絶縁粒子7と金属または金属被覆粒子6とが熱硬化性樹脂に含有されて成る。

(もっと読む)

半導体基板実装構造、表示装置、接着シートおよび基板実装方法

【課題】 接着層から回路基板および半導体基板を剥離しにくくし、また、回路基板の第1の端子と半導体基板の第2の端子との間の電気的な接続をより確実にする半導体基板実装構造を提供することにある。

【解決手段】本発明の半導体基板実装構造(60)は、回路基板(40)と、半導体基板(50)と、回路基板(40)と半導体基板(50)とを接着する接着層(20)とを備え、接着層(20)は、樹脂(22a)と、樹脂(22a)中に分散された絶縁性粒子(22b)とを含み、接着層(20)のうち第2の主面(20b)からの厚さが第2の端子(50a)の厚さに相当する厚さである領域を所定の領域(X)とすると、接着層のうち所定の領域(X)内の単位体積あたりの絶縁性粒子(22b)の数が、接着層(20)のうち所定の領域(X)以外の領域(Y)の単位体積あたりの絶縁性粒子(22b)の数よりも小さい。

(もっと読む)

半導体装置

【課題】 バンプ電極によって接続される半導体チップおよび電子部品の間に封止されるアンダーフィル樹脂中においてボイドの発生を抑止した半導体装置を提供する。

【解決手段】 第1の半導体チップ10および第2の半導体チップ20のそれぞれのバンプ形成面を対向させて形成される半導体装置において、第1の半導体チップ10および第2の半導体チップ20のそれぞれの最表面に形成された保護膜である絶縁膜14,24の少なくとも一方の中であって、バンプ形成領域12,22の近傍に、第1の半導体チップ10および第2の半導体チップ20の間にアンダーフィル樹脂を流し込むための開口部16,26を設けたものである。

(もっと読む)

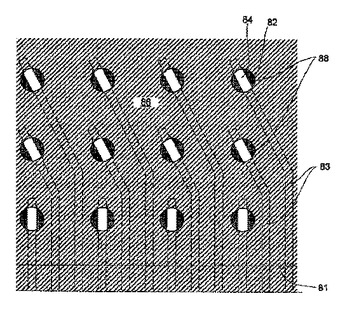

基板上に狭い配線部分を有するフリップチップ配線

基板上のダイのフリップチップ配線は、配線の隆起を、キャプチャパッド上にではなく、リードまたはトレースの上の狭い配線パッドの上に嵌合することによってなされる。狭い配線パッドの幅は、取り付けられるダイ上の隆起のベース直径未満である。また、フリップチップパッケージは、活性表面において配線パッドに取り付けられた半田の隆起を有しているダイと、ダイ取り付け表面において導電性トレースの上に狭い配線パッドを有している基板とを含んでおり、上記基板における隆起は、トレース上の狭いパッドに嵌合される。  (もっと読む)

(もっと読む)

381 - 400 / 460

[ Back to top ]