Fターム[5F045AF02]の内容

気相成長(金属層を除く) (114,827) | 被成膜面の組成、基板の特徴、ダミー基板、マスク (7,328) | 被成膜面が半導体であるもの (4,466) | IV族(Ge、SiC、C、Sn等)面への成膜 (2,477)

Fターム[5F045AF02]の下位に属するFターム

Si面への成膜 (1,762)

Fターム[5F045AF02]に分類される特許

61 - 80 / 715

エピタキシャルウエハおよびその製造方法、半導体装置およびその製造方法

【課題】本発明は、結晶欠陥が少なく、キャリア時定数が十分大きい高品質なエピタキシャルウエハの製造方法と、当該エピタキシャルウエハを用いた半導体装置の製造方法の提供を目的とする。

【解決手段】本発明のエピタキシャルウエハの製造方法は、(a)3×1018cm-3以下の不純物濃度を有するSiC基板12上に、1×1014cm-3以上1016cm-3台以下の不純物濃度を有するエピタキシャル層13をエピタキシャル成長により形成する工程と、(b)前記工程(a)により得られた構造のSiC基板12の側から、エピタキシャル層13のうち所定の厚みを残して、SiC基板12の全部とエピタキシャル層13の一部とを連続的に除去する工程とを備える。

(もっと読む)

III族窒化物積層体の製造方法

【課題】Al含有率が高いIII族窒化物半導体上にP型GaN層が形成された積層体において、その表面が極めて平滑であり、電極特性が良好な積層体の製造方法を提供する。

【解決手段】AlXGaYInZN(X、YおよびZが、X+Y+Z=1.0,Y≧0,Z≧0,0.5≦X≦1.0である)層と、不純物原子がドープされたGaN層と有するIII族窒化物積層体を製造する方法であって、P型GaN層16が、層厚みをT[nm]とし、P型GaN層の層厚み方向における成長速度をGR[nm/分]とし、P型GaN層を形成するために用いられるGa原料の流量をFGa[μmol/分]とし、不純物原子原料の流量をFi[μmol/分]としたときに、GRが0.15以上2.0以下、(Fi/FGa)×ln(T)が0.1を超え0.4以下となるように成長させる。

(もっと読む)

新規な水素化シリコンゲルマニウム、その製造法および使用法

【課題】本発明は、新規水素化シリコンゲルマニウム化合物、それらの合成法、それらの成膜法、およびそれらの新規化合物を用いて作製された半導体構造を提供する。

【解決手段】これらの化合物は、式:(SiHn1)x(GeHn2)yによって定義される。式中、xは2,3または4であり;yは1,2または3であり;x+yは3,4または5であり;n1は、化合物中の各Si原子に関して独立に0,1,2または3であって原子価を満たし;n2は、化合物中の各Ge原子に関して独立に0,1,2または3であって原子価を満たし;但し、yが1のとき、n2は0ではなく;さらに、xが3、かつ、yが1のとき、n2は2または3であり;さらに、xが2、かつ、yが1のとき、n2は3である。

(もっと読む)

半導体発光素子、窒化物半導体層成長用基板及び窒化物半導体ウェーハ

【課題】高効率の半導体発光素子、窒化物半導体層成長用基板及び窒化物半導体ウェーハを提供する。

【解決手段】実施形態によれば、第1半導体層と、第2半導体層と、それらの間に設けられた発光層と、を備えた半導体発光素子が提供される。第1半導体層は、発光層とは反対の側の第1主面に設けられた複数の構造体を有する。複数の構造体のそれぞれは凹部、または、凸部である。複数の構造体のうちのいずれかである第1の構造体の形状の重心と、複数の構造体のうちで第1の構造体に最も近い第2の構造体の形状の重心と、は、第2軸上に並ぶ。凹部の深さをhbとし、凹部の底部の第2軸に沿った幅をrbとしたとき、rb/(2・hb)≦0.7を満たす。第1主面の単位面積あたりの底部の面積の合計の、単位面積あたりの凸部の合計の面積に対する比は、0.17よりも小さい。

(もっと読む)

温度測定装置、温度測定方法、記憶媒体及び熱処理装置

【課題】処理容器内にて基板が載置されると共に回転する回転テーブルを備えた熱処理装置において、回転中の回転テーブルにおける基板の温度分布を測定すること。

【解決手段】

処理容器内に設けられた回転テーブルの回転時に当該回転テーブルの一面側を、径方向に沿って繰り返し走査して複数のスポット領域の温度を測定する放射温度測定部と、前記回転テーブル上における放射温度測定部の走査領域に割り当てられたアドレスと放射温度測定部の温度測定値とを対応付けた温度データを記憶するための記憶部と、走査の周期及び回転テーブルの回転数に基づいて特定された各スポット領域のアドレスに温度測定値を書き込むためのデータ作成部と、前記記憶部に書き込まれた温度データに基づいて、基板の温度分布を含む回転テーブルの一面側の温度分布を表示する処理を行うデータ処理部と、を備えるように温度測定装置を構成する。

(もっと読む)

半導体エピタキシャル基板、およびその製造方法

【課題】

高周波信号遮断後の回復が早く、素子分離特性のよい化合物半導体エピタキシャル基板を提供する。

【解決手段】

半導体エピタキシャル基板は、単結晶基板と、単結晶基板上にエピタキシャル成長されたAlN層と、AlN層の上にエピタキシャル成長された窒化物半導体層とを有し、単結晶基板とAlN層間界面より、AlN層と窒化物半導体層間界面の方が凹凸が大きい、ことを特徴とする。

(もっと読む)

CVD装置

【課題】膜上に付着し又は膜中に埋没したSiCパーティクル等が低減されたSiCエピタキシャル膜を作製することができるCVD装置を提供する。

【解決手段】本発明に係るCVD装置は、ウェハを水平に載置するウェハ載置部材と、該ウェハ載置部材に対向してその上方に配置する加熱部材と、該加熱部材の材料よりも膜材料の付着性が高い材料からなり、前記加熱部材と前記ウェハ載置部材との間に前記加熱部材に近接して配置して気相中から前記加熱部材へのガスの堆積を遮る遮蔽部材と、を備えたことを特徴とする。

(もっと読む)

半導体発光素子、窒化物半導体層、及び、窒化物半導体層の形成方法

【課題】低転位密度と良好な表面平坦性とを両立した、高効率な半導体発光素子、窒化物半導体層、及び、窒化物半導体層の形成方法を提供する。

【解決手段】実施形態によれば、下地層と、第1半導体層と、発光層と、第2半導体層と、を備えた半導体発光素子が提供される。発光層は下地層と第1半導体層との間に設けられる。第2半導体層は下地層と発光層との間に設けられる。下地層は、第2半導体層の側の第1主面と、第1主面とは反対側の第2主面と、を有する。下地層は、第2主面に設けられ、凹部と側部と凸部とを有する凹凸を有する。凸部に繋がる転位の少なくともいずれかは、側部に繋がる。凸部に繋がる転位のうちで第1主面に到達する転位の割合は、凹部に繋がる転位のうちで第1主面に到達する転位の割合よりも低い。第1主面のうちで凹部と重なる領域に繋がる転位は、凹部に繋がる転位よりも少ない。

(もっと読む)

発光ダイオード用基板及び発光ダイオード

【課題】高い光取出し効率を実現でき、かつ、製造が容易で低コストな発光ダイオード用基板及び発光ダイオードを提供する。

【解決手段】表面sに発光層7を含む半導体層3が形成される発光ダイオード用基板であって、サファイア基板からなり、表面sには、発光層7が発光する光を乱反射するランダムに配置された凹凸が形成され、かつ、凹凸は結晶方位を反映して形成されており、凹凸の高さが1μm以上5μm以下であり、表面のX線回折ロッキングカーブ半値幅が60秒以下である。

(もっと読む)

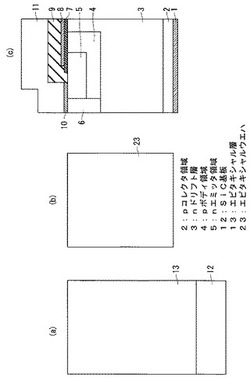

ダイアモンド基板上炭化珪素並びに関連するデバイス及び方法

【課題】ワイドバンドギャップ材料内に、接合温度低下、動作中の高電力密度化、及び定格電力密度における信頼性向上を達成する高電力デバイスを形成する。

【解決手段】SiC層10にSiO2層を形成し、次いで、熱伝導率を高めるためにダイアモンド層11を形成する。そして、SiC層10の厚さを低減し、ダイアモンド層11及びSiC層10の向きを逆にしてダイアモンド11を基板とする。次いで、SiC層10上に、バッファ層16、ヘテロ構造層14及び15を形成する。

(もっと読む)

発光ダイオード

【課題】格子欠陥が発生することを防止した発光ダイオードを提供する。

【解決手段】発光ダイオード10は、基板100と、第一半導体層120と、第二半導体層140と、活性層130と、第一電極150と、第二電極160と、を含む。第一半導体層、活性層、及び第二半導体層は、基板から離れる方向に沿って、基板に順次的に積層され、第一電極は、第一半導体層に電気的に接続され、第二電極は、第二半導体層に電気的に接続され、第一半導体層の基板と隣接する表面は、複数の空隙を含むパターン化されたカーボンナノチューブ層102である。第一半導体層のパターン化された表面が基板に接続することによって複数のキャビティが形成される。

(もっと読む)

電界効果トランジスタ用窒化物半導体エピタキシャルウェハ、窒化物半導体系電界効果トランジスタ、及び電界効果トランジスタ用窒化物半導体エピタキシャルウェハの製造方法

【課題】電子のトラッピング現象を緩和すると共に、ヘキサゴナル欠陥の発生を抑制可能な窒化物半導体エピタキシャルウェハの製造方法を提供する。

【解決手段】基板1上に核生成層2を形成し、その核生成層2上に第一の窒化物半導体層3を形成し、その第一の窒化物半導体層3上に、前記第一の窒化物半導体層3よりも電子親和力の小さい第二の窒化物半導体層4を形成する窒化物半導体エピタキシャルウェハ10の製造方法において、前記第一の窒化物半導体層3を形成する際の成長温度が、前記第二の窒化物半導体層4を形成する際の成長温度よりも低くするものである。

(もっと読む)

窒化物半導体発光ダイオード素子

【課題】大電流密度の電流を活性層に注入した場合における発光効率の低下を抑制する。

【解決手段】n型窒化物半導体層と、p型窒化物半導体層と、n型窒化物半導体層とp型窒化物半導体層との間に設けられた活性層とを備え、活性層は、量子井戸層と、p型窒化物半導体層に接する障壁層とを含む多重量子井戸構造を有し、障壁層は、AlGaN層と、GaN層との2層構造からなり、障壁層のAlGaN層が量子井戸層のp型窒化物半導体層側に接している窒化物半導体発光ダイオード素子である。

(もっと読む)

IV族基板表面上での窒化物半導体素子の層構造

【課題】IV族基板表面の混合結晶上に結晶性を向上させたIII族窒化物層構造を有する窒化物半導体素子を提供する。

【解決手段】立方晶のIV族基板材料のIV族基板表面を有する基板上にエピタキシャル堆積されている、III族窒化物層構造を有する窒化物半導体素子であって、IV族基板表面が、C2対称性の単位格子を有するが、C2対称性より高度の回転対称性の単位格子は有さない{nml}表面[式中、n、mはゼロ以外の整数であり、かつl≧2]であるようにする。

(もっと読む)

電界効果トランジスタ、製造用基板、およびその製造方法

【課題】電流量の減少や断線などの問題を抑制した状態で、電界効果トランジスタをより微細化できるようにする。

【解決手段】基板101の上に形成されたグラフェンからなるフィン状のチャンネル領域102と、ゲート電極104およびゲート電極104を挟んでチャンネル領域102に接続されたソース電極105およびドレイン電極106とを備える。例えば、チャンネル領域102は、グラフェンが1層から4層程度積層されたものである。図1に示す例では、ゲート電極104は、チャンネル領域102にゲート絶縁層103を介して形成されている。

(もっと読む)

基板処理装置、及び、基板の製造方法

【課題】ビューポートが汚れることにより、放射温度計による正確な温度測定ができなくなることを抑制する。

【解決手段】複数枚の基板を保持するボートと、ボートを囲む様に設けられ反応室を構成する筒状発熱材と、筒状発熱材を囲む様に設けられた反応管と、筒状発熱材と反応管との間に設けられた筒状断熱部と、筒状発熱材と筒状断熱部との間に設けられた温度測定用チップと、温度測定用チップからの放射光が入射されることにより温度を測定する放射温度計と、温度測定用チップと放射温度計との間に設けられ、温度測定用チップからの放射光を透過するビューポートと、筒状発熱材と筒状断熱部との間の間隙に設けられ、ビューポートに向けて不活性ガスを供給する第1ガス供給口を有するブローノズルと、を具備する。

(もっと読む)

半導体デバイスおよび方法

【課題】光照射に適合した、少なくとも1つの電位障壁、又は表面障壁を持つ半導体デバイスの製造または処理に関し、高い絶縁破壊電圧と、大電流で低いキヤリア密度を有するデバイスの製造方法を提供する。

【解決手段】a)基板1を用意するステップと、b)第1エピタキシャル半導体層3を基板1の上に設けるステップと、c)1次元または2次元の繰り返しパターンを形成するステップと、を含み、パターンの各部分が、0.1〜50の範囲のアスペクト比を有するようにした方法を開示する。対応する半導体デバイス、電子回路および装置も開示している。

(もっと読む)

歪み、反り、及びTTVが少ない75ミリメートル炭化珪素ウェハ

【課題】薄切りしたSiCウェハの歪み、反り、全厚さ変動(TTV)を低減する。

【解決手段】直径が少なくとも約75ミリメートル(3インチ)のSiCブールを、SiCの種結晶使用昇華成長により成長させ、該SiCブールを薄切りにして少なくとも1つのウェハを得る。その後、内層面損傷がウェハの各側において同一となるように、ラッピング下方力を、前記ウェハを折り曲げる下方力未満の量に制限しつつ、SiCウェハをラッピングし、SiCウェハを研磨する。これにより、高品質のSiC単結晶ウェハ16が得られる。該ウェハ16上には複数の窒化物エピタキシャル層18等が形成される。

(もっと読む)

エピタキシャル構造体の製造方法

【課題】本発明は、エピタキシャル構造体の製造方法に関する。

【解決手段】本発明のエピタキシャル構造体の製造方法は、少なくとも一つの結晶面を有する基板を提供する第一ステップと、前記基板の結晶面に複数の空隙を含むカーボンナノチューブ層を配置し、前記基板の結晶面の一部を前記カーボンナノチューブ層の複数の空隙によって露出させる第二ステップと、前記基板の結晶面にエピタキシャル層を成長させ、前記カーボンナノチューブ層を覆う第三ステップと、前記基板及び前記カーボンナノチューブ層を除去する第四ステップと、を含む。

(もっと読む)

立方晶炭化珪素膜の製造方法

【課題】横方向結晶成長における横方向成長速度が縦方向成長速度と同等の成長速度を維持することにより、等方的に立方晶炭化珪素を成長させることができ、より広い低欠陥領域を有する立方晶炭化珪素膜を形成させることのできる立方晶炭化珪素膜の製造方法を提供する。

【解決手段】シリコン基板2の表面2aに立方晶炭化珪素層11を形成する工程と、立方晶炭化珪素層11を選択除去し、結晶成長領域の結晶方位面が{100}面となる所望のパターンの立方晶炭化珪素シード層11aを形成する工程と、この立方晶炭化珪素シード層11a上に立方晶炭化珪素を成長させる工程と、を有する。

(もっと読む)

61 - 80 / 715

[ Back to top ]