Fターム[5F045AF02]の内容

気相成長(金属層を除く) (114,827) | 被成膜面の組成、基板の特徴、ダミー基板、マスク (7,328) | 被成膜面が半導体であるもの (4,466) | IV族(Ge、SiC、C、Sn等)面への成膜 (2,477)

Fターム[5F045AF02]の下位に属するFターム

Si面への成膜 (1,762)

Fターム[5F045AF02]に分類される特許

141 - 160 / 715

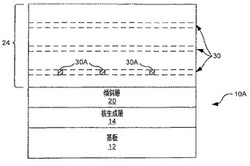

中間層構造を有する厚い窒化物半導体構造、及び厚い窒化物半導体構造を製造する方法

【課題】基板上に成長されるGaN層は歪みを受ける可能性があり、歪みのレベルがある閾値を超えると、GaN層に亀裂が入る恐れがある。

【解決手段】半導体構造は、基板、前記基板上の核生成層、前記核生成層上の組成傾斜層、及び前記組成傾斜層上の窒化物半導体材料の層を含む。前記窒化物半導体材料の層は、前記窒化物半導体材料の層の中に間隔をおいて配置された複数の実質的に緩和された窒化物中間層を含む。前記実質的に緩和された窒化物中間層は、アルミニウム及びガリウムを含み、n型ドーパントで導電的にドープされ、また前記複数の窒化物中間層を含む前記窒化物半導体材料の層は、少なくとも約2.0μmの全厚を有する。

(もっと読む)

炭化珪素半導体素子の製造方法および炭化珪素層付ウェハ

【課題】炭化珪素ウェハの主面に平行な面内における素子特性のばらつきを抑えて、歩留まりを向上させる。

【解決手段】

本発明の炭化珪素半導体素子の製造方法は、(A)炭化珪素ウェハ101と、炭化珪素ウェハ101の主面上に配置され、第1導電型の不純物を含む複数の第1導電型不純物領域105を有する第1炭化珪素層110とを備えた炭化珪素層付ウェハ1を用意する工程と、(B)第1炭化珪素層110の表面に炭化珪素をエピタキシャル成長させることによって、第2炭化珪素層115を形成する工程とを包含し、工程(B)において、複数の第1導電型不純物領域105の表面における第1導電型の不純物の濃度分布に基づいて、炭化珪素ウェハ101の主面に平行な面内で、第2炭化珪素層115の厚さ、不純物濃度、またはその両方に分布をもたせるように、エピタキシャル成長させる条件を制御する。

(もっと読む)

炭化珪素単結晶の製造装置および製造方法

【課題】SiC単結晶の製造装置に備えられる断熱材の劣化を抑制することができるようにする。

【解決手段】加熱容器8の周囲を囲む第1外周断熱材10を、浸透性の大きな断熱基材10aの内周面に浸透性の小さな黒鉛シート10bを配置した構造とし、さらに黒鉛シート10bの内周面を高融点金属炭化膜10cで覆った構造とする。これにより、黒鉛シート10bによって断熱基材10aに原料ガス3などが浸入することで固体SiCが析出することを抑制しつつ、さらに高融点金属炭化膜10cによって黒鉛シート10bがエッチングガスや原料ガス3に含まれる成分と化学反応することを抑制できる。したがって、第1外周断熱材10が劣化することを抑制することが可能となる。

(もっと読む)

へテロ接合トランジスタ及びその製造方法

【課題】チャネル層中のキャリア濃度を増すため、高いアルミニウム含有率を有した厚いAlGaN層は、成長中か冷却後にひびが入る傾向があり、これによってデバイスが破壊される。

【解決手段】基板上の第1のIII族窒化物層は第1の歪みを有する。GaN層のような第2のIII族窒化物層が、第1のIII族窒化物層上に設けられている。第2のIII族窒化物層は、第1のIII族窒化物層のバンドギャップよりも小さなバンドギャップを有し、かつ第1の歪みの大きさよりも大きい第2の歪みを有する。AlGaN層又はAlN層のような第3のIII族窒化物層がGaN層上に設けられている。第3のIII族窒化物層は、第2のIII族窒化物層のバンドギャップよりも大きなバンドギャップを有し、かつ第2の歪みと逆の歪みの型の第3の歪みを有する。ソースコンタクトとドレインコンタクトとゲートコンタクトを第3のIII族窒化物層上に設ける。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜上に保護膜を形成した構造において、絶縁耐圧の低下を防ぐ。

【解決手段】基板上に形成された第1の半導体層と、前記第1の半導体層上に形成された第2の半導体層と、前記第2の半導体層上に形成されたソース電極及びドレイン電極と、前記第2の半導体層上に形成された絶縁膜と、前記絶縁膜上に形成されたゲート電極と、前記絶縁膜を覆うように形成された保護膜と、を有し、前記保護膜は、熱CVD、熱ALD、真空蒸着のいずれかにより形成されたものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】本発明は、トランジスタ特性の再現性が高く、高速でパワーの大きい電界効果トランジスタ及びその製造方法を提供することを課題とする。

【解決手段】ダイヤモンド基板11と、前記ダイヤモンド基板11の一面11a側に離間して形成された第2の電極13及び第3の電極14と、2つの電極13、14の間に離間して形成された第1の電極15と、を有する電界効果トランジスタであって、第1の電極15とダイヤモンド基板11との間にIII族窒化物半導体層12が設けられ、ダイヤモンド基板11とIII族窒化物半導体層12との界面17の近傍領域に正孔伝導チャネル領域16が形成されている電界効果トランジスタ10を用いることによって前記課題を解決できる。

(もっと読む)

半導体装置の製造方法

【課題】 ピンチオフ特性を改善しまたはチャネル層の移動度を向上させ電気的特性の良好な半導体装置の製造方法を提供すること。

【解決手段】基板10上にGaN系半導体層20を形成する工程と、前記GaN系半導体層に開口部28を形成する工程と、前記開口部の側面に電子走行層22および電子供給層26を形成する工程と、前記電子供給層の前記開口部側の側面にゲート電極32を形成する工程と、前記GaN系半導体層上にソース電極30を形成する工程と、前記GaN系半導体層の前記ソース電極と相対する面に接続するドレイン電極34を形成する工程と、を具備する半導体装置の製造方法。

(もっと読む)

炭化珪素半導体素子の製造方法及び電子デバイスの製造方法

【課題】炭化珪素とその上に形成される絶縁膜との界面の品質及び当該絶縁膜の品質を改善して界面準位密度を低減することができる炭化珪素半導体素子の製造方法及び電子デバイスの製造方法を提供する。

【解決手段】炭化珪素基板1の主表面を、水素ガスを含むクリーニングガスで表面処理し、前記主表面を窒素含有ガスで表面処理し、前記主表面上に絶縁膜2を形成する。

(もっと読む)

被処理体の加熱冷却方法

【課題】特に真空処理装置において、被処理体を破損することなく略均一に被処理体を加熱できるようにした被処理体の加熱冷却方法を提供する

【解決手段】基板ステージ2に設けた正負一対の吸着電極14a乃至14d間に所定の電圧を印加して基板Wを静電吸着し、基板ステージ2に組み込んだ加熱手段または冷却手段により基板を所定の温度に加熱または冷却する。基板の温度が所定の温度に達するまでの間に、この吸着電極の印加電圧を三角パルス状に変化させ、この印加電圧が低くなるときに吸着電極と被処理体とを実質的に縁切りする。

(もっと読む)

ナノワイヤデバイスの製造方法

【課題】半導体の接合や商品設計の面で優れた自由度を得ることができるナノワイヤデバイスの製造方法を提供する。

【解決手段】半導体基板1の表面に、結晶をエピタキシャル成長させて複数のナノワイヤ状半導体2を形成する。ナノワイヤ状半導体2の間隙に充填剤5を充填してナノワイヤ状半導体2を埋設し、ナノワイヤ状半導体−充填剤複合体6を形成する。半導体基板6から、ナノワイヤ状半導体−充填剤複合体6を剥離して、ナノワイヤ状半導体アレイ9,10,11,13,14,15を形成する。ナノワイヤ状半導体−充填剤複合体6の剥離は、充填剤5上に支持基板8を形成した後、外力により行う。又は、充填剤5の熱収縮応力によりナノワイヤ状半導体−充填剤複合体6を剥離した後、充填剤5上に支持基板8を形成する。

(もっと読む)

熱処理装置

【課題】SiCを高温アニールするような場合であっても、低熱容量で且つ均一加熱が可能な熱処理装置を提供する。

【解決手段】熱処理装置において、平行平板電極2、3と、これら電極間に高周波電圧を印加し放電させる高周波電源6と、これら電極間に配置される被加熱試料1の温度を計測する温度計測手段17と、これら電極間へのガス導入手段10と、これら電極の周囲を覆う反射鏡13と、高周波電源6の出力を制御する制御部18を備える。これら電極間での放電によるガス加熱を用いて被加熱試料1の熱処理を行う。

(もっと読む)

SiCエピタキシャルウェハ

【課題】三角欠陥及び積層欠陥が低減され、キャリア濃度及び膜厚の均一性が高く、ステップバンチングフリーのSiCエピタキシャルウェハを提供する。

【解決手段】本発明のSiCエピタキシャルウェハは、0.4°〜5°のオフ角で傾斜させた4H−SiC単結晶基板上にSiCエピタキシャル層を形成したSiCエピタキシャルウェハであって、前記SiCエピタキシャル層の表面の三角形状の欠陥密度が1個/cm2以下であることを特徴とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】容量増加による高周波特性の劣化及び裏面電極に起因する絶縁破壊を抑止し、チップ面積を増加させることなく、インパクトイオン化により生成したホールを容易且つ確実に引き抜いて排出することを可能として、高耐圧性及び高信頼性を実現する化合物半導体装置及びその製造方法を提供する。

【解決手段】絶縁性又は半絶縁性の基板1の表面に電子走行層3、電子供給層4が形成され、電子供給層4内には局所的なp型領域7が形成されており、基板1の裏面にp型領域7の一部を露出させる開口1aが形成され、開口1aを導電材料で埋め込みp型領域7とオーミック接続された裏面電極8を備え、AlGaN/GaN・HEMTが構成される。

(もっと読む)

オフ角を有する単結晶基板の製造方法

【課題】単結晶の気相合成において利用できるオフ基板の製造に際して、製造コストを削減でき、且つ同一のオフ角を有する基板を簡単かつ大量に製造することが可能な新規な方法を提供する。

【解決手段】気相合成法による半導体ダイヤモンド等のエピタキシャル成長が可能な材料であって、その表面が、エピタキシャル成長が可能な結晶面に対してオフ角を有する材料を基板として用い、該基板にイオン注入を行って、基板の表面近傍に結晶構造の変質した層を形成し、気相合成法によって該基板上に結晶成長を行い、次いで、成長した結晶層と基板とを分離させて得られた結晶層を基板として用い、該基板にイオン注入を行って、基板の表面近傍に結晶構造の変質した層を形成し、気相合成法によって該基板上に結晶成長を行い、成長した結晶層と基板とを分離させることを特徴とする、オフ角を有する単結晶基板の製造方法。

(もっと読む)

半導体製造装置

【課題】SiCエピタキシャル成長過程でサセプタに付着した膜を除去し、製造歩留まりを向上させることのできる半導体製造装置を提供する。

【解決手段】サセプタSに載置されるウェハW上にSiCエピタキシャル膜を形成する成膜室2と、サセプタSが搬送される搬送用ロボット17を有する搬送室4を介して成膜室2に連結され、サセプタSに付着したSiC膜を除去するクリーニング室5とを有する。クリーニング5室は、サセプタSを400℃以上の温度で加熱するヒータ208と、サセプタSの上方からエッチングガスを供給してSiC膜を除去するエッチングガス供給手段とを備える。クリーニング室5は、サセプタSの表面にSiC膜を形成する再生室を兼ねる。

(もっと読む)

アモルファスカーボン及びその製造方法

【課題】欠陥密度の低いアモルファスカーボン及びその製造方法を提供すること。

【解決手段】本発明に係るアモルファスカーボンは、フッ素濃度が5×10−5〜3%(atm)であり、少量のフッ素原子を導入したフッ素化アモルファスカーボンである。これにより、アモルファスカーボン中の欠陥数を減少させることができ、欠陥密度の低いアモルファスカーボンが実現可能となる。

(もっと読む)

窒化物系化合物半導体および窒化物系化合物半導体素子

【課題】長期信頼性が高い窒化物系化合物半導体および窒化物系化合物半導体素子を提供すること。

【解決手段】アルミニウム原子、ガリウム原子、インジウム原子およびボロン原子から選択される1以上のIII族原子と、窒素原子とを含む窒化物系化合物半導体であって、添加物としてリチウム、銅、銀、または金を含む。好ましくは、前記添加物のドープ濃度は、ガリウム格子間原子の濃度と同程度である。好ましくは、前記添加物のドープ濃度は、5×1016cm−3〜5×1018cm−3である。

(もっと読む)

量子ドット形成方法及びこれを実施するためのプログラムを記憶する記憶媒体並びに基板処理装置

【課題】基板表面の構造に拘わらず,所望の位置に高精度で量子ドットを形成する。

【解決手段】定在波を有するレーザ光のレーザ光源Lを基板Wの側方に配置し,そのレーザ光を基板Wの側方からその基板の表面に沿うように照射させることによって,基板表面をそのレーザ光の定在波の半波長間隔で励起させる。その基板に対してその表面を構成する下地膜と格子定数の異なる膜を成長させることによって,上記レーザ光の照射により励起した部位Exに量子ドットが形成される。

(もっと読む)

窒化物系化合物半導体、窒化物系化合物半導体素子、およびその製造方法

【課題】長期信頼性が高い窒化物系化合物半導体、窒化物系化合物半導体素子、およびその製造方法を提供すること。

【解決手段】アルミニウム原子、ガリウム原子、インジウム原子およびボロン原子から選択される、少なくともガリウム原子を含むIII族原子と、窒素原子とを含む窒化物系化合物半導体であって、前記III族原子の格子間原子を拡散させる拡散促進物質を添加物としてドープしたものである。好ましくは、前記拡散促進物質はリン、砒素、またはアンチモンである。

(もっと読む)

半導体基板の製造方法および発光素子

【課題】 半導体の結晶性を向上させることが可能な半導体基板の製造方法を提供する。

【解決手段】 本発明の半導体基板の製造方法は、単結晶基板2の上に単結晶基板2を覆うように半導体層を結晶成長させた半導体基板の製造方法であって、平坦な上面4Aを有する複数の突起4が第1主面2Aに設けられた単結晶基板2を準備する工程と、複数の突起4のうち、上面4Aから半導体層3を結晶成長させるものを第1突起4aとし、第1突起4a同士の間に位置する、上面4Aに半導体層3を結晶成長させないものを第2突起4bとして、第2突起4bの上面4Aを被覆するように実質的に半導体層3が結晶成長しないマスク層5を形成する工程と、第1突起4aの上面4Aからそれぞれ第2突起4bの上面4Aのマスク層5を越えて単結晶基板2を覆うように半導体層3を結晶成長させる工程とを有する。そのため、単結晶基板2上に成長させる半導体層3の単結晶基板2に対する平坦性を向上させることができ、半導体層3の結晶性を向上させることができる。

(もっと読む)

141 - 160 / 715

[ Back to top ]