Fターム[5F045DA52]の内容

気相成長(金属層を除く) (114,827) | 半導体成長層の構造 (3,415) | 半導体成長層の形状、構造 (2,125) | 多層成長層 (2,091)

Fターム[5F045DA52]の下位に属するFターム

バッファ層・中間層・遷移層を有するもの (1,084)

超格子(歪超格子、変調ドープ超格子を含む) (99)

量子井戸 (345)

量子細線・量子箱 (31)

Fターム[5F045DA52]に分類される特許

461 - 480 / 532

2元のIII族窒化物をベースとする高電子移動度トランジスタおよびその製造方法

2元のIII族窒化物高電子移動度トランジスタ(HEMT)と2元のIII族窒化物HEMTを作製する方法が提供される。いくつかの実施例では2元のIII族窒化物HEMTは第1の2元のIII族窒化物バリヤ層と、第1のバリヤ層上の2元のIII族窒化物チャネル層と、およびチャネル層上の第2の2元のIII族窒化物バリヤ層を含む。いくつかの実施例では2元のIII族窒化物 HEMTは第1のAlNバリヤ層と、GaNチャネル層と、および第2のAlNバリヤ層とを含む。  (もっと読む)

(もっと読む)

エピタキシャル基板およびそれを用いた半導体装置並びにその製造方法

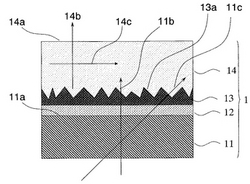

【課題】窒化物系レーザダイオードの低閾値化、窒化物系半導体発光ダイオードの高効率化、エンハンスメント型窒化物系半導体電界効果トランジスタの実現のためには、R面サファイア基板上に成長すれば可能であるが、従来技術では、表面平坦性や多数の欠陥が入る問題があり、また、その結晶性を向上させる方法として、選択横方向成長という方法があるが、コスト、量産性の面で大きな問題があった。

【解決手段】R面サファイア基板上に作製した窒化物系半導体に、歪を導入することおよび成長条件を最適化することによって、結晶成長中に自発的に周期10nmから10μm、高さ10nmから10μmの凹凸を形成し、その後平坦化することにより貫通転位密度、積層欠陥密度の低減が可能であり、且つ、表面平坦性の良好な半導体基板の作製が低コストかつ簡便に作製可能であり、また、この基板を用いること。

(もっと読む)

高機能粒子構造を有する多結晶膜の堆積方法

多結晶Si含有膜の粒子構造を制御するための方法は、最初の段階で堆積される第1の膜層のモフォロジーが、後の段階で堆積される第2の膜層のモフォロジーに有利に作用するような、膜を段階的に堆積するステップを含む。例示する実施形態では、最初の段階は、アニーリングするステップを含む。別の実施形態では、後の段階は、第1の層用とは異なる堆積条件下で第2の層を堆積するステップを含む。  (もっと読む)

(もっと読む)

(Al,In,Ga)N薄層を作製するためのエッチング技術

(Al,In,Ga)N薄層を製作するためのエッチング技術であり、適当なテンプレートまたは基板が選択されて、所望の面積上に異種イオンが注入されてイオン注入された材料を作る。次に、イオン注入されたテンプレートまたは基板の上にデバイス構造が再成長される。テンプレートの成長表面上面がキャリアウェーハにボンディングされて、ボンディングされたテンプレート/キャリアウェーハからなる構造を形成する。ほかの残留する材料と一緒に基板が除去されて、イオン注入された材料が露出される。ボンディングされたテンプレート/キャリアウェーハからなる構造上のイオン注入された材料は、次に、イオン注入された材料を除去するのに十分な時間、適当なエッチャントに晒される。  (もっと読む)

(もっと読む)

窒化物半導体基板およびそれを用いた窒化物半導体素子

SiO2膜(2)の表面にAlN多結晶3をスパッタリング法により堆積させ、マスクを形成する。次いで、このマスクを形成した上にSiドープn−GaN層5を形成する。その後、Siドープn型Al0.1Ga0.9N(シリコン濃度4×1017cm−3、厚さ1.2μm)からなるn型クラッド層(6)、Siドープn型GaNからなるn型光閉じ込め層(7)、In0.2Ga0.8N井戸層とSiドープIn0.05Ga0.95Nバリア層からなる多重量子井戸層(8)、Mgドープp型Al0.2Ga0.8Nからなるキャップ層(9)、Mgドープp型GaNからなるp型光閉じ込め層(10)、Mgドープp型Al0.1Ga0.9Nからなるp型クラッド層(11)、Mgドープp型GaNからなるp型コンタクト層(12)を順次成長させて、LD層構造を形成する。  (もっと読む)

(もっと読む)

厚い半絶縁性または絶縁性エピタキシャル窒化ガリウム層およびそれを組み込んだデバイス

導電性半導体基板および/または導電層上の、半絶縁性または絶縁性GaNエピタキシャル層を備える半導体デバイス構造およびその半導体デバイス構造を作製する方法が提供される。半絶縁性または絶縁性GaNエピタキシャル層は、少なくとも約4μmの厚さを有する。導電性SiC基板および導電性SiC基板上の絶縁性または半絶縁性GaNエピタキシャル層を備えるGaN半導体デバイス構造ならびにそのGaN半導体デバイス構造を作製する方法も提供される。GaNエピタキシャル層は、少なくとも約4μmの厚さを有している。導電性GaN基板と、導電性GaN基板上の絶縁性または半絶縁性GaNエピタキシャル層と、GaNエピタキシャル層上のGaNベースの半導体デバイスと、GaNベースの半導体デバイスの層およびGaNエピタキシャル層を貫通するビアホールならびにビアホール内の対応するビアメタルとを備えるGaN半導体デバイス構造およびそのGaN半導体デバイス構造を作製する方法も提供される。  (もっと読む)

(もっと読む)

プラズマ成膜方法及び成膜構造

【課題】 基板上の成膜時間を短くするとともに、デバイスの特性低下を抑制すること。

【解決手段】 真空容器1内に高周波による電磁波を形成し、電磁波によって原料ガスのプラズマを発生させて、基板5上の成膜対象面に成膜を行なうプラズマ成膜方法において、電磁波をパルス状に形成するとともに、変調器16を用いて電極3のパルスの単位時間当たりのオン時間を膜厚方向で変更させるようにする。これにより、成膜によって形成される層間の界面を良好に保ち、デバイス特性の低下を抑制することができる。また、オン時間を適宜長くすることで、成膜時間を短縮することができる。

(もっと読む)

縦型窒化ガリウム半導体装置およびエピタキシャル基板

【課題】所望の低キャリア濃度を有するn−型窒化ガリウム膜をn型窒化ガリウム基板上に実現できる構造を有する縦型窒化ガリウム半導体装置のためのエピタキシャル基板を提供する。

【解決手段】窒化ガリウムエピタキシャル膜65は、窒化ガリウム基板63上に設けられている。層状領域67が、窒化ガリウム基板63および窒化ガリウムエピタキシャル膜65内に設けられている。窒化ガリウム基板43および窒化ガリウムエピタキシャル膜65の界面は層状領域67内に位置している。層状領域67では、窒化ガリウム基板63から窒化ガリウムエピタキシャル膜65へ向かう軸に沿ったドナー不純物が1×1018cm−3以上のピーク値である。ドナー不純物は、シリコンおよびゲルマニウムの少なくともいずれかである。

(もっと読む)

プラズマ処理装置

【課題】 高周波電極と給電線との間の電磁気的な干渉を弱くする、もしくは除去することができるプラズマCVD装置を提供する。

【解決手段】 外部から電力が供給される1つ以上の高周波電極4と、真空容器1の外部に配設された電力供給手段(機構7)と高周波電極4とを接続する1つ以上の給電線3とを有し、高周波電極4と給電線3との接触部は高周波電極4の中央付近であり、かつ、給電線3は直線状ではなく、真空容器1内において任意の形状をしており、電力が供給される高周波電極4に対して非対称な構造をしているプラズマCVD装置10aにおいて、給電線3と高周波電極4との間の電磁気的な干渉を弱くする、もしくは除去するシールド12aを真空容器1内に配置する。

(もっと読む)

異なるガス圧の領域を隔離するためのガス出入口

此処に開示されているのは、異なるガス組成及び/又は圧力の領域、特に大気と真空、を相互接続するための改良されたガス出入口である。ガス出入口は、異なるガス圧の領域間に在るハウジング内の円筒を含んでいる。基板材料の膜が、第一領域内の少なくとも一本のローラーと第二領域内の少なくとも一本のローラーを用いて、領域間を移動するように設計されている。ローラーは、膜が二領域間の円筒円周上部の上又は二領域間の円筒円周底部の下を進む時に、十分な張力を生ずるように配置されている。好ましい実施形態において、ガス出入口は、ハウジング上板と円筒の円周上部の上を進む基板膜との間の通路高さ、並びにハウジング底板と円筒の円周底部との間の通路高さによって特徴づけられる。そこを通るガスの流速は、円筒入口と相互接続された二領域の少なくとも一つとの間にガスの遷音速流をもたらし、従って遷音速流領域内における拡散成分の衝突間の平均自由行程を短くすることによって、一つの組成と圧力で特徴づけられる一方の領域を、異なる組成及び/又は圧力を有するもう一方の領域から効果的に隔離する。  (もっと読む)

(もっと読む)

固溶半導体発光素子用材料および発光素子

【課題】本発明は、紫外可視波長領域で発光し、波長可変で室温付近で動作する発光素子、特に格子整合型ダブルヘテロ接合構造、量子井戸構造および量子ドット構造の発光素子を製作可能な固溶半導体発光素子用材料および発光素子を提供する。

【解決手段】一般式 Ca1−x−yCdxYyX(但し、モル比で、0<x+y<1.0,0<x<1.0,0≦y≦0.1,X:S,SeおよびTeの少なくとも一種又は二種以上の元素、Y:I族、III族、V族およびVII族元素)で表される固溶半導体発光素子用材料およびそれらを用いた発光素子を、薄膜製造装置、例えば、ホットウォールエピタキシー装置を用いて成長を行う。なお、この際、基板として適当な基板、例えば、InPを用いる。成長終了後、固溶半導体発光材料の取り出しは、各部の温度が室温まで降下した後、真空槽内を適当なガス、例えば、窒素によりパージすることにより適当な形状の薄膜を製造する。

(もっと読む)

SiC半導体およびその製造方法

【課題】 表面の凹凸および反りが低減され、結晶性に優れた高品質な面方位(111)の3C−SiC単結晶薄膜を備えた半導体、および、Si単結晶基板上に、格子不整合を緩和し、かつ、エッチングを防止して、確実かつ容易に、面方位(111)の3C−SiC単結晶薄膜を形成することができるSiC半導体の製造方法を提供する。

【解決手段】 面方位(110)のSi単結晶基板1上に、有機化合物ガスを用いて、300Torr以下の減圧雰囲気下、780〜950℃で、水素が1019atoms/cm3以上含まれる3C−SiC低温成長層2を気相成長させた後、その上に面方位(111)の3C−SiC単結晶層3を形成することにより、SiC半導体を得る。

(もっと読む)

多層のエピタキシャルシリコン単結晶ウェーハの製造方法及び多層のエピタキシャルシリコン単結晶ウェーハ

【課題】スリップ転位が無く、高抵抗率のウェーハや、直径が300mm以上のウェーハに対しても適用可能な多層のエピタキシャルシリコン単結晶ウェーハの製造方法および多層のエピタキシャルシリコン単結晶ウェーハを提供する。

【解決手段】多層のエピタキシャルシリコン単結晶ウェーハの製造方法であって、少なくともチョクラルスキー法によって窒素をドープしたシリコン単結晶棒を育成し、該シリコン単結晶棒をスライスしてシリコン単結晶ウェーハに加工した後、該シリコン単結晶ウェーハの表層部に一層目のエピタキシャル層を形成し、その後、少なくとも、該一層目のエピタキシャル層の表層部に二層目のエピタキシャル層を形成する多層のエピタキシャルシリコン単結晶ウェーハの製造方法。

(もっと読む)

窒化物半導体材料および窒化物半導体結晶の製造方法

【課題】下地に発生した転位をその上に形成する窒化物半導体層に伝播させずに、均一性と安定性に優れた窒化物半導体材料を提供する。

【解決手段】サファイア基板(0001)面上に、MOVPE装置でGaN膜を極性が揃う程度の膜厚(約3μm)で製膜した。その表面にP−CVD法によりSiNx膜を約100nm製膜し、開口部とマスク部の面積比がそれぞれ1:5になるように周期的なストライプ状のマスクを形成した。 そのウェハーをHVPE装置に投入し、ガスが流れてくる方向とウェハー表面の法線との角度が80°となるように設置し、1050℃でGaNを成長させた。ウェハーの断面をTEMで観察した結果、第一窒化物半導体層のGaNの転位(欠陥)が第二窒化物半導体層に伝播していないことが確認された。

(もっと読む)

化合物半導体エピタキシャル結晶及びその成長方法

【課題】 p型伝導層をC添加のInGaAsを主成分とする化合物半導体層で構成したエピタキシャル結晶であって、p型伝導層の結晶性及びpn接合の急峻性に優れ、HBT等の電子デバイス用基体として有用なエピタキシャル結晶を提供する。

【解決手段】 化合物半導体基板上に、p型不純物として炭素が添加されたInGaAsを主成分とするp型伝導層を含む複数のエピタキシャル層が積層された化合物半導体エピタキシャル結晶において、前記p型伝導層がアンチモンを0.5〜10モル%含有するようにした。

(もっと読む)

III族窒化物系化合物半導体素子の製造方法

【課題】アクセプタ不純物の添加された、少なくともアルミニウムを含むIII族窒化物系化合物半導体層の結晶性の向上。

【解決手段】サファイヤ基板101の上に、順にAlNから成るバッファ層102、ノンドープのGaNから成る層103、シリコン(Si)をドープしたGaNから成るn型コンタクト層104、多重層105、ノンドープGaNから成る障壁層1062とノンドープIn0.2Ga0.8Nから成る井戸層1061がくり返し形成された多重量子井戸層からなる発光層106、Mgをドープしたp型Al0.2Ga0.8Nから成るp型層107、ノンドープのAl0.02Ga0.98Nから成る層108、Mgをドープしたのp型GaNから成るp型コンタクト層109を形成した。p型層107を窒素と水素の混合ガス(窒素濃度40〜80%)下でエピタキシャル成長させることで光強度が向上した。

(もっと読む)

光起電力装置

【課題】出力特性を向上させることが可能な光起電力装置を提供する。

【解決手段】この光起電力装置は、n型層3と、n型層3上に形成された光電変換層4と、光電変換層4上に形成されたp型層5とを有する発電ユニットを含んでいる。そして、n型層3は、非晶質Si層であり、光電変換層4およびp型層5は、微結晶Si層であるとともに、光電変換層4およびp型層5は、それぞれ、(220)面および(111)面の優先結晶配向を有する。

(もっと読む)

III−V族窒化物半導体及びその製造方法

【課題】炉内付着物からGaやNラジカルの発生が起こってもSi基板表面を劣化させず、さらにはスループットを落すことなく良質なIII−V族窒化物半導体薄膜を実現すること。

【解決手段】加熱したSi基板上に複数のIII族元素またはV族元素を含む原料ガスを供給し、熱分解反応させてIII−V族窒化物半導体を成長させるIII−V族窒化物半導体の製造方法において、Si元素を含む原料ガスを供給しながらSi基板1を加熱することにより、Si基板1上にSiを成長しつつSi基板1を昇温し、その後にIII−V族窒化物半導体、例えばAlN層2の成長を行う。

(もっと読む)

エピタキシャル半導体基板の製造方法及び半導体装置の製造方法

【課題】本発明は、ゲッタリング能力が向上したエピタキシャル半導体基板の製造方法を提供する。また、本発明は、動作特性が向上した半導体装置の製造方法を提供する。

【解決手段】エピタキシャル半導体基板を製造する方法の一実施形態で、ゲッタリング層は半導体基板上に成長される。その後、エピタキシャル層が前記ゲッタリング層上に形成されることができて、半導体装置が前記エピタキシャル層上に形成されることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】シリコン単結晶基板上に完全に転位をなくした(無欠陥の)III −V族化合物半

導体層を形成することを目的とする。

【解決手段】シリコン単結晶基板1と、シリコン単結晶基板1上にその臨界膜厚以下の厚さに形成されたGaPバッファ層2と、GaPバッファ層2上に形成されシリコン単結晶に実質的に格子整合するように窒素(N)をV族元素に対して1%〜10%添加したIII −V族化合物半導体からなる複数の半導体層3とを有する。

(もっと読む)

461 - 480 / 532

[ Back to top ]