Fターム[5F045HA13]の内容

気相成長(金属層を除く) (114,827) | 他プロセスとの組合せ (2,158) | 後処理(膜形成が先) (953) | エッチング (308) | ドライエッチ (171)

Fターム[5F045HA13]に分類される特許

1 - 20 / 171

シリコン膜の形成方法及び半導体装置の製造方法

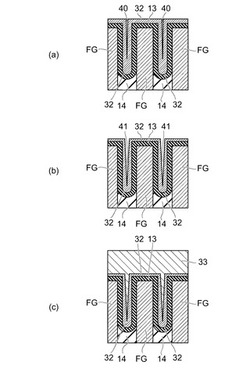

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

(もっと読む)

窒化物半導体発光素子及びその製造方法

【課題】

高抵抗領域と低抵抗領域が隣接して形成されると、境界部に電流集中が生じる。

【解決手段】

窒化物半導体発光素子は、基板と、基板上に配置され、p型層、活性層、n型層を含む窒化物半導体積層と、p型層と基板との間に形成されたp側電極と、n型層上の限定された領域に形成されたn側電極と、n側電極に対向する領域を含んで、p型層内、またはp型層表面に形成され、実質的に電流を流さない高抵抗領域と、高抵抗領域外側のp型層に形成され、p側電極との間に電流を流す低抵抗領域と、高抵抗領域と低抵抗領域の間に形成され、制限された電流を流すグレーデッド領域と、を有する。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】閾値電圧のばらつきを低減できる炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置10は、基板11と、基板11上に設けられ、主表面13Aと、主表面13Aと交差する厚さ方向とを有する炭化珪素層4とを含む。炭化珪素層4は、チャネル層7と、ソース領域15と、ドレイン領域17と、ソース領域15とドレイン領域17との間において、ゲート領域16Rとを含む。ゲート領域16Rはチャネル層7に対して、第1の導電型と異なる第2の導電型を有するようにエピタキシャル成長されている。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

窒化物電子デバイス、窒化物電子デバイスを作製する方法

【課題】リーク特性のばらつき幅を低減可能な、窒化物電子デバイスを作製する方法を提供する。

【解決手段】テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた処理を行って半導体積層53bに第1処理面65fを処理装置10dで形成する。第1溶液による処理温度は、摂氏50度以上摂氏100度以下である。第1溶液の濃度は5パーセント以上であり、50パーセント以下である。第1処理工程に引き続き第2処理工程を行う。第2処理工程では、テトラメチルアンモニウムヒドロキシド処理の後に、フッ化水素酸及び過酸化水素を含む第2溶液を用いた処理を半導体積層53bに行って半導体積層53bに第2処理面65gを処理装置10eで形成する。第2処理工程の後において、半導体積層53bの処理面65gのドナー性不純物の濃度は5×1017cm−3以下である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された化合物半導体積層構造7と、化合物半導体積層構造上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、が設けられている。化合物半導体積層構造7には、電子走行層3と、電子走行層3上方に形成された電子供給層5を含む窒化物半導体層と、が設けられている。窒化物半導体層の表面のIn組成は、平面視でゲート電極11gとソース電極11sとの間に位置する領域及びゲート電極11gとドレイン電極11dとの間に位置する領域において、ゲート電極11gの下方よりも低くなっている。

(もっと読む)

シリコンと炭素を含有するインサイチュリンドープエピタキシャル層の形成

【課題】堆積速度が速く、好ましくは約700℃以下のような低いプロセス温度を維持し、置換型炭素濃度が高い、SiとCを含有する選択エピタキシャル層を得る方法を提供する。

【解決手段】基板上にSiとCを含有するエピタキシャル層を形成する方法であって、単結晶表面と、アモルファス表面、多結晶表面及びこれらの組み合わせより選ばれる少なくとも一つの第二表面とを含む基板をプロセスチャンバ内に配置するステップと、プロセスチャンバ内の圧力を少なくとも300トールに維持しつつ、該基板をシリコン源と、炭素源と、リン源にさらして、該基板の少なくとも一部にリンがドープされたSi:Cエピタキシャル膜を形成するステップと、700℃以下のプロセスチャンバ内の温度の下で、HClを含むエッチングガスに該基板をさらすことにより該基板を更に処理するステップと、を含む。

(もっと読む)

シリコン膜の形成方法およびその形成装置

【課題】ボイドやシームの発生を抑制することができるシリコン膜の形成方法およびその形成装置を提供する。

【解決手段】シリコン膜の形成方法は、第1成膜工程と、エッチング工程と、ドープ工程と第2成膜工程とを備えている。第1成膜工程では、被処理体の溝を埋め込むように不純物でドープされていないノンドープシリコン膜を成膜する。エッチング工程では、第1成膜工程で成膜されたノンドープシリコン膜をエッチングする。ドープ工程では、エッチング工程でエッチングされたノンドープシリコン膜を不純物でドープする。第2成膜工程では、ドープ工程でドープされたシリコン膜を埋め込むように、不純物がドープされたシリコン膜を成膜する。

(もっと読む)

成膜装置

【課題】エッチング耐性の高いアモルファスカーボン膜を提供する。

【解決手段】上部電極および下部電極が処理容器内に配設された平行平板型のプラズマCVD装置を用い、下部電極上に基板を配置する工程と、処理容器内に一酸化炭素および不活性ガスを供給するとともに、少なくとも上部電極に高周波電力を印加してプラズマを発生させることにより一酸化炭素を分解し、基板上にアモルファスカーボンを堆積して成膜する工程とを有する。上部電極が炭素電極であることが好ましい。

(もっと読む)

埋め込みヘテロ構造半導体レーザの製造方法及び埋め込みヘテロ構造半導体レーザ

【課題】耐圧特性を十分に維持しながら放熱特性を向上させることが可能な埋め込みヘテロ構造半導体レーザの製造方法等を提供する。

【解決手段】埋め込みヘテロ構造半導体レーザの製造方法は、半導体基板1上に半導体積層9とマスク層11を形成する工程と、マスク層11を用いて半導体構造物10をエッチングすることにより、第1方向に沿って延びる半導体メサ15であって、第1方向と直交する第2方向において被エッチング領域17と隣接する半導体メサ15を形成する工程と、マスク層11を半導体メサ15上に残した状態で、被エッチング領域17の第1領域17A1のみに埋め込み層19Aを形成する工程と、上部電極25を形成する工程と、を備える。上部電極25は、半導体メサ15の上面15Tから被エッチング領域17の第2領域17A2に亘って形成されることを特徴とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを十分に抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された化合物半導体積層構造2と、化合物半導体積層構造2上方に形成されたゲート電極3、及び平面視でゲート電極3を間に挟む2個のオーミック電極4a及び4bと、が設けられている。更に、ゲート電極3上方に形成され、ゲート電極3並びにオーミック電極4a及び4bから絶縁分離されたフィールドプレート6が設けられている。フィールドプレート6のオーミック電極4a及び4bを互いに結ぶ方向における少なくとも一方の端部は、平面視で、オーミック電極4a及び4bとゲート電極3との間に位置する。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 より平滑な表面を持ち、かつ、更なる薄膜化を達成することが可能なアモルファスシリコン膜の成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを供給し、下地2表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2表面のシード層3にアミノ基を含まないシラン系ガスを供給し、シード層3上にアモルファスシリコン膜4を、層成長する厚さに形成する工程と、層成長する厚さに形成されたアモルファスシリコン膜4をエッチングし、該アモルファスシリコン膜4の膜厚tを減ずる工程とを備える。

(もっと読む)

光集積素子の製造方法

【課題】バットジョイント構造を構成する第1及び第2の半導体積層部上に成長する半導体層に生じる結晶欠陥を低減する。

【解決手段】エッチングマスク30を用いて第1の半導体積層部20にエッチングを施す工程と、Alを含む光吸収層42、及び光吸収層42上に設けられるInPクラッド層44を有する第2の半導体積層部40を、エッチングマスク30を用いて選択的に成長させる第1の再成長工程と、エッチングマスク30を除去するマスク除去工程と、第1及び第2の半導体積層部20,40上に第3の半導体積層部を成長させる第2の再成長工程とを行う。第1の再成長工程において、InPに対してエッチング選択性を有するInP系化合物半導体を含むキャップ層46を第2の半導体積層部40上に更に成長させる。マスク除去工程の前に、エッチングマスク30上に生じたInP系堆積物Deを除去する。

(もっと読む)

半導体光素子の製造方法

【課題】過剰なエッチングを抑制するとともに半導体表面の突起物を除去する半導体光素子の製造方法を提供する。

【解決手段】半導体光素子の製造方法は、エッチストップ層13及び複数の半導体層を含み、半導体光素子のための半導体積層10を半導体基板11の主面11aにエピタキシャル成長させる半導体積層成長工程と、半導体積層10の最表面から突出する突起物の先端部が露出するように、最表面にマスク層を形成するマスク層形成工程と、マスク層を用いて、ウェットエッチングにより突起物をエッチングするウェットエッチング工程と、ウェットエッチングの後に、ドライエッチングにより突起物を除去するドライエッチング工程と、突起物を除去した後に、最表面からマスク層を除去するマスク層除去工程と、マスク層を除去した後に、半導体積層10に半導体光素子のための加工を行う加工工程と、を備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】大きなチャネル移動度を有する半導体装置及びその製造方法を提供する。

【解決手段】基板は、ポリタイプ4Hの六方晶の単結晶構造を有する半導体からなる表面SRを有する。基板の表面SRは、面方位(0−33−8)を有する第1の面S1と、第1の面S1につながりかつ第1の面S1の面方位と異なる面方位を有する第2の面S2とが交互に設けられることによって構成されている。ゲート絶縁膜は基板の表面SR上に設けられている。ゲート電極はゲート絶縁膜上に設けられている。

(もっと読む)

半導体発光素子の製造方法及び半導体発光素子用ウェーハ

【課題】成長用基板の剥離の際の半導体層の損傷を抑制した半導体発光素子の製造方法及び半導体発光素子用ウェーハを提供する。

【解決手段】実施形態によれば、凹凸が設けられた主面を有する第1基板の主面上に、発光層を含む窒化物半導体層を形成する工程と、窒化物半導体層と第2基板とを接合する工程と、第1基板を介して窒化物半導体層に光を照射して第1基板を窒化物半導体層から分離する工程と、を含む半導体発光素子の製造方法が提供される。窒化物半導体層を形成する工程は、凹凸の凹部の内壁面上に窒化物半導体層の少なくとも一部と同じ材料を含む薄膜を形成しつつ、凹部の内側の空間内に空洞を残すことを含む。分離する工程は、薄膜に光の少なくとも一部を吸収させて、窒化物半導体層のうちで凹部に対向する部分に照射される光の強度を、窒化物半導体層のうちで凹凸の凸部に対向する部分に照射される光の強度よりも低くすることを含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造において基板の金属汚染を抑える。

【解決手段】半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、前記半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む半導体装置の製造方法。

(もっと読む)

GaNHEMT装置用再成長ショットキー構造

【課題】高温で動作可能な高電子移動度トランジスタを提供する。

【解決手段】バッファ層16と、バッファ層16上のIII−V族層18と、III−V族層18上のソース接点20およびドレイン接点22と、III−V族層18上で、ソース接点20およびドレイン接点22間の再成長ショットキー層10と、成長ショットキー層10上のゲート接点24、を備える装置、および装置を用いたシステムを含む。さらに、装置とシステムの製造方法も含む。

(もっと読む)

半導体基板、半導体装置及びその製造方法

【課題】異種材料の基板上に形成した平坦かつ薄い半導体基板であって、異種材料の基板からの剥離が容易な半導体基板、半導体装置及びそれらの製造方法を提供すること。

【解決手段】本発明によると、第1の面に所定の間隔で配置した複数の半球状の凸部を有する基板と、前記基板の第1の面に形成した第1の半導体層と、を有することを特徴とする半導体基板が提供される。また、前記複数の半球状の凸部の表面積の合計と前記第1の面との比は1以上である。

(もっと読む)

発光ダイオード

【課題】格子欠陥が発生することを防止した発光ダイオードを提供する。

【解決手段】発光ダイオード10は、基板100と、第一半導体層120と、第二半導体層140と、活性層130と、第一電極150と、第二電極160と、を含む。第一半導体層、活性層、及び第二半導体層は、基板から離れる方向に沿って、基板に順次的に積層され、第一電極は、第一半導体層に電気的に接続され、第二電極は、第二半導体層に電気的に接続され、第一半導体層の基板と隣接する表面は、複数の空隙を含むパターン化されたカーボンナノチューブ層102である。第一半導体層のパターン化された表面が基板に接続することによって複数のキャビティが形成される。

(もっと読む)

1 - 20 / 171

[ Back to top ]