Fターム[5F048AB04]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 用途 (4,368) | 論理回路 (1,440) | インバータ回路 (545)

Fターム[5F048AB04]に分類される特許

61 - 80 / 545

半導体装置

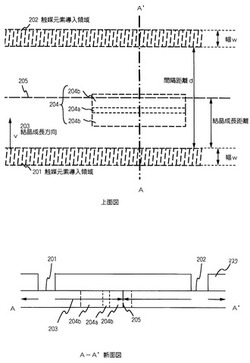

【課題】本願発明で開示する発明は、従来と比較して、さらに結晶成長に要する熱処理時間を短縮してプロセス簡略化を図る。

【解決手段】

一つの活性層204を挟んで二つの触媒元素導入領域201、202を配置して結晶化を行い、触媒元素導入領域201からの結晶成長と、触媒元素導入領域202からの結晶成長とがぶつかる境界部205をソース領域またはドレイン領域となる領域204bに形成する。

(もっと読む)

半導体デバイス及びその駆動方法

【課題】半導体デバイスの小面積化を実現する。

【解決手段】電極と、第1絶縁体と、バンドギャップが2eV以上の第1半導体と、第2絶縁体と、第2半導体とが積層されており、第1半導体に接する1つ以上の電極と、第2半導体に接する2つ以上の電極とを少なくとも備えることを特徴とする半導体デバイス。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

多結晶シリコン半導体素子及びその製造方法

【課題】多結晶シリコン半導体素子及びその製造方法を提供する。

【解決手段】ゲート共通化ラインに存在するシリコン物質層による寄生キャパシタンスを減少させるために、製造工程中にゲート以外の他の部分の不要なシリコン物質を除去する。シリコン物質層は、ゲートの下部のみに局地的に存在し、したがって、寄生キャパシタンスの減少によって信号遅延が抑制されて良好な電気的特性を有する薄膜トランジスタの多結晶シリコン半導体素子が得られる。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】集積回路のコア部のロジックトランジスタ(MOSFET、MISFET)は、世代が進むごとに動作電圧をスケーリングすることで微細化が可能である。しかし、高耐圧部のトランジスタ(MOSFET、MISFET)は比較的高い電源電圧で動作するために縮小化が困難であり、同様に電源セル内の静電気放電(ESD)保護回路は、静電気(外来サージ)から半導体集積回路内の素子を保護するために耐圧が高いことが必須であり、電荷を逃がすために大面積である必要がある。従って、集積回路の微細化のためには、微細化が可能なトランジスタ構造が必須である。

【解決手段】本願発明は、ソース側にのみハロー領域を有するソースドレイン非対称構造の一対のMISFETから構成されたCMISインバータをESD保護回路部に有する半導体集積回路装置である。

(もっと読む)

半導体装置の製造方法

【課題】前工程においてトランジスタごとに不純物の種類や量を変えることによる、製造コストや製造時間の増大を抑制する。

【解決手段】本発明による半導体装置の製造方法は、第1の閾値電圧及び第1のドレイン・ソース間電流を呈するようなデバイスパラメータをもって設計された第1のトランジスタを含む半導体回路を形成する半導体回路形成工程(ステップS11)と、第1のトランジスタにストレス電圧を印加して第1の閾値電圧とは異なる第2の閾値電圧及び前記第1のドレイン・ソース間電流とは異なる第2のドレイン・ソース間電流の少なくとも一方を第1のトランジスタが呈するようにする特性制御工程(ステップS14)と、第1のトランジスタが第2の閾値電圧及び第2のドレイン・ソース間電流の少なくとも一方を呈する状態で出荷する出荷工程(ステップS16)とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】動作マージンの向上に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板上に、互いのゲート電極が接続されて配置される第1トランジスタ(P2)と、前記第1トランジスタと異なる導電型を有する第2トランジスタ(N4)とを具備し、前記第1トランジスタのゲート電極は、第1不純物と前記第1不純物の拡散を抑制する第2不純物とを含有し、前記第1不純物の濃度ピーク(PE1)は、前記第2不純物の濃度ピーク(PE2)よりも浅い位置に形成されている。

(もっと読む)

CMOS回路及び半導体装置

【課題】しきい電圧VTが小さくてもリーク電流が小さく、また高速にかつ小さな電圧振幅で動作するCMOS回路さらには半導体装置を提供することである。

【解決手段】ゲートとソースを等しい電圧にしたときにドレインとソース間に実質的にサブスレショルド電流が流れるようなMOST(M)を含む出力段回路において、その非活性時には、前記MOST(M)のゲートとソース間を逆バイアスするように該MOST(M)のゲートに電圧を印加する。すなわち、MOST(M)がpチャンネル型の場合にはp型のソースに比べて高い電圧をゲートに印加し、また、MOST(M)がnチャンネル型の場合にはn型のソースに比べて低い電圧をゲートに印加する。活性時には、入力電圧に応じて該逆バイアス状態を保持するかあるいは順バイアス状態に制御する。

(もっと読む)

半導体装置、半導体集積回路装置、SRAM、Dt−MOSトランジスタの製造方法

【課題】Dt−MOSトランジスタよりなる半導体装置の素子寸法を縮小する。

【解決手段】シリコン基板21と、素子分離領域21Iと、前記素子分離領域により画成された、第1の導電型を有する第1のウェルよりなる素子領域21DNWと前記第1の導電型と逆の第2の導電型のコンタクト領域21P+1と、ゲート絶縁膜を介して、前記素子領域上から、前記素子分離領域のうち前記素子領域と前記コンタクト領域との間に延在するゲート電極と、第2の導電型のソース拡散領域と、第2の導電型のドレイン拡散領域と、前記ソース拡散領域の下端部に接して形成された第1の絶縁領域と、前記ドレイン拡散領域の下端部に接して形成された第2の絶縁領域と、前記ゲート電極と前記コンタクト領域とを電気的に接続するビアプラグと、を含み、前記第1のウェルは前記素子分離領域部分の下の前記シリコン基板を介して前記コンタクト領域に電気的に接続されていること。

(もっと読む)

半導体装置およびその製造方法

【課題】集積性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1と、半導体基板1上に設けられた埋め込み絶縁膜2と、埋め込み絶縁膜2上に設けられた第1の薄膜FET100と、第1の薄膜FET100と隣接して埋め込み絶縁膜2上に形成された第2の薄膜FET101と、第1の薄膜FET100直下の半導体基板1内に設けられた第1ウェル領域4と、第2の薄膜FET101直下の半導体基板1内に設けられた第2ウェル領域5と、を備え、第1ウェル領域4から第2ウェル領域5までの距離が、第1の薄膜FET100から第2の薄膜FET101までの距離よりも大きい。

(もっと読む)

半導体装置

【課題】従来よりも低消費電力かつ小面積であるとともに設計性のよいパワーオンリセット回路またはスタートアップ回路を備えた半導体装置を提供する。

【解決手段】半導体装置1は、出力部10と、第1および第2の電位設定部8,9とを備える。出力部10は、電源投入時に、中間電位ノードN1の電位に応じた制御信号RSを内部回路3に出力する。第1の電位設定部8は、第1の基準電位ノードVDDと中間電位ノードN1との間に接続された第1の導電型を有するエンハンスメント型の第1のMOSトランジスタEPを含む。第2の電位設定部9は、第2の基準電位ノードGNDと中間電位ノードN1との間に直列接続された第2の導電型を有するディプレッション型の複数の第2のMOSトランジスタDN1_〜DN_nを含む。複数の第2のMOSトランジスタDN1_〜DN_nの各々において、ソースとウェルとが互いに接続される。

(もっと読む)

半導体装置、並びに、半導体装置の製造方法及び駆動方法

【課題】絶縁層上に形成された部分空乏型のトランジスターにおいて、ヒストリー効果を低減し、なおかつ高いON/OFF比、及び急峻なサブスレッショルド特性を実現する。

【解決手段】絶縁層上の半導体層に形成された第1導電型のソース領域、第1導電型のドレイン領域、及び、第2導電型のボディ領域と、第1ゲート絶縁膜と、第1ゲート電極と、を含む部分空乏型の第1トランジスターと、絶縁層上の半導体層に形成された第1ダイオードと、を具備し、第1ダイオードは、第1導電型の第1不純物領域と、第1不純物領域上に形成された第2導電型の第2不純物領域と、を含み、第1トランジスターのボディ領域は、第1ダイオードの第1不純物領域及び第2不純物領域に接続されている。

(もっと読む)

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

半導体装置

【課題】低電位領域と高電位の配線が交差することの無い優れた耐圧性能を示す半導体装置を提供することを課題とする。

【解決手段】本発明の半導体装置は、ロジック回路(501)と、ロジック回路からの制御信号に従い低電位側パワー素子を駆動する低電位側駆動回路(502)と、ロジック回路からの制御信号がレベルシフト回路を介して入力され、高電位側パワー素子(506)を駆動する高電位側駆動回路(505)と、複数に重なったトレンチ分離領域により、前記高電位側パワー素子を含む高電位島を分離する多重トレンチ分離領域(508)と、を有する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】LSI中の高耐圧MOSFETを含む高耐圧回路は、純粋な内部回路と異なり、外部との関係で動作電圧が高い状態で固定されているため、通常のように、低電圧化による微細化が適用できない。このため、内部回路部の低電圧化に伴って、ますます、チップ内の占有面積を肥大化させる結果となっている。この問題について、本願発明者等が、各種の対策について評価したところによると、CMOSFET回路構成およびデバイス構成との適合性等の問題がネックとなっていることが明らかとなった。

【解決手段】本願発明は、各チャネル表面に波状起伏が設けられたNチャネル型およびPチャネル型MISFETを有する半導体集積回路装置において、Pチャネル型MISFETのチャネル表面に設けられた波状起伏に比べて、Nチャネル型MISFETのチャネル表面に設けられた波状起伏のピッチを狭くしたものである。

(もっと読む)

パルス変換回路

【課題】回路面積を低減する。

【解決手段】第1の信号が入力され、第2の信号を出力する論理回路を具備し、論理回路は、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧に設定するか否かを制御するP型トランジスタと、エンハンスメント型であり、閾値電圧の絶対値がP型トランジスタより大きく、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧より高い第2の電圧に設定するか否かを制御するN型トランジスタと、を備え、P型トランジスタは、チャネルが形成され、第14族の元素を含有する半導体層を含み、N型トランジスタは、チャネルが形成され、キャリア濃度が1×1014/cm3未満である酸化物半導体層を含む。

(もっと読む)

半導体装置

【課題】ラッチ回路を有する半導体装置におけるデータの破壊を抑制する。

【解決手段】ラッチ回路に含まれる第1トランジスタP4と、ラッチ回路に含まれ、第1トランジスタP4と共通のウェル40内に形成された、第1トランジスタP4と同じ導電型の第2トランジスタP1と、第1トランジスタP4と第2トランジスタP1との間に設けられ、ウェル40を電源に接続するウェルコンタクトWCと、を備える。第1トランジスタP4側のウェル40内で発生した電荷は、ウェルコンタクトWCに流れるため、第1トランジスタP4におけるソフトエラーの影響が、第2トランジスタP1に伝搬することを抑制することができる。これにより、ラッチ回路内における2箇所のノードにおいて、同時に論理の反転が生じることを抑制することができるため、データの破壊を抑制することができる。

(もっと読む)

電力用半導体装置

【課題】消費電力を低減することができる電力用半導体装置を得る。

【解決手段】高耐圧ダイオードDBによりコンデンサCBを充電してハイサイド駆動回路10aの駆動電圧を得る電力用半導体装置において、高耐圧ダイオードDBは、P−型半導体基板12と、P−型半導体基板12の表面に設けられたN型カソード領域14と、N型カソード領域14内に設けられたP型アノード領域16と、P型アノード領域16内に設けられたP+型コンタクト領域20及びN+型コンタクト領域22と、N型カソード領域14に接続されたカソード電極24と、P+型コンタクト領域20及びN+型コンタクト領域22に接続されたアノード電極26とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

61 - 80 / 545

[ Back to top ]