Fターム[5F048BB07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | 多結晶Si (4,558) | P型ドープ多結晶Si (956)

Fターム[5F048BB07]に分類される特許

81 - 100 / 956

半導体装置及びその製造方法

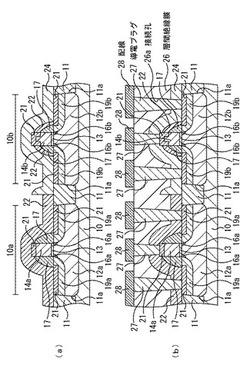

【課題】N型トランジスタ及びP型トランジスタの双方で可及的に製造工程を共通にして、工程数の可及的な削減を図るも、N型トランジスタ及びP型トランジスタの夫々に適合した応力を適宜印加し、トランジスタ性能の大幅な向上を実現する。

【解決手段】N型トランジスタでは、ゲート電極14a及びサイドウォール絶縁膜17を覆うようにN型領域10aの全面に引張応力膜22を形成し、P型トランジスタでは、サイドウォール17絶縁膜上のみに引張応力膜22を形成し、更にゲート電極14b及び引張応力膜22を覆うようにP型領域10bの全面に圧縮応力膜24を形成する。

(もっと読む)

半導体回路装置の製造方法

【課題】MOSトランジスタ、容量素子を有する半導体装置の製造コストを削減できる製造方法を提供する。

【解決手段】MOSトランジスタのゲート電極が第1のポリシリコン膜から成り、容量が第1のポリシリコン膜と容量膜と第2のポリシリコン膜から成り、ノーマリーオフトランジスタと容量下部電極の低抵抗化を同時に行い、N型MOSトランジスタと容量上部電極の低抵抗化を同時に行うことを特徴とする半導体回路装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されたMISFETのゲート電極の加工精度を向上することができる技術を提供する。

【解決手段】シリコン上にニッケルプラチナ合金膜を形成する(S101)。そして、第1加熱処理を実施する(S102)。このとき、第1加熱処理において、加熱温度は250℃〜270℃であり、加熱時間は30秒未満である。続いて、未反応のニッケルプラチナ合金膜を除去する(S103)。その後、第2加熱処理を実施する(S104)。このとき、第2加熱処理において、加熱温度は、450℃〜600℃である。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の不純物分布のバラツキを抑え、STIエッジ部分への電界集中をより効果的に制御でき、実効チャネル幅が狭くなることを抑制できる半導体装置およびその製造方法を提供する。

【解決手段】P型のシリコン基板10の一主面11に、トレンチ22と絶縁物24とを有する素子分離領域25と、素子分離領域25に囲まれた素子領域12であって、シリコン基板10の側面上部17が、トレンチ25に露出した素子領域12を形成し、ゲート絶縁膜40をシリコン基板10の上面14から側面上部17に延在して形成し、N+型ポリシリコン32とN+型ポリシリコン32の両側のP+型ポリシリコン34と、P+型ポリシリコン34の下側の側面上部17に沿って設けられたN+型ポリシリコン36とを有するゲート電極30を形成する。

(もっと読む)

保護トランジスタおよび半導体集積回路

【課題】占有面積が小さく、所望の耐圧と熱破壊の防止を両立した保護トランジスタを提供する。

【解決手段】ゲート長方向の一方の側でゲート直下の領域に隣接しているゲート・ドレイン間領域REgdが、ゲート幅方向に互いに隣接する領域として、第1領域REgd1と第2領域REgd2とを有する。第1領域は、ドレイン耐圧が相対的に大きく、第2領域は、ドレイン電極(ドレインコンタクト部に設けられているシリサイド層10D)からの距離が平面視で第1領域より遠く、ドレイン耐圧が相対的に小さい。このため、耐圧が低いゲート・ドレイン間領域REgd2の加熱部分Aからドレインコンタクト部が遠いが、面積は小さく(または拡大しない)構造となっている。

(もっと読む)

絶縁膜下の埋め込みバック・コントロール・ゲートを有するSeOI上の同型のトランジスタからなる回路

【課題】リソグラフィーパターン転写に存在する変動性によって発生する問題の解決、STIを使用せず、構造を厳密化して空間を節約すること、転写されるべきより規則的かつ緻密な構造の提供。

【解決手段】SeOI基板上に形成された半導体デバイスであり、電界効果トランジスタから形成された行の形で配置されパターンのアレイを備え、電界効果トランジスタのチャンネル領域の上方に形成されたフロント・コントロール・ゲート領域を備え、各行に含まれるソース領域およびドレイン領域も同じ寸法を有し、かつ所定の寸法を有するフロント・コントロール・ゲート領域だけ隔てられ、パターンに含まれる少なくとも1つのトランジスタT1〜T4がチャンネル領域の下方に存在するベース基板内に形成されたバック・コントロール・ゲート領域を有し、トランジスタのしきい電圧をシフトさせて、バック・コントロール・ゲート領域がバイアスされることを可能とする。

(もっと読む)

半導体装置と論理回路およびその製造方法

【課題】インパクトイオン化MISFETに関して、微細素子において二つの入力によりAND型論理素子動作することを可能とし、素子バラツキを低減することを可能とし、消費電力を低減することを可能とする半導体装置を提供する。

【解決手段】第1導電型または真性である半導体領域の表面上に形成された二つの独立した第一および第二のゲート電極への両者への入力により反転層が形成された場合に、インパクトイオン化によるスイッチング動作が可能となることを特徴とする、半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜、及び、ゲート電極としてメタル膜を含む半導体装置において、逆短チャネル効果の発生を防止して高性能化を実現する。

【課題手段】半導体装置は、半導体基板101の上に形成されたランタンを含有する高誘電率ゲート絶縁膜102と、高誘電率ゲート絶縁膜102の上に形成されたキャップ膜103と、キャップ膜103の上に形成されたメタル膜104と、メタル膜104の上に形成されたポリシリコン膜105と、高誘電率ゲート絶縁膜102、キャップ膜103、メタル膜104、及びポリシリコン膜105それぞれの両側面に形成されたランタンを含有するゲート側壁絶縁膜106とを備えている。

(もっと読む)

半導体素子及びその製造方法

【課題】 チャネルカット領域を形成するために、バーズビークの下方または近傍に選択的にイオン注入を行う工程が必要である。製造コスト低減のために、工程数の削減が求められている。

【解決手段】 半導体基板の表面に、活性領域を画定する素子分離絶縁膜が形成されている。活性領域の外周線から、素子分離絶縁膜と半導体基板との界面に沿って隙間が形成されている。半導体基板の上に、活性領域と交差し、両端が素子分離絶縁膜の上まで延在するゲートパターンが形成されている。ゲートパターンは、活性領域上においては、第1の酸化膜と電極とを含み、ゲート電極が素子分離絶縁膜の上まで延在する。隙間内の半導体基板の表面に、第1の酸化膜に連続する第2の酸化膜が形成されている。隙間が、ゲート電極に連続する半導体部材で埋め込まれている。

(もっと読む)

半導体装置の製造方法

【課題】NMOSトランジスタおよびPMOSトランジスタを有する半導体装置において、ショートチャネル効果を抑制するとともに、ゲート−ドレイン間での電流リークを低減し、また、ゲートオーバーラップに起因する寄生容量を低減して、回路動作速度の低下を低減した半導体装置を提供する。

【解決手段】低電圧NMOS領域LNRにおけるシリコン基板1の表面内に、N型不純物、例えばヒ素をイオン注入により比較的低濃度に導入して、エクステンション層61を形成する。そして、シリコン基板1の全面を覆うように、シリコン酸化膜OX2を形成し、ゲート電極51〜54の側面においてはシリコン酸化膜OX2をオフセットサイドウォールとして使用し、低電圧PMOS領域LPRにおけるシリコン基板1の表面内に、ボロンをイオン注入により比較的低濃度に導入して、エクステンション層62となるP型不純物層621を形成する。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造コストが低減し、電界効果トランジスタの短チャネル効果が抑制された半導体装置を提供する。

【解決手段】第1導電型のソース領域と、第1導電型のドレイン領域と、が表面に選択的に形成された第2導電型のウェル領域と、前記ソース領域と前記ドレイン領域との間の電流経路を制御する制御電極と、前記ソース領域に接続された第1の主電極と、前記ドレイン領域に接続された第2の主電極と、を備え、前記ソース領域の最も曲率が高い部分または前記ドレイン領域の最も曲率が高い部分と同じ深さの前記ウェル領域の位置を基準した場合、前記ウェル領域の深さ方向の前記第2導電型の不純物濃度分布のプロファイルは、前記基準からプラスマイナス0.15ミクロンの範囲に不純物濃度分布のピークを有することを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置およびその製造方法、pチャネルMOSトランジスタ

【課題】nチャネルMOSトランジスタにおいてhigh−Kゲート絶縁膜をhigh−K誘電体膜と酸化ランタン膜の積層により構成した半導体装置において、酸化ランタン膜のパターニングプロセスを不要とする半導体装置の製造方法を提供する。

【解決手段】界面酸化膜22上に形成されたhigh−K誘電体膜23上に酸化膜24を形成する工程と、前記high−K誘電体膜に窒化物層25を形成する工程と、前記窒化物層および前記酸化膜を第1の素子領域21Aから選択的に除去し、第1および第2の素子領域21Bにわたり酸化ランタン膜26を形成し、前記第1の素子領域においては前記界面酸化膜と前記high−K誘電体膜と前記酸化ランタン膜を積層した第1の積層構造を、また前記第2の素子領域においては前記界面酸化膜と前記high−K誘電体膜と前記酸化膜と前記窒化物層と前記酸化ランタン膜を積層した第2の積層構造を形成する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】発熱に対して効率的に冷却を行うことができる、半導体装置を提供する。

【解決手段】半導体層の表面に形成された活性領域5,6と、N型の不純物を有する半導体から成るN型ゲート7Nと、P型の不純物を有する半導体から成るP型ゲート7Pと、N型ゲート7N及びP型ゲート7P及び活性領域5,6に接続された第1の金属配線13と、P型ゲート7P及びN型ゲート7Nに接続された第2の金属配線と15、第2の金属配線15に接続され、熱を外部に放出するための放熱部19とを含む冷却機構素子を備えた半導体装置を構成する。

(もっと読む)

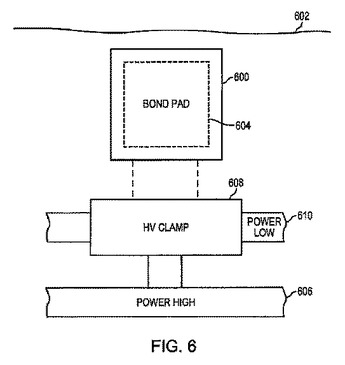

一体化された過渡過電圧保護を有するボンドパッド

過電圧クランプ構造および過電圧クランプ構造を形成する方法が提供される。いくつかの実施形態において、過電圧クランプ構造は、基板(708)と、基板の上に配置されるボンドパッド(700)と、ボンドパッドの下の基板に形成されるプレーナー高電圧MOSデバイス(100c)とを含む。高電圧MOSデバイス(100c)は、基板に形成される井戸(100、115)と、井戸に形成されるドープされた浅い領域(130、135、140、145)と、井戸の上に配置されるゲート(160)とを含み得る。いくつかの実施形態において、クランプ構造は、第1のスナップバック後にソフトな故障の漏れを示さず、デバイスエリアを有意に減少させながら、ESDロバストネスを大幅に延ばす。  (もっと読む)

(もっと読む)

CMOS用歪トランジスタの集積化

【課題】n型MOSデバイス(NMOS)の電子の移動度の向上、およびp型MOSデバイス(PMOS)のホールの移動度の向上した半導体装置および製造方法の提供。

【解決手段】(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

半導体装置

【課題】MIM構造の容量素子を有する半導体装置において、容量素子の信頼性を向上させることのできる技術を提供する。

【解決手段】下部電極DEと、容量絶縁膜CELと、上部電極UEとからなる容量素子において、下部電極DEを、半導体基板1の主面上の絶縁膜に形成された電極溝17aの内部に埋め込まれた金属膜によって構成し、上部電極UEを、TiN膜(下層金属膜)22と、TiN膜(下層金属膜)22上に形成されたTi膜(キャップ金属膜)23との積層膜によって構成する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供し得る半導体装置の製造方法を提供することにある。

【解決手段】第2の応力膜44に対する第2の絶縁膜48の選択比が第1の値である第1の条件でエッチングを行うことにより、第1のコンタクトホール60eを少なくとも第2の応力膜の途中まで開口し、第2のコンタクトホールを少なくとも第2の絶縁膜の途中まで開口するエッチング工程と、第2の応力膜に対する第2の絶縁膜の選択比が第1の値より大きい第2の値である第2の条件でエッチングを行うことにより、第1のコンタクトホールにより第2の応力膜44を貫き、第2のコンタクトホールにより第2の絶縁膜及び第1の絶縁膜40を貫くエッチング工程と、更なるエッチングを行い、第1のコンタクトホールをゲート配線20まで到達させ、第2のコンタクトホールをトランジスタのソース/ドレインまで到達させる第3のエッチング工程とを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】短チャネル効果の発生を抑制できる半導体装置及びその製造方法の提供。

【解決手段】本発明の半導体装置は、半導体基板1の活性領域上にゲート絶縁膜5aを介して形成されたゲート電極105と、ゲート電極105側面を覆う第1絶縁膜サイドウォール5bと、ゲート電極105を挟んで形成されたソース領域108S及びドレイン領域108Dにおいて、側面が第1絶縁膜サイドウォール5bに接して半導体基板1上面に形成されたシリコン層109と、第1絶縁膜サイドウォール5bを介してゲート電極105側面と対向し、底面がシリコン層109上面に接して形成された第2絶縁膜サイドウォール5dと、シリコン層109内下層部に設けられたLDD不純物層109aと、シリコン層109内上層部に設けられた高濃度不純物層109bと、LDD不純物層109aの下方、半導体基板1の表面側に形成されたポケット不純物層108aとを具備する。

(もっと読む)

半導体製造装置

【課題】内部応力を有する膜を基板の裏面にのみ形成することにより、基板の反り量を抑制し、その際に基板の表面にダメージを与えず、裏面に対する成膜と表面に対するパターン形成とを一貫して行う半導体製造装置を得られるようにする。

【解決手段】基板に薬液を塗布する薬液塗布部102と、基板を加熱する加熱処理部104と、基板の表面にレジストを塗布するレジスト塗布部107と、そのレジストに所定のパターンを露光する露光部105と、そのレジストを現像することにより所定のパターンを得る現像部108とを備えている。薬液塗布部102は、基板を浮遊した状態で、基板を回転させながら基板の裏面にのみ薬液を塗布する薬液塗布手段を有し、加熱処理部104は、基板に熱処理を行うことにより、内部応力を有する応力印加膜を成膜する熱処理手段を有し、裏面に応力印加膜の成膜を行うことと、表面に所定のパターンを形成する処理とを一貫して行う。

(もっと読む)

81 - 100 / 956

[ Back to top ]