Fターム[5F048BB07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | 多結晶Si (4,558) | P型ドープ多結晶Si (956)

Fターム[5F048BB07]に分類される特許

141 - 160 / 956

半導体装置

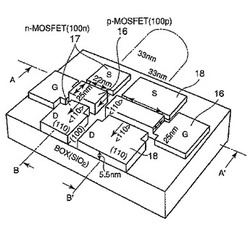

【課題】10GHz程度以上のクロック周波数での動作が可能な高速半導体装置の提供。

【解決手段】n−MOSFET100n、p−MOSFET100pを有し、n−MOSFETのチャンネルを形成する第1の領域の表面が(100)面から±10°以内の面または(110)面から±10°以内の面のを有し、p−MOSFETのチャンネルを形成する第2の領域の表面が((110)面から±10°以内の面または(100)面から±10°以内の面のを有し、第1及び第2の領域の各々から各々の両端の前記ソース電極、ドレイン電極の各々までの抵抗を4Ω・μm以下とし、かつ第1の領域と第1のゲート絶縁層との界面及び第2の領域と第2のゲート絶縁層との界面を、各領域のソースからドレインに向かう方向での長さ2nmにおけるピーク・トゥ・バレイが0.3nm以下であるような平坦度とした半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】 抵抗素子の抵抗値の選択範囲を拡大し、且つ抵抗層形成後にシリサイドブロックを形成せずに該抵抗層のシリサイド化を防止することを可能にする。

【解決手段】 半導体領域11上に絶縁膜15を形成し、絶縁膜15を介して半導体領域11に不純物のイオン注入12を行う。これにより、絶縁膜15の下に抵抗層13が形成されるとともに、抵抗層13に隣接して電極領域14が形成される。その後、電極領域14の表面にシリサイド膜17を形成する。このとき、絶縁膜15は、抵抗層13がシリサイド化されることを防止するシリサイドブロックとして機能する。イオン注入12として、同一半導体基板上に形成されるMOSトランジスタのソース/ドレイン領域への不純物注入工程を利用し得る。

(もっと読む)

半導体装置及びその製造方法、固体撮像素子

【課題】生産性良く、歩留まり良く製造することを可能にする構造の半導体装置を提供する。

【解決手段】n型の不純物が導入された電極層15と、その上の不純物が導入されていない電極層17との積層構造であるゲート電極21を含む、縦型のNMOSトランジスタと、電極層15とその上の電極層16との積層構造であるゲート電極22,23を含む、平面型のNMOSトランジスタと、電極層15とその上のp型の不純物が導入された電極層17との積層構造であり、p型の電極であるゲート電極24を含む、平面型のPMOSトランジスタと、縦型のNMOSトランジスタの下に形成された、フォトダイオード等の他の回路素子とを含む半導体装置を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極を有するpチャネル型電界効果トランジスタにおいて、所望するしきい値電圧を安定して得ることのできる技術を提供する。

【解決手段】半導体基板1上に形成されたHfSiON膜からなるゲート絶縁膜5h上に、Me−O−Al−O−Me結合を含むMe1−xAlxOy(0.2≦x≦0.75、0.2≦y≦1.5)組成の導電性膜を一部に有するメタルゲート電極6、またはMe−O−Al−N−Me結合を含むMe1−xAlxN1−zOz(0.2≦x≦0.75、0.1≦z≦0.9)組成の導電性膜を一部に有するメタルゲート電極6を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】p型ソースドレイン領域内にシリコン混晶層が形成されていると、N型MISトランジスタのキャリア移動度が低下する虞があった。

【解決手段】活性領域10aと活性領域10bとが素子分離領域11により分離されており、活性領域10a上には第1導電型の第1のトランジスタが設けられており、活性領域10b上には第2導電型の第2のトランジスタが設けられている。活性領域10b内には、第1の応力を有するシリコン混晶層21が設けられている。素子分離領域11のうち活性領域10aと活性領域10bとで挟まれた部分の上面には凹部22が設けられている。凹部23内には応力絶縁膜24が設けられており、応力絶縁膜24は第1の応力とは反対方向の第2の応力を有する。

(もっと読む)

半導体装置とその製造方法

【課題】MOSトランジスタとバイポーラトランジスタとが混載された半導体装置とその製造方法において、半導体装置の信頼性を高めること。

【解決手段】シリコン基板20素子分離絶縁膜24を形成する工程と、シリコン基板20に低電圧p型MOSトランジスタTRLVP用のLDD領域45を形成する工程と、シリコン基板20に高電圧p型MOSトランジスタTRHVP用のLDD領域55をLDD領域45よりも深く形成するのと同時に、シリコン基板20にバイポーラトランジスタTRBIP用の第1のエミッタ領域46を形成する工程と、各領域45、46、55におけるシリコン基板20の表層に高融点金属シリサイド層70を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗素子の小型化と電界効果トランジスタのラッチアップ耐性の向上とを両立させた半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板11のNウェル抵抗素子形成領域にSTI12を形成する。次に、P型MOSトランジスタ形成領域に対してドナーを注入して、ドナー拡散領域21を形成する。次に、Nウェル抵抗素子形成領域及びP型MOSトランジスタ形成領域に対してドナーを注入して、Nウェル抵抗素子形成領域におけるSTI12の直下域にN型ウェル14を形成すると共に、P型MOSトランジスタ形成領域にドナー拡散領域20を形成する。ドナー拡散領域21及び20は重ね合わせられて、P型MOSトランジスタ7のチャネル領域を構成するN型ウェル19が形成される。このとき、N型ウェル14及びドナー拡散領域20を形成するための不純物注入量を、ドナー拡散領域21を形成するための不純物注入量よりも少なくする。

(もっと読む)

半導体装置の製造方法

【課題】ハーフピッチサイズが32nm以下のCMISデバイスを有する半導体装置において、nチャネル型電界効果トランジスタおよびpチャネル型電界効果トランジスタのそれぞれの閾値電圧を適切に設定することのできる技術を提供する。

【解決手段】pMIS形成領域に、主としてAlが拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜5ならびに下層メタルゲート電極6Dと上層メタルゲート電極6Uとの積層膜からなるメタルゲート電極6を有するpMIS100pを形成し、nMIS形成領域に、主としてLa(ランタン)が拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜11ならびに上層メタルゲート電極6Uからなるメタルゲート電極12を有するnMIS100nを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】基板上に抵抗素子を備える半導体装置において、シリコン抵抗素子の抵抗値の低下を防ぐ。

【解決手段】半導体装置1は、基板10上に、MIPS構造を有するMOSトランジスタとシリコン抵抗素子を備える。抵抗素子は、基板10の上に設けられた金属膜28と、金属膜28の上に設けられた絶縁膜30と、絶縁膜30の上に設けられたシリコン層37と、からなる。絶縁膜30は、シリコン酸化膜、シリコン窒化膜、HfSiON、HfO2、ZrO2、HfAlO、Al2O3から選ばれる少なくとも一つを有する。

(もっと読む)

半導体装置の製造方法

【課題】所望のMOSトランジスタのみにチャネル領域に引っ張り応力を印加してキャリア移動度を向上させ、且つ、製造工程の複雑化を抑える。

【解決手段】シリコン基板10上にnMOSトランジスタのゲート絶縁膜13およびゲート電極14を非単結晶シリコンで形成し、ゲート電極14をマスクとして例えばAsやSb等の比較的質量数が大きい(質量数70以上)n型ドーパントを注入することで、nMOSトランジスタのソースドレイン領域を形成する。それにより、ゲート電極14は非晶質化する。そして、ゲート電極14が再結晶化する温度(約550℃)以下の温度条件でゲート電極14を覆うようにシリコン酸化膜40を形成し、その後1000℃程度の加熱処理を行う。それにより、ゲート電極14内に強い圧縮応力が残留すると共に、その下のチャネル領域には強い引っ張り応力が印加され、当該nMOSトランジスタのキャリア移動度は向上する。

(もっと読む)

半導体装置及びその製造方法

【課題】複数のゲート長を有するトランジスタを形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に、第1の柱状体と第2の柱状体とを形成する工程と、前記第1及び第2の柱状体と前記半導体基板とを覆う半導体膜であって、前記第1の柱状体を覆う第1の部分と前記第2の柱状体を覆う第2の部分との導電型及び不純物の濃度の少なくとも一方が互いに異なるように半導体膜を形成する工程と、前記半導体膜をエッチバックして、前記第1及び第2の柱状体のそれぞれの側壁に、互いに異なる高さを有する第1の半導体膜柱状部と第2の半導体膜柱状部とを形成する工程と、を備えることを特徴とする半導体装置の製造方法を採用する。

(もっと読む)

半導体装置及び配線

【課題】低抵抗の電極や配線を有する半導体装置を実現する。

【解決手段】本実施形態による配線は、p型不純物が導入されたp型不純物層部分と、n型不純物が導入されたn型不純物層部分と、p型及びn型不純物が導入された(p+n)型不純物層部分と、を含む半導体層と、少なくとも(p+n)型不純物層部分上に形成されたシリサイド層と、を備え、(p+n)型不純物層部分に含まれるp型不純物とn型不純物の総濃度は、5E20cm−3未満である。

(もっと読む)

半導体装置

【課題】ESD耐性に優れ、保護素子の新たな作製を要さない半導体装置を提供する。

【解決手段】この発明にかかる半導体装置は、主電流を制御するゲート端子22に接続されたゲート電極と、主電流を流すドレイン端子21に接続されたドレイン電極と、主電流を流すソース端子23に接続されたソース電極とを有する主MOSFET素子31と、ゲート端子22に接続されたゲート電極と、ドレイン端子21に接続されたドレイン電極と、電流検出用のセンスソース端子24に接続されたソース電極とを有するセンスMOSFET素子32と、ソース端子23に接続されたゲート電極と、ドレイン端子21に接続されたドレイン電極と、センスソース端子24に接続されたソース電極およびボディ電極とを有するESD保護素子A33と、ゲート端子22に接続されたカソード電極と、センスソース端子24に接続されたアノード電極とを有するESD保護素子D41とを備える。

(もっと読む)

水素化ホウ素クラスターイオンの注入によるイオン注入装置及び半導体製造方法

【課題】イオン化チャンバ内の電子ビーム通路に均一な磁場を生成する磁場装置を提供する。

【解決手段】電子衝撃イオン源用の磁場装置において、イオン化チャンバ内の電子ビーム通路に均一な磁束線119を生成させるために、一対の永久磁石510A、510Bにより生成された磁束が、磁気ヨークアセンブリ500を経て、電子ビーム通過用の一対の整列した開口530A、530Bを有する磁極片520A、520Bの間の間隙を通って戻るようにする。

(もっと読む)

デュアルゲート不純物ドーピング方法及びこれを用いたデュアルゲート形成方法

【課題】デュアルゲート不純物ドーピング方法及びこれを用いたデュアルゲート形成方法を提供する。

【解決手段】デュアルゲート不純物ドーピング方法は、第1領域及び第2領域を有する半導体基板上のゲート導電膜に第1導電型の不純物イオンをドープする段階であって、ゲート導電膜の下部よりも上部における不純物ドーピング濃度がより高い濃度勾配でドープする段階と、第2領域のゲート導電膜をオープンさせるマスクを用いて第2領域のゲート導電膜に第2導電型の不純物イオンをドープする段階と、熱処理を行い、第1導電型及び第2導電型の不純物イオンを拡散させる段階と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜及びメタルゲート電極を備えたCMISFETの生産性や性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有絶縁膜5を形成し、その上に窒化金属膜7を形成し、窒化金属膜7上のフォトレジストパターンをマスクにしたウェットエッチングによって、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aの窒化金属膜7を選択的に除去する。それから、希土類元素を含有するしきい値調整層8を形成し、熱処理を行って、nMIS形成領域1AのHf含有絶縁膜5をしきい値調整層8と反応させるが、pチャネル型MISFET形成予定領域であるpMIS形成領域1BのHf含有絶縁膜5は、窒化金属膜7があるためしきい値調整層8とは反応しない。その後、未反応のしきい値調整層8と窒化金属膜7を除去してから、nMIS形成領域1AとpMIS形成領域1Bにメタルゲート電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート配線に達するコンタクトホールを確実に形成し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38を形成する工程と、第1応力膜とエッチング特性が異なる絶縁膜40を形成する工程と、第1領域2を覆う第1マスク60を用いて、第2領域内の絶縁膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の絶縁膜をサイドエッチングする工程と、第1マスクを用いて第2領域内の第1応力膜をエッチングする工程と、絶縁膜とエッチング特性が異なる第2応力膜を形成する工程と、第2領域を覆い、第1領域側の端面が絶縁膜上に位置する第2マスクを用いて、第2応力膜の一部が第1応力膜の一部及び絶縁膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】薄膜BOX−SOI基板に形成される電界効果型トランジスタの信頼性および動作特性の劣化を防ぐことのできる技術を提供する。

【解決手段】薄膜BOX−SOI基板の主面上に所定の間隔で配置されたnウェルnwおよびpウェルpwが形成されており、pウェルpwに形成されたnMIS1nは、SOI層1iの主面上に所定の距離を隔てて積み上げられた半導体層に形成された一対のn型ソース・ドレイン領域2nと、一対のn型ソース・ドレイン領域2nに挟まれたゲート絶縁膜3、ゲート電極4、およびサイドウォール5とを有しており、nウェルnwとpウェルpwとの間に素子分離10を形成し、素子分離10の側端部が、n型ソース・ドレイン領域2nの側端部(BOX層1bの側壁部)よりもゲート電極4側に広がっている。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

半導体構造体およびその形成方法(内部応力を有する半導体ナノワイヤ)

【課題】高性能の相補型金属半導体(CMOS)回路の為の高いオン電流をもたらす半導体ナノワイヤ・デバイスを提供する。

【解決手段】両方の端部に半導体パッド33A、37Aを有する半導体ナノワイヤ32が、基板上にサスペンドされる。半導体ナノワイヤが応力発生ライナ部によって長手方向の応力を受けている間、半導体ナノワイヤの中間部の上にゲート誘電体36及びゲート電極38が形成される。ゲート誘電体及びゲート電極の形成によって半導体ナノワイヤの歪み状態が固定されるため、半導体ナノワイヤの中間部は、応力発生ライナの除去後に長手方向の固有の内部応力を受ける。半導体パッド内にソース及びドレイン領域33B,37Bが形成され、半導体ナノワイヤ・トランジスタが得られる。ソース及びドレイン・パッドの上に、中間工程(MOL)誘電体層を直接形成することができる。

(もっと読む)

141 - 160 / 956

[ Back to top ]