Fターム[5F048BB07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | 多結晶Si (4,558) | P型ドープ多結晶Si (956)

Fターム[5F048BB07]に分類される特許

101 - 120 / 956

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

半導体装置

【課題】絶縁層上の半導体層に形成された部分空乏型のトランジスターにおいて、高いON/OFF比と、安定動作を同時に実現できるようにした半導体装置を提供する。

【解決手段】絶縁層上の半導体層に形成された部分空乏型の第1トランジスターと、前記半導体層に形成された第2トランジスターと、前記半導体層に形成された第3トランジスターと、を備え、前記第1トランジスターは、第1導電型の第1ソース又は第1ドレインを有し、前記第2トランジスターは、第1導電型の第2ソース又は第2ドレインを有し、前記第3トランジスターは、第2導電型の第3ソース又は第3ドレインを有し、前記第1ソース又は第1ドレインの一方と、前記第2ソース又は第2ドレインの一方とが電気的に接続され、前記第2ソース又は第2ドレインの他方と、前記第1トランジスターのボディ領域と、前記第3ソース又は第3ドレインの一方とが互いに電気的に接続されている。

(もっと読む)

半導体装置、その製造方法及び表示装置

【課題】他の基板に接合され、かつ薄膜化された基体層に形成されたPMOSトランジスタのサブスレッシュホールド特性を向上することができる半導体装置、その製造方法及び表示装置を提供する。

【解決手段】基板と、基体層に形成され、かつ素子を含むとともに、基板に接合されたデバイス部とを備える半導体装置であって、上記デバイス部は、素子として、少なくともPMOSトランジスタを含み、上記PMOSトランジスタは、基体層のゲート電極側に電気伝導経路を有する半導体装置である。

(もっと読む)

半導体装置及びその設計方法並びに半導体装置の製造方法

【課題】良好な電気的特性を有する半導体装置及びその設計方法並びに半導体装置の製造方法を提供する。

【解決手段】第1のトランジスタが形成される第1の活性領域のパターンと、第2のトランジスタが形成される第2の活性領域のパターンとを配置するステップS2と、第1の活性領域及び第2の活性領域と交差するゲート配線のパターンを配置するステップS3と、第1の活性領域とゲート配線とが重なり合う領域である第1の領域を抽出するステップS4と、第1の活性領域を含む領域上に、圧縮応力膜のパターンを配置するステップS5とを有し、第2の活性領域を含む領域上に、圧縮応力膜に隣接する引っ張り応力膜のパターンを配置するステップS6とをコンピュータに実行させることにより、半導体装置のレイアウトパターンを取得する工程を有し、圧縮応力膜のパターンを配置するステップでは、第1の領域の縁部の位置に基づいて、圧縮応力膜のパターンの縁部の位置が設定される。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの面積を小さくしてもフリッカノイズを低減できる半導体装置を提供する。

【解決手段】本発明の一態様の半導体装置は、シリコン基板1に形成された第1及び第2のP型低濃度不純物層3a,3bと、シリコン基板1に埋め込まれて形成され、第1及び第2のP型低濃度不純物層の相互間に位置する埋め込みチャネル層5と、埋め込みチャネル層の上方に位置するシリコン基板の表面上にゲート絶縁膜6を介して形成され、N型不純物が導入されたポリシリコン膜からなるゲート電極と、第1のP型低濃度不純物層3a内における深さが浅い領域に形成されたソース領域及びドレイン領域の一方のP型層13aと、第2のP型低濃度不純物層3b内における深さが浅い領域に形成されたソース領域及びドレイン領域の他方のP型層13bと、を具備することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】n型MISトランジスタを有する半導体装置の特性ばらつきを低減させる。

【解決手段】シリコン基板1上のメモリ領域RMに形成された、n型導電型である第1トランジスタQ1は、ホウ素を含むメモリ用チャネル領域CH1と、メモリ用ゲート電極GE1の両側壁側下に形成された、n型のメモリ用エクステンション領域ET1および酸素を含む拡散防止領域PA1とを有している。ここで、拡散防止領域PA1はメモリ用エクステンション領域ET1を内包するようにして形成されている。また、拡散防止領域PA1は、少なくともその一部が、メモリ用エクステンション領域ET1とメモリ用チャネル領域CH1との間に配置されている。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置の製造方法を提供することにある。

【解決手段】側壁にサイドウォール絶縁膜が形成されたゲート配線20を形成する工程と、第1の応力膜38を形成する工程と、第1の応力膜上にエッチングストッパ膜40を形成する工程と、エッチングストッパ膜をエッチングし、第1の応力膜のうちのサイドウォール絶縁膜を覆う部分上にエッチングストッパ膜を選択的に残存させる工程と、第2の領域4を露出する第1のマスクを用いて第2の領域内の第1の応力膜をエッチングする工程と、第2の応力膜42を形成する工程と、第1の領域2を露出する第2のマスクを用いて第1の領域内の第2の応力膜をエッチングする工程と、第1の領域と第2の領域との境界部におけるゲート配線に達するコンタクトホール46aを形成する工程とを有している。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

半導体装置およびその製造方法

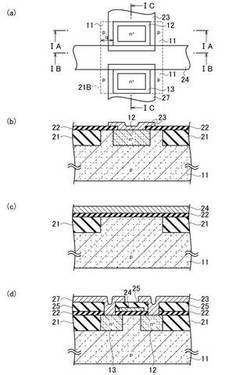

【課題】相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置およびその製造方法の提供。

【解決手段】相対的に薄いゲート絶縁膜25を有するMOSトランジスタが形成される領域のフィールド絶縁膜端23を相対的に厚いゲート絶縁膜24で覆うことにより、フィールド絶縁膜下部に形成された反転防止拡散層31から相対的に薄いゲート絶縁膜25を有するMOSトランジスタのチャネル領域33をオフセットさせることによって、フィールド絶縁膜の膜厚ばらつきや相対的に厚い第一のゲート絶縁膜24のエッチングばらつき、および反転防止拡散層によるチャネル端の濃度変動の影響を受けず、MOSトランジスタのチャネル幅を短く設計した際に生じる狭チャネル効果の影響を抑制することが可能となり、素子特性が安定した半導体装置。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。一部の構造及び方法は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。一部の構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得る。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】低電圧動作CMOS半導体装置の製造におけるイオン注入およびそれに伴うレジストのパターニング工程数を削減する。

【解決手段】第1導電型半導体基板上に第1導電型MOSトランジスタと第2導電型MOSトランジスタを有する半導体装置の製造方法において、第1導電型MOSトランジスタのチャネルが形成される領域の表面に、前記第2導電型ウェル拡散層よりも低濃度の第2導電型低濃度拡散層を備えることで、第1導電型MOSトランジスタと第2導電型MOSトランジスタは共通の第2導電型ゲート電極であっても、第1導電型半導体装置は表面チャネル形での動作を実現する。これにより、製造工程数が削減可能となる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に対する不純物の突き抜けを抑止する。

【課題を解決するための手段】半導体装置の製造方法は、基板上方に成膜した多結晶シリコンをエッチングして基板の第1領域上方に第1ゲート電極を形成し、基板の第2領域上方に第2ゲート電極を形成し、第1領域及び第1ゲート電極を覆う第1パターンを形成し、第2ゲート電極及び第1パターンをマスクにして第2領域に第1不純物を第1ドーズ量で注入して第2領域に第1エクステンション領域を形成し、第1ゲート電極、第1領域及び第2ゲート電極の上面を露出させた第2パターンを形成し、第1エクステンション領域を覆い、第1ゲート電極、第2ゲート電極及び第2パターンをマスクにして第1領域に第2不純物を第1ドーズ量よりも多いドーズ量で注入して第1領域に第2エクステンション領域を形成するとともに、第1ゲート電極及び第2ゲート電極の少なくとも上部をアモルファス化する。

(もっと読む)

半導体装置の製造方法

【課題】外部から印加される電源電圧の仕様に対応した、半導体装置の製造方法を提供する。

【解決手段】チャネルイオン注入工程、ゲート酸化膜形成工程、および、ゲート電極パターニング工程の少なくとも1つの工程を、外部から第1の電源電圧が供給されて動作する第1の半導体装置を製造する場合には第1の電源電圧で動作する素子を形成する工程で行い、外部から第2の電源電圧が供給されて動作する第2の半導体装置を製造する場合には第2の電源電圧で動作する素子を形成する工程で行い、また、第1の半導体装置の製造の場合と第2の半導体装置の製造の場合とで少なくとも拡散領域形成工程を共通に行うものである。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート構造としてメタル電極/High−k膜構造を用いた半導体装置において、仕事関数の制御とEOTの薄膜化とを両立させる。

【解決手段】半導体基板101におけるnチャネルMISトランジスタ形成領域の上に、ゲート絶縁膜として、第1の高誘電率絶縁層202、アルミニウム含有層203、ランタン含有層204及び第2の高誘電率絶縁層205を順次形成する。その後、ゲート電極形成を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体ゲート絶縁膜/メタルゲート電極のMOSトランジスタ構造において、メタルゲート電極側壁の酸化層を抑制し、トランジスタ駆動能力を改善する。

【解決手段】基板101上に、金属含有膜110を形成する工程(a)と、反応室内において金属含有膜にアンモニアラジカルを曝露する工程(b)と、反応室内に不活性ガスを供給し、工程(b)において生じたガスを排気する工程(c)と、工程(b)及び工程(c)を所定の回数繰り返した後に、大気曝露することなく、反応室内において金属含有膜110を覆うシリコン窒化膜100aを形成する工程(d)とを備える。

(もっと読む)

半導体装置の製造方法

【課題】第1導電型の第1の多結晶シリコン膜と第2導電型の第2の多結晶シリコン膜とを同時にエッチング加工する際の加工精度を向上するための製造方法の提供。

【解決手段】第1導電型の不純物を含む第1の多結晶シリコン膜103−1と、第2導電型の不純物を含む第2の多結晶シリコン膜103−2とを形成し、前記第1の多結晶シリコン膜をエッチングし、第1のパターンを形成するとともに、前記第2の多結晶シリコン膜をエッチングし、第2のパターンを形成するパターニング工程とを備える。パターニング工程は、第1のパターン及び第2のパターンのそれぞれの側面を露出させるようにエッチングを行う第1のエッチング工程と、露出した側面を酸化して側面に酸化膜を形成する酸化工程と、側面が酸化膜で保護された状態でエッチングを行い、第1の多結晶シリコン膜及び第2の多結晶シリコン膜のパターニングを完了させる第2のエッチング工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】接合リークを抑制しながら、キャリアの移動度向上とチャネル中でのキャリア速度の増加を実現することができるトランジスタを提供する。

【解決手段】半導体基板10のチャネル形成領域にチャネル方向に第1の幅を有するSiGe層15が埋め込まれ、チャネル形成領域上にゲート絶縁膜28が形成され、ゲート絶縁膜上に、第1の幅より大きい第2の幅を有してSiGe層の形成領域からはみ出す領域を有するゲート電極29が形成され、チャネル形成領域を挟む半導体基板においてエクステンション領域12を有するソースドレイン領域13が形成されて、電界効果トランジスタが構成されており、エクステンション領域と半導体基板の接合面から伸びる空乏層がSiGe層に達しないようにエクステンション領域とSiGe層が離間されている。

(もっと読む)

バンド設計超格子を有する半導体装置

【課題】例えば大きな電荷キャリア移動度を有する半導体装置を提供する。

【解決手段】半導体装置は、複数の積層された層群を有する超格子を有する。また装置は、電荷キャリアが積層された層群と平行な方向に超格子を通って輸送される領域を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】消費電力が低減された、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】第1電圧が印加される第1導電型領域12と、前記第1導電型領域から離れた位置に設けられ、前記第1導電型とは逆の導電型の第2電圧が印加される第2導電型領域13と、前記第1導電型領域と前記第2導電型領域との間を占めるように配置された、ウェル層11と、オン状態であるときに、前記ウェル層に含まれる第1領域に反転層を形成させる、第1ゲート電極15及び第2領域に反転層を形成させる、第2ゲート電極16とを具備する。前記第1領域と前記第2領域との間の間隔は、前記第1ゲート電極及び前記第2ゲート電極がオン状態である場合に、前記第1電圧と前記第2電圧との差によってインパクトイオン化現象が発生し、前記第1ゲート電極及び前記第2ゲート電極の少なくとも一方がオフ状態である場合に、インパクトイオン化現象が発生しないように設定される。

(もっと読む)

101 - 120 / 956

[ Back to top ]