Fターム[5F048BB07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | 多結晶Si (4,558) | P型ドープ多結晶Si (956)

Fターム[5F048BB07]に分類される特許

21 - 40 / 956

半導体集積回路装置の製造方法

【課題】MISFETが微細化されてくると、単チャネル効果が更に顕著となり、トランジスタの特性ばらつきが増大しやすくなる。ここで、トランジスタの特性ばらつきは、従来のゲート長に依存するものに加えて、オフセットスペーサ長やサイドウォールスペーサ長に依存するものの影響が強くなることが本願発明者らによって明らかにされた。

【解決手段】本願の発明は、CMIS型半導体集積回路装置の製造方法において、オフセットスペーサ長とサイドウォールスペーサ長の和をNチャネルMISFETとPチャネルMISFETに於いて、調整するものである。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体集積回路およびその製造方法

【課題】半導体集積回路に電源を投入後の通常の動作時にリーク電流の抑制と同時にクランプ電圧の増大防止または低下を図り、保護用MOSトランジスタのゲート電位が変動しにくい保護回路を有する半導体集積回路及び製造方法を提供する。

【解決手段】RCMOS型のESD保護回路1において、保護用MOSトランジスタ5は、内部回路6の内のチャネルの導電型が同じトランジスタに対して、仕事関数差を有する異なる電極材料からゲート電極が形成され、または、仕事関数差を設けるために異なる導電型の半導体電極材料からゲート電極が形成されることによって、単位チャネル幅あたりのリーク電流量が、より減る向きに閾値電圧が異なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に歪みを導入して半導体装置の特性を向上するとともに、応力印加膜に覆われたゲート配線の断線を防止する。

【解決手段】半導体装置は、第1の素子形成領域101に形成された第1の活性領域104と、第2の素子形成領域102に形成された第2の活性領域105と、第1の活性領域104上から第2の活性領域105上に亘って延伸するゲート配線103と、第1の活性領域104のうちゲート配線103の直下領域に形成された第1のチャネル領域80と、第2の活性領域のうちゲート配線の直下領域に形成された第2のチャネル領域90とを備える。ゲート配線103は、第1の活性領域104上に形成され、引張り応力又は圧縮応力である第1の応力を有する第1の領域164と、第1の領域164よりも緩和された第1の応力を有する第2の領域162とを有している。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】溝部および該溝部を挟んで形成された一対の低抵抗領域を有する半導体基板と、半導体基板上の第1のゲート絶縁膜と、第1のゲート絶縁膜を介し、溝部と重畳するゲート電極と、ゲート電極を覆って設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜上の、溝部を挟んで設けられた一対の電極と、一対の電極と接する半導体膜と、を有し、一対の低抵抗領域の一方と、一対の電極の一方が電気的に接続されている積層されたトランジスタを形成し、一方はn型半導体からなるトランジスタであり、他方はp型半導体からなるトランジスタにより形成させることによって、相補型MOS回路を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させる。

【解決手段】ゲート電極GE1,GE2、ソース・ドレイン用のn+型半導体領域SD1及びp+型半導体領域SD2を形成してから、半導体基板1上にNi−Pt合金膜を形成し、第1の熱処理を行って合金膜とゲート電極GE1,GE2、n+型半導体領域SD1及びp+型半導体領域SD2とを反応させることで、(Ni1−yPty)2Si相の金属シリサイド層13aを形成する。この際、Niの拡散係数よりもPtの拡散係数の方が大きくなる熱処理温度で、かつ、金属シリサイド層13a上に合金膜の未反応部分が残存するように、第1の熱処理を行う。その後、未反応の合金膜を除去してから、第2の熱処理を行って金属シリサイド層13aを更に反応させることで、Ni1−yPtySi相の金属シリサイド層13bを形成する。第2の熱処理の熱処理温度は580℃以上で、800℃以下とする。

(もっと読む)

半導体装置の製造方法

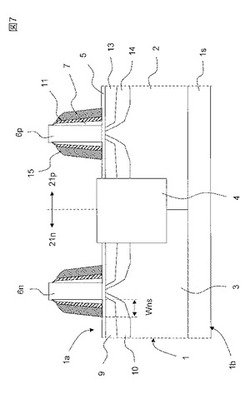

【課題】 CMOS型半導体装置におけるデュアルゲート構造のゲート電極をエッチングにより形成する時に、局所的なゲート絶縁膜の「突き抜け」やゲート電極サイドエッチ等の欠陥が発生することを防止できる製造方法を提供する。

【解決手段】 ゲート絶縁膜5を介して半導体基板1上に形成されたシリコン膜等の、実質的に不純物を含まない半導体膜6を選択的にエッチングしてゲート電極7を形成する。隣接するゲート電極7間の領域をレジスト等の絶縁膜9で埋め込む。さらに例えば所定のゲート電極7が形成された領域を覆うマスク層10を形成し、絶縁膜9とマスク層10とをマスクとして、マスク層10で覆われないゲート電極7にイオン注入等の手段により所定導電型の不純物を導入する。同様の方法を用いてマスク層10で覆われていたゲート電極7に異なる導電型の不純物を導入する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能向上を図る。

【解決手段】ゲート電極GE1,GE2,GE3,GE4の側壁上にオフセットスペーサを形成した状態で半導体基板1のnMIS領域1A,1BおよびpMIS領域1C,1Dのそれぞれにイオン注入を行うことで、ソース・ドレインのエクステンション領域を形成する。この際、nMIS領域1A,1BおよびpMIS領域1C,1Dのそれぞれに対して別々のフォトレジストパターンを用いて個別にイオン注入を行うが、フォトレジストパターンを形成し直す度に、オフセットスペーサを形成し直すようにする。

(もっと読む)

半導体装置およびその製造方法

【課題】 層間絶縁膜をCMP法で研磨、平坦化する際、MOS型トランジスタのチャネル領域に応力を与えるためにゲート電極を覆うように形成される応力ライナー膜が研磨されて、トランジスタ特性の変動やバラツキが発生しないようにする。

【解決手段】 第1活性領域(例えばPチャネルトランジスタ形成領域)上のゲート電極(シリコン膜14と金属シリサイド膜15との積層膜)上には第1応力膜(圧縮応力ライナー膜)16のみを形成し、第2活性領域(例えばNチャネルトランジスタ領域)上のゲート電極上には第2応力膜(引っ張り応力ライナー膜)18のみを形成する。一方、素子分離10上のゲート電極上には第1および第2応力膜16、18の積層膜を形成する。層間絶縁膜20のCMP法による研磨は、素子分離10上の第2応力膜18の露出後に停止する。

(もっと読む)

アクティブ発振防止付き複合半導体デバイス

【課題】アクティブ発振防止付き複合半導体デバイスを提供する。

【解決手段】本明細書は、アクティブ発振制御付き複合半導体デバイスの種々の実現を開示する。1つの好適な実現では、ノーマリオフ複合半導体デバイスが、ノーマリオンIII-窒化物パワートランジスタ、及びこのノーマリオンIII-窒化物パワートランジスタとカスコード接続された低電圧(LV)デバイスを具えて、ノーマリオフ複合半導体デバイスを形成する。このLVデバイスは、例えば修正したボディ打込み領域により低減した出力抵抗、及び例えば修正した酸化物の厚さにより低減したトランスコンダクタンスの一方または両方を含むように構成されて、複合半導体デバイスのゲインを約10,000以下にすることができる。

(もっと読む)

CVDエッチングおよび堆積シーケンスにより形成されるCMOSトランジスタ接合領域

【課題】CMOSトランジスタのソース−ドレイン置換技術に関し、装置一式を利用して基板材料に窪みをエッチングして、その後、応力を有する異なる材料を堆積することに関し、大気に曝すことなく、エッチングとその後の堆積とを行う方法の提供。

【解決手段】エッチングおよびデポジションによりCMOSトランジスタの接合領域を形成する方法であって、

第1接合領域270を形成すべくゲート電極190の隣の基板120の第1箇所と、前記基板120に第2接合領域280を形成すべく前記ゲート電極190を介して前記第1箇所とは反対側に位置する前記基板120の第2箇所とを除去する工程と、前記第1接合領域270と前記第2接合領域280とに結晶質材料のエピタキシャル厚みを有する層を形成する工程とを含み、前記除去する工程と前記形成する工程は同一のチャンバ内で前記チャンバの封止を破ることなく行う。

(もっと読む)

電界効果トランジスタ及びその製造方法、並びに半導体装置

【課題】横型二重拡散構造を有する電界効果トランジスタの高集積化を可能とする半導体装置を提供する。

【解決手段】半導体装置1Nは、ゲート電極17の幅方向両側のうちの一方の側で延在するP型ボディ領域20Pと、他方の側で延在するN型ボディ領域20Nと、その一方の側に形成されてP型ボディ領域20Pと接合するP型不純物拡散領域32Pと、その他方の側でP型不純物拡散領域32Pと対向する位置に形成されてN型ボディ領域20Nと接合するN型不純物拡散領域32Nと、その一方の側に形成されてP型ボディ領域30Nと接合するN型不純物拡散領域31Nと、その他方の側でN型不純物拡散領域31Nと対向する位置に形成されてN型ボディ領域20Nと接合するP型不純物拡散領域31Pとを備える。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体装置および基準電圧生成回路

【課題】所望の温度特性を有することによって回路規模を小さくできるMOSトランジスタを提供する。

【解決手段】ゲート電極はP型半導体層及びN型半導体層からなるので、P型半導体層とN型半導体層との接合面に、空乏層13が生じる。温度が変化すると、空乏層13の領域の面積が変化し、P型半導体層11及びN型半導体層12の領域の面積もそれぞれ変化することで、MOSトランジスタに所望の温度特性を与えられる。その結果、温度補正回路を簡単にする、あるいは不要にすることができる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性と電気的特性の確保を両立した半導体装置を提供する。

【解決手段】同一の半導体基板1上に形成されたパワーMOSFETと保護回路を備える。パワーMOSFETがトレンチゲート縦型PチャネルMOSFETであって、そのゲート電極6の導電型をP型とする。また、保護回路がプレーナゲート横型オフセットPチャネルMOSFETを備え、そのゲート電極10の導電型をN型とする。これらゲート電極6とゲート電極10は別工程で形成される。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】寄生バイポーラトランジスタのゲインを低下することにより、誤動作や動作特性の変動が少ない半導体装置及びその製造方法を得る。

【解決手段】シリコン層3の上面上には、シリコン酸化膜6が部分的に形成されている。シリコン酸化膜6上には、ポリシリコンから成るゲート電極7が部分的に形成されている。ゲート電極7の下方に存在する部分のシリコン酸化膜6は、ゲート絶縁膜として機能する。ゲート電極7の側面には、シリコン酸化膜8を挟んで、シリコン窒化膜9が形成されている。シリコン酸化膜8及びシリコン窒化膜9は、シリコン酸化膜6上に形成されている。ゲート長方向に関するシリコン酸化膜8の幅W1は、シリコン酸化膜6の膜厚T1よりも大きい。

(もっと読む)

不揮発性メモリ装置

【課題】一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供することによって、読出しマージン減少による信頼性の下落を防止できる不揮発性メモリ装置が提供される。

【解決手段】本発明の実施形態による不揮発性メモリ装置は、基板と直交する方向に積層された複数のメモリセルを含むメモリセルアレイと、ワードラインを通じて前記メモリセルアレイに連結された行選択回路と、前記ワードラインに提供される電圧を発生する電圧発生回路と、を含み、前記電圧発生回路は、目標電圧レベルまで段階的に増加させる方式に前記電圧を発生する。本発明の実施形態による不揮発性メモリ装置は、一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供できる。したがって、読出しマージン減少による信頼性の下落が防止され得る。

(もっと読む)

電界効果トランジスタを備える半導体素子及びその製造方法

【課題】電界効果トランジスタを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成され、第1活性領域の上面及び向き合う側面を経て伸張する第1ゲート電極を有する第1導電型の第1FET素子と、前記第1FET素子上に形成された層間絶縁膜と、前記層間絶縁膜上に形成され、第2活性領域の上面及び向き合う側面を経て伸張する第2ゲート電極を有する第2導電型の第2FET素子と、を備える。

(もっと読む)

半導体装置

【課題】集積回路の動作速度の向上に有利な技術を提供する。

【解決手段】n型トランジスタおよびp型トランジスタがシリコンの(551)面に形成された半導体装置において、前記n型トランジスタの拡散領域に接触するシリサイド層の厚さが前記p型トランジスタの拡散領域に接触するシリサイド層の厚さよりも薄い。

(もっと読む)

21 - 40 / 956

[ Back to top ]