Fターム[5F048BB07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | 多結晶Si (4,558) | P型ドープ多結晶Si (956)

Fターム[5F048BB07]に分類される特許

61 - 80 / 956

半導体装置及びその製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38上に第1ストッパ膜39及び第2ストッパ膜40を形成する工程と、第1領域2を覆う第1マスク60をマスクとし、第1ストッパ膜をストッパとして、第2領域4内の第2ストッパ膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の第2ストッパ膜をサイドエッチングする工程と、第2ストッパ膜とエッチング特性が異なる第2応力膜42を形成する工程と、第2領域を覆い、第1領域側の端面が第2ストッパ膜上に位置する第2マスクとし、第2ストッパ膜をストッパとして、第2応力膜の一部が第1応力膜の一部及び第2ストッパ膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

高電圧動作電界効果トランジスタとそのバイアス回路およびその高電圧動作回路要素

【課題】 ICまたはLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該IC中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートにドレイン電位に応じて変化する電位分布を設ける手段をとる。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

MOSトランジスタおよびその製造方法、半導体集積回路装置

【課題】MOSトランジスタのチャネル領域に、基板上に形成した応力膜からより効率的に応力を印加する半導体装置の構造及びその製造方法を提供する。

【解決手段】MOSトランジスタは、n型またはp型のソース・ドレイン領域21e〜hと、素子分離領域21Iからチャネル領域に向かって延在し、ソース・ドレイン領域21e〜hを覆って形成された、引張応力、圧縮応力のいずれかである応力膜27A、27Bを備える。応力膜27A,27Bは、ゲート電極23A,23Bの側壁面に沿って、ただし側壁面からは隙間32A〜Dを介して形成される。ソース・ドレイン領域21e〜hがn型である場合、応力膜の応力は引張応力であり、ソース・ドレイン領域21e〜hがp型である場合、応力膜の応力は圧縮応力である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】規則的に配列した複数の微細な開口部OPを有するフィルタFLを通過したイオンビーム22をレンズ26で収束して半導体ウエハ1Wに照射することにより、チャネルドープイオン注入を行なう。この際、フィルタFLには、イオンビーム22と同じ極性の電圧を印加する。フィルタFLの開口部OPの中央部に向かって入射した不純物イオンは、そのまま直進して開口部OPを通過することができるが、フィルタFLの開口部OPの中央部以外の領域に向かって入射する不純物イオンは、フィルタFLによる電場によって進行方向が曲げられて、開口部OPを通過することができない。このため、半導体ウエハ1Wに注入された不純物イオンは、規則的な配列を有したものとなり、MISFETのしきい値電圧のばらつきを抑制できる。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】p型MOSトランジスタの半導体埋め込み領域形成に付随する不具合が抑制される技術を提供する。

【解決手段】半導体装置の製造方法は、n型、p型MOSトランジスタの配置される第1、第2活性領域にまたがりシリコンでゲート電極を形成する工程と、第1活性領域とその近傍のゲート電極へのn型不純物注入工程と、第2活性領域及びその近傍のゲート電極を露出するマスクの形成工程と、マスク開口内の第2活性領域及びゲート電極をエッチングする凹部形成工程と、凹部表面の自然酸化膜を除去しこれに伴い開口が後退する工程と、凹部表面をハロゲンガスでクリーニングする工程と、凹部への半導体埋め込み領域形成工程とを有し、クリーニング工程時に後退した開口内にゲート電極上n型領域が露出していないように、ゲート電極上n型領域の第2活性領域側の端とマスク開口の第1活性領域側の縁とが離される。

(もっと読む)

半導体薄膜基板および半導体薄膜基板を用いた半導体装置の作製方法

【課題】一層の半導体層から膜厚の異なる半導体層を有する半導体薄膜基板を提供することを目的の一とする。または、半導体薄膜基板を適用した半導体装置を提供することを目的の一とする。

【解決手段】基板上に半導体層を形成し、半導体層を加工して第1の島状半導体層および第2の島状半導体層を形成し、第1の島状半導体層にレーザー照射を行うことにより第1の島状半導体層を溶融させ、第1の島状半導体層から第2の島状半導体層より膜厚が厚い第3の島状半導体層を形成する、半導体薄膜基板の作製方法である。

(もっと読む)

半導体装置

【課題】キャリアのライフタイム制御に関わらず、寄生バイポーラトランジスタの動作を抑制し、耐量を向上させることができる構造の半導体装置を提供する。

【解決手段】ダイオード構造が形成された領域において、n-型ドリフト層1の裏面側に、p+型不純物領域2だけでなく部分的にn+型不純物領域3を形成する。これにより、p+型不純物領域2の幅が狭くなり、その結果、p+型不純物領域2のうちn+型不純物領域3との境界部から最も離れる場所までの距離が短くなる。したがって、n-型ドリフト層1の内部抵抗が小さくなることでバイアス電圧が小さくなり、寄生バイポーラトランジスタの動作を抑制することが可能となる。よって、キャリアのライフタイム制御に関わらず、寄生バイポーラトランジスタの動作を抑制し、耐量を向上させることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】電源配線の電位の変動に起因するボディ領域の電位の変動を抑制し得る半導体装置を得る。

【解決手段】シリコン層4の上面内には、パーシャルトレンチ型の素子分離絶縁膜5が選択的に形成されている。電源配線21は、素子分離絶縁膜5の上方に形成されている。電源配線21の下方において、素子分離絶縁膜5には、絶縁層3の上面に達する完全分離部分23が形成されている。換言すれば、半導体装置は、電源配線21の下方において、シリコン層4の上面から絶縁層3の上面に達して形成された完全分離型の素子分離絶縁膜を備えている。

(もっと読む)

半導体集積回路装置

【課題】ゲート絶縁膜の厚さが異なる複数種類の電界効果トランジスタを有する半導体集積回路装置の信頼性を高める。

【解決手段】第1の電界効果トランジスタQ3及び第2の電界効果トランジスタQ4は埋込絶縁膜25によって分離され、ゲート絶縁膜31,32は各々熱酸化膜27、30と堆積膜27,28,29が積層され、第1の電界効果トランジスタの熱酸化膜は第2の電界効果トランジスタの熱酸化膜より厚く、各トランジスタの堆積膜は、各々各トランジスタの熱酸化膜よりも厚く構成され、第1の電界効果トランジスタのゲート電極は、ゲート幅方向における端部が埋込絶縁膜上に引き出され、かつ端部と埋込絶縁膜との間に第1の電界効果トランジスタの堆積膜が設けられ、第2の電界効果トランジスタのゲート電極は、ゲート幅方向における端部が埋込絶縁膜上に引き出され、かつ前記端部と埋込絶縁膜との間に第2の電界効果トランジスタの堆積膜が設けられる。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多層配線構造を使って、キャパシタンスが大きく、かつキャパシタンス値が安定なキャパシタ素子を半導体基板上に集積化する。

【解決手段】多層配線構造18は、少なくとも第1層目の層間絶縁膜16と、第1層目の層間絶縁膜中に埋設された第1配線層と、を含み、第1配線層は、第1の電源に接続され前記第1の層間絶縁膜中に埋設された第1の配線パタ―ン15C1と、第2の電源に接続され前記第1の層間絶縁膜中に埋設された第2の配線パタ―ン15C2と、を含み、第1の配線パタ―ンと前記第2の配線パタ―ンとは容量結合して第1のキャパシタを形成し、第1の配線パタ―ンは積層配線パタ―ン13C上に形成されて、前記第4の電極パターン13Gと容量結合して第2のキャパシタを形成し、第4の電極パターンは第2の配線パタ―ンに電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート電極GEと上部に金属シリサイド層11bが形成されたソース・ドレイン領域とを有するMISFETが半導体基板1の主面に複数形成されている。金属シリサイド層11bは、Pt,Pd,V,Er,Ybからなる群から選択された少なくとも一種からなる第1金属元素およびニッケルのシリサイドからなる。半導体基板1の主面に形成された複数のMISFETのソース・ドレイン領域のうち、ゲート長方向に最も近接して隣り合うゲート電極GE間に配置されたソース・ドレイン領域のゲート長方向の幅W1cよりも、金属シリサイド層11bの粒径が小さい。

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】NMOSFETにSiGe層が成長されることを抑制し、かつPMOSFETのSiGe層の形状不良の発生を抑止する。

【解決手段】半導体装置の製造方法は、半導体基板の第1領域に第1ゲート電極6Aを形成し、前記半導体基板の第2領域に第2ゲート電極6Bを形成し、前記第1ゲート電極の側壁に第1サイドウォール12Aを形成し、前記第2ゲート電極の側壁に第2サイドウォール12Bを形成し、前記半導体基板、前記第1ゲート電極、前記第2ゲート電極、前記第1サイドウォール及び前記第2サイドウォールを覆うように酸化膜20を形成し、前記酸化膜上に、前記第1領域を覆うようにレジストを形成し、前記レジストをマスクとして前記酸化膜20をエッチングすることにより、前記第2領域の前記酸化膜20を除去し、前記レジストを除去し、前記半導体基板及び前記第1領域の前記酸化膜20に対して、塩素を含むガスを用いてプラズマ処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】デュアルゲート構造を有する半導体装置の製造技術において、MISFETのしきい値電圧の上昇を抑制することができる製造技術を提供する。

【解決手段】ポリシリコン膜PF1上にレジスト膜FR2を形成する。そして、レジスト膜FR2に対して露光・現像処理を施すことにより、レジスト膜FR2をパターニングする。その後、パターニングしたレジスト膜FR2をマスクにしたイオン注入法により、露出しているnチャネル型MISFET形成領域NTRのポリシリコン膜PF1にアルゴン(Ar+)を導入する。このアルゴン注入工程により、nチャネル型MISFET形成領域NTRのポリシリコン膜PF1はアモルファス化する。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】全反応方式のサリサイドプロセスを用いず、部分反応方式のサリサイドプロセスによりゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の熱処理では、ランプまたはレーザを用いたアニール装置ではなく、カーボンヒータを用いた熱伝導型アニール装置を用いて半導体ウエハを熱処理することにより、少ないサーマルバジェットで精度良く薄い金属シリサイド層41を形成し、最初の熱処理によって金属シリサイド層41内にNiSiの微結晶を形成する。

(もっと読む)

デュアルドープゲートの用途におけるプロフィル制御とN/Pローディングを改善する方法

【課題】プラズマエッチングチャンバ内でデュアルドープゲート構造をエッチングするための方法を提供する。

【解決手段】エッチングされるポリシリコンフィルムを保護するパターンを設ける工程、次いで、プラズマが点火され、保護されていないポリシリコンフィルムのほぼすべてがエッチングされる。次いで、シリコン含有ガスを導入しつつポリシリコンフィルムの残りをエッチングする。また、エッチング処理中にシリコン含有ガスを導入するよう構成されたエッチングチャンバ。

(もっと読む)

半導体集積回路装置

【課題】ゲート絶縁膜の一部を高誘電体膜で構成した場合に好適な2種ゲート構造を提供する。

【解決手段】基板1上に窒化シリコン膜よりも比誘電率が大きい高誘電体膜、例えば酸化チタン膜6(内部回路のゲート絶縁膜)を堆積した後、酸化チタン膜6の上部に窒化シリコン膜7を堆積する。窒化シリコン膜7は、次の工程で基板1の表面を熱酸化する時に酸化チタン膜6が酸化されるのを防ぐ酸化防止膜として機能する。次に、内部回路領域に窒化シリコン膜7と酸化チタン膜6を残し、I/O回路領域の窒化シリコン膜7と酸化チタン膜6を除去した後、基板1を熱酸化することによって、I/O回路領域の基板1の表面に酸化シリコン膜8(I/O回のゲート絶縁膜)を形成する。

(もっと読む)

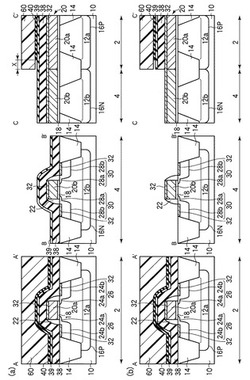

半導体装置及びその製造方法

【課題】N型トランジスタ及びP型トランジスタの双方で可及的に製造工程を共通にして、工程数の可及的な削減を図るも、N型トランジスタ及びP型トランジスタの夫々に適合した応力を適宜印加し、トランジスタ性能の大幅な向上を実現する。

【解決手段】N型トランジスタでは、ゲート電極14a及びサイドウォール絶縁膜17を覆うようにN型領域10aの全面に引張応力膜22を形成し、P型トランジスタでは、サイドウォール17絶縁膜上のみに引張応力膜22を形成し、更にゲート電極14b及び引張応力膜22を覆うようにP型領域10bの全面に圧縮応力膜24を形成する。

(もっと読む)

61 - 80 / 956

[ Back to top ]