Fターム[5F048BD01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | チャネル (4,415) | 形状 (1,258)

Fターム[5F048BD01]の下位に属するFターム

チャネル長(幅) (272)

Fターム[5F048BD01]に分類される特許

121 - 140 / 986

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 LDMOS型トランジスタなどの半導体装置が動作中に生ずる経時的な特性変動を抑制すると共に、高耐圧かつ低オン抵抗が実現される半導体装置およびその製造方法を提供する。

【解決手段】 N型半導体層102に、深さが1μmより小さいP型の第1ドレインオフセット領域103と、深さが第1ドレインオフセット領域103より小さく、不純物濃度が第1ドレインオフセット領域103より大きいP型の第2ドレインオフセット領域105と、第1ドレインオフセット領域103より深いN型のボディ領域106と、N型のソース領域107およびドレイン領域104とを設ける。またLOCOS酸化膜からなる絶縁膜110と、ゲート絶縁膜108を介して形成されたゲート電極109とをN型半導体層102上に備える構造とする。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置の作製工程数を減少させること、半導体装置の歩留まりを向上させること、半導体装置の作製コストを低減することを課題とする。

【解決手段】基板上に、単結晶半導体層をチャネル形成領域に有する第1のトランジスタと、当該第1のトランジスタと絶縁層を介して分離され、酸化物半導体層をチャネル形成領域に有する第2のトランジスタと、当該単結晶半導体層及び酸化物半導体層を有するダイオードを有する半導体装置、及び、その作製方法に関する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の向上に寄与し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10にトランジスタ36を形成する工程と、半導体基板上に、トランジスタを覆う第1のシリコン窒化膜38を形成する工程と、第1のシリコン窒化膜にNH4Fラジカルを供給する工程と、NH4Fラジカルを供給する工程の後、第1のシリコン窒化膜に対して熱処理を行う工程と、熱処理を行う工程の後、第1のシリコン窒化膜上に第2のシリコン窒化膜を形成する工程とを有している。

(もっと読む)

垂直TFETの製造方法

【課題】ヘテロ構造ナノワイアを有するトンネル電界効果トランジスタと集積されたナノワイアを有する相補型トンネル電界効果トランジスタの製造方法を提供する。

【解決手段】犠牲材料21の層を有するチャネル材料34の層を含むスタック24を形成する工程と、チャネル材料34の層と犠牲材料21の層から、少なくとも1つのナノワイヤ30を形成するために、スタック24から材料を除去する工程と、第1ドーパント型の少なくとも1つのナノワイヤ30中の犠牲材料21を第1ドーパント型のヘテロ接合材料41で置き換えて、その後に、第2ドーパント型の少なくとも1つのナノワイア中の犠牲材料を、第2ドーパント材料のヘテロ接合材料52で置き換える工程を含み、相補型TFETの容易な製造が可能となる。

(もっと読む)

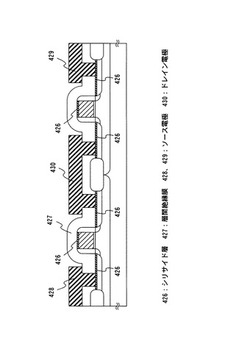

半導体装置及びその製造方法

【課題】SOI構造の縦型のMISFETの提供

【解決手段】Si基板1上に、一部に空孔4を有する絶縁膜2が設けられ、空孔4上及び絶縁膜2の一部上に横方向半導体層6が設けられ、半導体層6の側面の一部に導電膜3が接して設けられ、絶縁膜2により素子分離されている。半導体層6上の、空孔4直上部に縦方向半導体層7が設けられ、半導体層7の上部にドレイン領域(10,9)が設けられ、離間し、相対して下部にソース領域8が設けられ、ソース領域8は延在して、半導体層6全体に設けられている。半導体層7の全側面には、ゲート酸化膜11を介してゲート電極12が設けられ、ドレイン領域10、ゲート電極11及び導電膜3を介したソース領域8には、バリアメタル18を有する導電プラグ19を介してバリアメタル21を有する配線22が接続されている縦型のMISFET。

(もっと読む)

半導体装置及び電子機器

【課題】逆スタガ型TFTにおいて、薄膜の応力を用いてしきい値電圧を制御する。

【解決手段】基板上に形成された電極上に設けられた第1の絶縁層の応力と膜厚の積と、前記第1の絶縁層上に設けられた引張り応力を有する結晶質半導体膜からなる活性層の応力と膜厚の積と、前記活性層上に設けられた第2の絶縁層の応力と膜厚の積を適当な大きさに設定することでしきい値電圧を制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート電極GEと上部に金属シリサイド層11bが形成されたソース・ドレイン領域とを有するMISFETが半導体基板1の主面に複数形成されている。金属シリサイド層11bは、Pt,Pd,V,Er,Ybからなる群から選択された少なくとも一種からなる第1金属元素およびニッケルのシリサイドからなる。半導体基板1の主面に形成された複数のMISFETのソース・ドレイン領域のうち、ゲート長方向に最も近接して隣り合うゲート電極GE間に配置されたソース・ドレイン領域のゲート長方向の幅W1cよりも、金属シリサイド層11bの粒径が小さい。

(もっと読む)

電気光学装置及び電子機器、並びに電気光学装置の製造方法

【課題】液晶装置等の電気光学装置において、TFTで発生する光リーク電流を低減させ

る。

【解決手段】電気光学装置は、表示領域(10a)に設けられた複数の画素電極(9a)

と、画素電極に画像信号を供給するデータ線(6a)と、画素電極に電気的に接続された

画素電極側ソースドレイン領域(1e)、データ線に電気的に接続されたデータ線側ソー

スドレイン領域(1d)、並びに画素電極側ソースドレイン領域及びデータ線側ソースド

レイン領域間に位置するチャネル領域(1a’)を有する半導体層(1a)と、半導体層

のチャネル領域にゲート絶縁膜(2a,2b)を介して対向配置されたゲート電極(3b

)とを備える。半導体層は、チャネル領域の膜厚が、画素電極側ソースドレイン領域及び

データ線側ソースドレイン領域の膜厚より薄くなるように形成されている。

(もっと読む)

半導体装置の製造方法

【課題】NMOSFETにSiGe層が成長されることを抑制し、かつPMOSFETのSiGe層の形状不良の発生を抑止する。

【解決手段】半導体装置の製造方法は、半導体基板の第1領域に第1ゲート電極6Aを形成し、前記半導体基板の第2領域に第2ゲート電極6Bを形成し、前記第1ゲート電極の側壁に第1サイドウォール12Aを形成し、前記第2ゲート電極の側壁に第2サイドウォール12Bを形成し、前記半導体基板、前記第1ゲート電極、前記第2ゲート電極、前記第1サイドウォール及び前記第2サイドウォールを覆うように酸化膜20を形成し、前記酸化膜上に、前記第1領域を覆うようにレジストを形成し、前記レジストをマスクとして前記酸化膜20をエッチングすることにより、前記第2領域の前記酸化膜20を除去し、前記レジストを除去し、前記半導体基板及び前記第1領域の前記酸化膜20に対して、塩素を含むガスを用いてプラズマ処理を行う。

(もっと読む)

半導体装置

【課題】高さの異なる複数の素子形成面に形成された半導体素子の電気特性を均一化する。

【解決手段】半導体装置Sは、高さの異なる複数の素子形成面50が段差状に形成された半導体層1と、素子形成面50を含む各領域にそれぞれ形成された半導体素子51,52と、半導体層1に対し、半導体素子51,52を覆うと共に素子形成面50に沿った段差状の表面を有する段差補償絶縁膜28とを備えている。そして、各素子形成面50における半導体層1は、互いに同じ厚みに形成されている。

(もっと読む)

半導体装置

【課題】 工程の増加や占有面積の増加もなくオフリーク電流を小さく抑えた、十分なESD保護機能を持たせたシャロートレンチ分離構造を有するESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】 素子分離にシャロートレンチ分離領域501を有するESD保護用のN型MOSトランジスタにおいて、ESD保護用のN型MOSトランジスタのゲート電極301下面のゲート絶縁膜を介してP型シリコン基板表面に形成されたチャネル領域の表面に、ESD保護用のN型MOSトランジスタのドレイン領域202から一定の距離を隔てたオフセット領域601を介して、濃いP型の不純物濃度領域からなるP型ブレークダウン領域401を形成した半導体装置とした。

(もっと読む)

半導体装置及びその製造方法

【課題】N型トランジスタ及びP型トランジスタの双方で可及的に製造工程を共通にして、工程数の可及的な削減を図るも、N型トランジスタ及びP型トランジスタの夫々に適合した応力を適宜印加し、トランジスタ性能の大幅な向上を実現する。

【解決手段】N型トランジスタでは、ゲート電極14a及びサイドウォール絶縁膜17を覆うようにN型領域10aの全面に引張応力膜22を形成し、P型トランジスタでは、サイドウォール17絶縁膜上のみに引張応力膜22を形成し、更にゲート電極14b及び引張応力膜22を覆うようにP型領域10bの全面に圧縮応力膜24を形成する。

(もっと読む)

フィン型電界効果トランジスタおよびその製造方法

【課題】フィン型電界効果トランジスタおよびその製造方法を提供する。

【解決手段】半導体基板より上に延伸したfinFETの第1および第2のフィン206を、その間にシャロートレンチアイソレーション(STI)領域202、およびSTI領域の上面と第1および第2のフィンの上面との間の距離を有して、形成するステップ、STI領域の上面より上の第1および第2のフィンの上面および側面に第1および第2のフィン延伸部を提供するステップ、STI領域から材料を除去し、STI領域の上面と第1および第2のフィンの上面との間の距離を増加させるステップ、フィンおよびSTI領域上に共形のストレッサ誘電材料214を堆積するステップ、および共形のストレッサ誘電材料をSTI領域の上面より上の第1および第2のフィンの間の空間内に流入するようにリフローし、finFETのチャネルに応力を加えるステップを含む方法。

(もっと読む)

応力発生膜を含む半導体装置の製造方法、および設計方法

【課題】応力発生膜の形状に依存して、半導体装置製造時の半導体装置の回路部品の特性がマクロセル設計段階での半導体装置の回路部品の特性から変動することを極力抑制する。

【解決手段】応力発生膜の延在方向の寸法の変更量に対する、半導体装置の特性の変化量が所定の限度で飽和する延在方向の寸法を目標延在寸法として設定する工程と、半導体装置内で応力発生膜の末端からゲートに至るまでの寸法が少なくとも目標延在寸法となるように応力発生膜を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な電気的特性を有する半導体装置及びその製造方法を提供する。

【解決手段】質量数が比較的小さいドーパント不純物を導入することにより第1のトランジスタ34a及び第2のトランジスタ34bのチャネルドープ層18を形成する工程と、質量数が比較的大きいドーパント不純物を導入することにより第3のトランジスタ34cのチャネルドープ層20を形成する工程と、質量数の比較的小さいドーパント不純物を導入することにより第1のトランジスタのポケット領域26を形成する工程と、質量数の比較的大きいドーパント不純物を導入することにより第2のトランジスタ及び第3のトランジスタのポケット領域36を形成する工程とを有している。

(もっと読む)

半導体装置

【課題】Si混晶層における選択成長用マスクの開口率の違いによりエピタキシャル成長が不均一となることを防止すると共に、半導体素子のキャリア移動度を向上できるようにする。

【解決手段】半導体装置は、半導体基板100の上部に形成された素子分離膜101と、素子分離膜に囲まれてなる素子活性領域102と、該素子活性領域102に形成され正孔をキャリアとするチャンネル領域100aとを有するP型MIS−FET200Pと、素子分離膜における素子活性領域102の周辺部に形成された複数のダミー活性領域105とを備えている。複数のダミー活性領域105のうち、正孔の移動方向と対向する位置に形成されたダミー活性領域のみをシリコンとゲルマニウムとを含むSiGe付きダミー活性領域106としている。

(もっと読む)

半導体装置およびその製造方法

【課題】閾値電圧が低く、かつ、ゲート絶縁膜のリーク電流を抑制可能な半導体装置およびその製造方法を提供する。

【解決手段】メタルゲート電極103,203の材料として、Ta3N5を含むTaxNy膜18,38を用いる。TaxNy膜18,38中には多くの窒素が含まれており、その窒素の一部がゲート絶縁膜102,202中に拡散することにより、TiNに比べてフラットバンド電圧Vfbが高くなり、NMOSFET100およびPMOSFET200の閾値電圧Vthを低くすることができる。また、TaxNy膜18,38中の窒素がHfSiON膜17,37中に拡散することにより、ゲート絶縁膜の絶縁性を高くすることができ、ゲートリーク電流Jgを抑制できる。

(もっと読む)

フィン型FETを有する半導体装置およびその製造方法

【課題】横方向延伸を減少し、素子サイズを小さくすることができる半導体装置を提供する。

【解決手段】半導体基板上に延伸し、STI領域を間に有する第1および第2のフィンを形成する。STI領域の上面と第1および第2のフィンの上面の間の寸法を第1の高さとし、STI領域の第1と第2のフィンとの間の間隙内に誘電材料を堆積し、STI領域の上面上に上面を有して、誘電材料の上面と第1および第2のフィンの上面との寸法を第2の高さとし、第2の高さは、第1の高さより低くなるように誘電材料を堆積した後、第1および第2のフィン上でそれぞれ誘電体の上方に、第1および第2のフィン延伸をエピタキシャル成長で形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トンネルFETの閾値ばらつきの抑制をはかる。

【解決手段】Si1-x Gex (0<x≦1)の第1の半導体層13上にゲート絶縁膜21を介して形成されたゲート電極22と、Geを主成分とする第2の半導体と金属との化合物で形成されたソース電極24と、第1の半導体と金属との化合物で形成されたドレイン電極25と、ソース電極24と第1の半導体層13との間に形成されたSi薄膜26とを具備した半導体装置であって、ゲート電極22に対しソース電極24のゲート側端部とドレイン電極25のゲート側端部とは非対称の位置関係にあり、ドレイン電極25のゲート側の端部の方がソース電極24のゲート側の端部よりも、ゲート電極22の端部からゲート外側方向に遠く離れている。

(もっと読む)

121 - 140 / 986

[ Back to top ]