Fターム[5F048BD01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | チャネル (4,415) | 形状 (1,258)

Fターム[5F048BD01]の下位に属するFターム

チャネル長(幅) (272)

Fターム[5F048BD01]に分類される特許

81 - 100 / 986

半導体装置

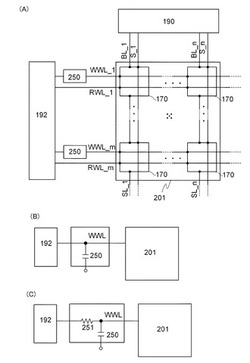

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込みワード線に電気的に接続する容量素子またはノイズ除去回路を設けることで、駆動回路等からメモリセルに入力されうる制御信号とは異なる短パルスやノイズ等の信号を低減または除去することができる。これにより、メモリセルが有するトランジスタが瞬間的にオンすることでメモリセルに書き込まれたデータが消失してしまう誤動作を防ぐことが可能である。

(もっと読む)

半導体装置

【課題】転位ループが発生するおそれがあるダミーパターン領域を有しながらも、転位ループによる基板上の他の素子等への悪影響が抑えられた半導体装置を提供する。

【解決手段】一実施の形態による半導体装置は、基板上に形成された素子分離絶縁膜と、前記素子分離絶縁膜により前記基板上に区画された素子領域およびダミーパターン領域と、前記素子領域内の前記基板上に形成された第1のエピタキシャル結晶層と、前記ダミーパターン領域内の前記基板上に形成された第2のエピタキシャル結晶層と、を有する。第1のエピタキシャル結晶層は前記基板を構成する結晶と異なる格子定数を有する結晶からなる。第2のエピタキシャル結晶層は前記第1のエピタキシャル結晶層と同じ結晶からなる。前記第2のエピタキシャル結晶層と前記基板との界面上の任意の点を含む前記基板の(111)面は、前記第2のエピタキシャル結晶層よりも深い領域で前記素子分離絶縁膜に囲まれる。

(もっと読む)

半導体装置及びその製造方法

【課題】低電圧トランジスタ及び高電圧トランジスタの双方の要求を満たし、高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】ボロン又はリンを含む第1の不純物層と、第1の不純物層上に形成された第1のエピタキシャル層と、第1のエピタキシャル層上に第1のゲート絶縁膜を介して形成された第1のゲート電極と、第1のソース/ドレイン領域とを有する第1のトランジスタと、ボロン及び炭素又は砒素を含む第2の不純物層と、第2の不純物層上に形成された第2のエピタキシャル層と、第2のエピタキシャル層上に、第1のゲート絶縁膜よりも薄い第2のゲート絶縁膜を介して形成された第2のゲート電極と、第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

半導体装置および携帯電話機

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】RXスルートランジスタ群TH(RX)は、互いに直列に接続されたMISFETQ1〜Q5において、それぞれのMISFETのボディ領域と、隣接するMISFETのソース領域あるいはドレイン領域とを、それぞれ、ダイオード(整流素子)を介して接続する。そして、特に、nチャネル型MISFETの場合、MISFETのボディ領域から隣接するMISFETのソース領域あるいはドレイン領域へ向う向きが順方向となるようにダイオードを接続する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル不純物の拡散を抑制し、高性能・高信頼性を実現しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板第1及び第2の領域に非晶質化のためのイオン注入を行い、第1の領域及び第2の領域に第1の不純物及び第2の不純物をそれぞれイオン注入し、注入した不純物を活性化して第1の不純物層及び第2の不純物層を形成し、不純物層を形成した半導体基板上に半導体層をエピタキシャル成長し、第1及び第2の領域上にゲート絶縁膜を成長し、第1及び第2のゲート絶縁膜上に第1及び第2のゲート電極をそれぞれ形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】低廉なプロセスにて高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の領域に形成された第1の不純物層及び第1のエピタキシャル半導体層と、第1のエピタキシャル半導体層上にゲート絶縁膜を介して形成された第1のゲート電極と、第1の領域に形成された第1のソース/ドレイン領域とを有する第1のトランジスタと、第2の領域に形成された第2の不純物層及び第1のエピタキシャル半導体層よりも薄い第2のエピタキシャル半導体層と、第2のエピタキシャル半導体層上にゲート絶縁膜を介して形成された第2のゲート電極と、第2の領域に形成された第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

半導体装置の製造方法

【課題】Geをチャネル材料に用いても、素子特性の劣化を抑制することを可能にする。

【解決手段】Geを含むp型半導体領域上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程と、前記半導体領域の、前記ゲート電極の両側に位置する第1および第2領域に、有機金属錯体および酸化剤を交互に供給して金属酸化物を堆積する工程と、前記金属酸化物の上に金属膜を堆積する工程と、熱処理を行うことにより、前記半導体領域および前記金属酸化物と、前記金属膜とを反応させて前記第1および第2領域に金属半導体化合物層を形成するとともに前記金属半導体化合物層と前記半導体領域との界面に金属偏析層を形成する工程と、を備えている。

(もっと読む)

マルチゲート電界効果トランジスタのゲート電極およびその製造方法

【課題】マルチゲート電界効果トランジスタにおいて、新規なゲート電極構造と製造方法を提供する。

【解決手段】マルチゲート電界効果トランジスタ102のゲート電極100は、半導体基板104と、前記半導体基板上の誘電体層106と、前記誘電体層上のフィン108と、前記フィンの側面上のゲート絶縁膜であって、前記フィンの側面上に形成されるゲート絶縁膜と接する誘電体層の上面部分を除き、前記誘電体層の上面上には形成されないゲート絶縁膜110と、フィン上のゲート電極層112と、前記フィンを覆うように形成されるポリシリコン層114とを具備する。

(もっと読む)

半導体装置および集積回路

【課題】ドレイン端での局所的な電流集中を防止して静電放電に対する耐性を向上させる。

【解決手段】N型高濃度埋め込み領域102の上面にN型低濃度領域103とN型ウエル領域104とN型高濃度埋め込みコンタクト領域105を順次隣接して配置し、N型低濃度領域103の上面にP型低濃度領域106を配置し、ドレイン電極113Dが接続される第1のN型高濃度領域107をN型高濃度埋め込みコンタクト領域105の上面に配置し、ソース電極113Sが接続される第2のN型高濃度領域108とP型高濃度領域109をP型低濃度領域106の上面にチャネル幅方向に並べて配置し、第1のN型高濃度領域107からN型ウエル領域104の上面を経由しP型低濃度領域106の上面に向けて素子分離領域110を配置し、P型低濃度領域106の上面に位置する箇所の上面にゲート酸化膜を介してゲート電極111を配置し、P型低濃度領域106のうちのゲート電極111の下部にチャネルが形成されるようにした。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

歪チャネルを有するMOSトランジスタを製造する方法

【課題】歪チャネルを有するMOS トランジスタを製造するための比較的簡単な方法を提供する。

【解決手段】歪チャネルを有するMOS トランジスタ(M) を製造する方法は、(a) 半導体基板(10)の表面に、ソース領域及びドレイン領域とMOS トランジスタを囲む絶縁領域(22)に部分的に延びる絶縁された犠牲ゲートとを備えたMOS トランジスタを形成するステップと、(b) 犠牲ゲートの上面と略同一の高さの上面を有する絶縁層を形成するステップと、(c) 犠牲ゲートを除去するステップと、(d) 露出した絶縁領域(22)の少なくとも上部分をエッチングしてトレンチを形成するステップと、(e) 半導体基板(10)を歪ませることが可能な材料(24)をトレンチに充填するステップと、(f) 犠牲ゲートの除去によって空いた空間にMOS トランジスタの絶縁ゲート(12)を形成するステップとを有する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】1つのチップ内に、高駆動性が求められるpMISFET及び高信頼性が求められるpMISFETの両方を形成してCMOSトランジスタの品質向上をはかる。

【解決手段】Siチャネルを有する第1のpMISFET領域121、Siチャネルを有する第2のpMISFET領域122、及びSiチャネルを有するnMISFET領域123を備えた半導体装置であって、第1のpMISFET領域121に、Siチャネルを挟んで該Siチャネルに第1の圧縮歪みを与える第1のSiGe層321が埋め込み形成され、第2のpMISFET領域122に、Siチャネルを挟んで該Siチャネルに第1の圧縮歪みとは大きさの異なる第2の圧縮歪みを与える第2のSiGe層322が埋め込み形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】CMISデバイスにおいて、pチャネル型電界効果トランジスタの動作特性を劣化させることなく、ひずみシリコン技術を用いたnチャネル型電界トランジスタの動作特性を向上させる。

【解決手段】所望する濃度プロファイルおよび抵抗を有するnMISのソース/ドレイン(n型拡張領域8およびn型拡散領域13)およびpMISのソース/ドレイン(p型拡張領域7およびp型拡散領域11)を形成した後、所望するひずみ量を有するSi:C層16をn型拡散領域13に形成することにより、nMISのソース/ドレインにおいて最適な寄生抵抗と最適なSi:C層16のひずみ量とを得る。また、Si:C層16を形成する際の熱処理を1m秒以下の短時間で行うことにより、すでに形成されているp型拡張領域7およびp型拡散領域11のp型不純物の濃度プロファイルの変化を抑える。

(もっと読む)

半導体装置の製造方法

【課題】 側壁部及び上部の平面部を持つ立体凹凸部分を形成した三次元デバイスとしての半導体装置において側壁部及び上部の平面部へ均一に高濃度の不純物を低エネルギードーピングできる方法を提供する。

【解決手段】 シリコン基板1の表面上に加工によりシリコンFin部11を形成した後、該シリコンFin部の側壁及び上部の平面部へドナーもしくはアクセプターとなる不純物原子を含む不純物薄膜を、堆積膜として上部の平面部には厚く、側壁には薄く堆積する工程と、前記シリコンFin部における前記堆積膜の斜め上方から斜め方向のイオン注入と反対側の斜め上方から斜め方向のイオン注入を行なうとともに、該イオン注入によって、前記不純物原子を堆積膜内部からシリコン基板の前記シリコンFin部の側壁内部及び上部の平面部内にリコイルして導入させる工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】基板に形成される第1の膜と第2の膜との重なり量を精度良く算出する。

【解決手段】半導体装置の製造方法は、基板の第1の領域及び第2の領域に第1の膜を形成する工程と、第2の領域の第1の膜の幅を測定する工程と、基板の第2の領域及び第3の領域に第2の膜を形成する工程と、第2の領域の第2の膜の幅及び第2の領域の第1の膜と第2の膜との距離を測定する工程と、第2の領域における第1の膜の幅の測定値、第2の膜の幅の測定値、第1の膜と第2の膜との距離の測定値及び第1の膜と第2の膜とに関する設計値に基づいて、第1の領域における第1の膜と第3の領域における第2の膜との重なり量を算出する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】容易なプロセスにより単結晶半導体層を形成したSOI構造のMISFETの提供

【解決手段】半導体基板1上に、第1の絶縁膜2を介して、一部に空孔4を有する第2の絶縁膜3が設けられ、空孔4上及び第2の絶縁膜3の一部上に島状に絶縁分離された半導体層6が設けられ、半導体層6上にゲート酸化膜12を介して、空孔4直上に空孔4の幅以下のゲート電極13が設けられ、半導体層6には、ゲート電極13に自己整合して低濃度のソースドレイン領域(9,10)が、ゲート電極13の側壁に設けられたサイドウォール14に自己整合して高濃度のソースドレイン領域(8,11)がそれぞれ設けられ、ゲート電極13(配線図示せず)及び高濃度のソースドレイン領域(8,11)にはバリアメタル17を有する導電プラグ18を介してバリアメタル20を有する配線21が接続されているMISFET。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル形成領域に印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させる半導体装置を提供する。

【解決手段】チャネル形成領域を有する半導体基板10上にゲート絶縁膜20が形成され、ゲート絶縁膜20の上層にゲート電極21が形成され、ゲート電極21の上層にチャネル形成領域に応力を印加する第1応力導入層22が形成されており、ゲート電極21及び第1応力導入層22の両側部における半導体基板10の表層部にソースドレイン領域13が形成されており、少なくとも第1応力導入層22の領域を除き、ソースドレイン領域13の上層に、チャネル形成領域に第1応力導入層22と異なる応力を印加する第2応力導入層26が形成されている構成とする。

(もっと読む)

半導体装置

【課題】SOI構造の単結晶半導体層(SiGe層/歪みSi層/SiGe層)上のMISFETの提供

【解決手段】半導体基板1に選択的に設けられた第1のトレンチの下部側面及び底面に絶縁膜3が設けられ、側面絶縁膜3間の底面絶縁膜3上に空孔4が設けられ、空孔4及び側面絶縁膜3上には単結晶半導体層が設けられ、半導体層は絶縁膜2が埋め込まれた第2のトレンチにより、島状に絶縁分離され、歪みSi層6直上にはゲート酸化膜11を介してゲート電極12が設けられ、半導体層には、ゲート電極12に自己整合してn型ソースドレイン領域(8、9)が、ゲート電極12の側壁のサイドウォール13に自己整合して、n+型ソースドレイン領域(7、10)がそれぞれ設けられ、ゲート電極12(配線図示せず)及びn+型ソースドレイン領域にはバリアメタル16を有する導電プラグ17を介してバリアメタル19を有する配線20が接続されているMISFET。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38上に第1ストッパ膜39及び第2ストッパ膜40を形成する工程と、第1領域2を覆う第1マスク60をマスクとし、第1ストッパ膜をストッパとして、第2領域4内の第2ストッパ膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の第2ストッパ膜をサイドエッチングする工程と、第2ストッパ膜とエッチング特性が異なる第2応力膜42を形成する工程と、第2領域を覆い、第1領域側の端面が第2ストッパ膜上に位置する第2マスクとし、第2ストッパ膜をストッパとして、第2応力膜の一部が第1応力膜の一部及び第2ストッパ膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

81 - 100 / 986

[ Back to top ]