Fターム[5F048BD01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | チャネル (4,415) | 形状 (1,258)

Fターム[5F048BD01]の下位に属するFターム

チャネル長(幅) (272)

Fターム[5F048BD01]に分類される特許

21 - 40 / 986

酸化物半導体層、半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであって、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極との接触抵抗を下げることができる。

(もっと読む)

半導体装置

【課題】RCATの電流駆動能力を向上させることが可能な半導体装置を提供する。

【解決手段】半導体基板11は、ゲート溝13を有している。拡散層12は、ゲート溝13の上部に対応する半導体基板11の表面領域に形成されている。ゲート絶縁膜14は、ゲート溝の壁面に形成されている。ゲート電極15は、ゲート溝13の内部及びゲート溝13の外部に形成されている。圧縮応力を有する膜16は、ゲート溝13の外部のゲート電極15の全面に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】一定のドレイン電圧及びゲート電圧に対して得られるドレイン電流を増大することの出来る半導体装置の製造方法を提供する。

【解決手段】チャンネル領域と、ソース領域及びドレイン領域と、前記ソース領域及びドレイン領域にそれぞれ電気的に接続する合計二つの第1の電極と、前記チャンネル領域上にゲート絶縁膜を介して設けられた第2の電極とを備えた半導体装置の製造に際し、前記ゲート絶縁膜を、酸素の含有量を1ppb以下にした水素添加超純水にIPAを添加した洗浄液を用いて、酸素含有量1ppb以下の窒素雰囲気でしかも遮光した状態で表面の洗浄を行ない、かつ等方性酸化または窒化で形成することにより、前記チャンネル領域と前記ゲート絶縁膜との界面の平坦度を、前記ソース領域から前記ドレイン領域に向かう方向での長さ2nmにおけるピーク・トゥ・バレイ値が0.3nm以下となるようにするとともに、前記第1の電極から前記チャンネル領域までの抵抗率を4Ω・μm以下とした。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの集積度が高い半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、を備える。そして、前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なる。

(もっと読む)

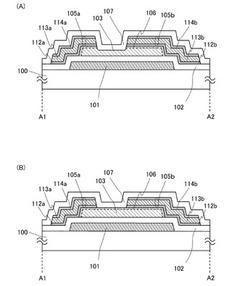

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用ボトムコンタクト型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。多階調マスクを用いたフォトリソグラフィ工程を用いることで、作製工程を簡略化できる。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置

【課題】小面積、低電力動作、高速動作を並立する論理ゲートを含む半導体装置の構成を提供する。

【解決手段】本発明に係る半導体装置は、基板上にゲート絶縁膜を介してゲート電極と半導体層が配置され、半導体層に接続してソース電極とドレイン電極とが配置される薄膜トランジスタを2つ以上含む論理ゲートで構成される。少なくとも第一の薄膜トランジスタは、そのゲート電極が電気的に浮遊状態にあり、かつ、その半導体層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。また、少なくとも第二の薄膜トランジスタは、そのゲート電極が入力端子に接続され、かつ、そのチャネル層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。

(もっと読む)

集積回路装置及びその製造方法

【課題】FinFETの特性が均一な集積回路装置及びその製造方法を提供する。

【解決手段】実施形態に係る集積回路装置は、半導体基板の上面に形成され、第1方向に延びる複数本のフィンと、前記フィン間に配置された素子分離絶縁膜と、前記第1方向に対して交差した第2方向に延び、前記素子分離絶縁膜上に設けられたゲート電極と、前記フィンを前記ゲート電極から絶縁する絶縁膜と、を備える。そして、連続して配列された複数本の前記フィンが配置された第1領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも下方の第1の位置に位置し、前記第1領域から見て前記第2方向に位置する第2領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも上方の第2の位置に位置する。また、前記第2領域においては、前記素子分離絶縁膜が前記フィンの側面の全体を覆っている。

(もっと読む)

半導体装置

【課題】トンネル型FETのオン電流とオフ電流との比と、単位基板面積あたりのオン電流を増大させる。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に絶縁膜を介して形成されたゲート電極と、前記ゲート電極の側面に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記半導体基板上に順に積層された第1導電型の下部主端子層と、中間層と、第2導電型の上部主端子層とを有し、前記ゲート絶縁膜を介して前記ゲート電極の側面に形成された積層体とを備える。さらに、前記上部主端子層は、前記ゲート電極の側面に、前記ゲート絶縁膜と半導体層を介して形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1のnMIS形成領域1Aにnチャネル型MISFETQnを、半導体基板1のpMIS形成領域1Bにpチャネル型MISFETQpを、それぞれ形成してから、nチャネル型MISFETQnおよびpチャネル型MISFETQpを覆うように引張応力の窒化シリコン膜5を形成し、nMIS形成領域1AおよびpMIS形成領域1Bの窒化シリコン膜5に紫外線照射処理を施す。その後、nMIS形成領域1Aの窒化シリコン膜5を覆いかつpMIS形成領域1Bの窒化シリコン膜5を露出するマスク層6aを形成してから、pMIS形成領域1Bの窒化シリコン膜5をプラズマ処理することで、pMIS形成領域1Bの窒化シリコン膜5の引張応力を緩和させる。

(もっと読む)

低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法

【課題】低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法を提供する。

【解決手段】NMOS素子及びPMOS素子が何れもアナログ及びデジタルモードのような相異なるモードで動作される半導体素子において、これら素子の要求される動作モードによって特定素子にストレスエンジニアリングを選択的に適用する。フォトレジスト160をデジタル回路領域のPMOSトランジスタのみを覆うように形成し、Ge、Siなどのイオン162をストレスコントロール膜150に注入する。デジタル回路領域のPMOSトランジスタを除くあらゆる領域でストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換され、デジタル回路領域のPMOSトランジスタのチャネル104bだけに圧縮応力が印加される状態が残る。

(もっと読む)

半導体装置

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

【解決手段】SRAMを構成するドライバトランジスタ(Dr1)が配置される活性領域(Ac)の下部に、絶縁層(BOX)を介して、素子分離領域(STI)により囲まれたn型のバックゲート領域(nBG)を設け、ドライバトランジスタ(Dr1)のゲート電極(G)と接続する。また、n型のバックゲート領域(nBG)の下部に配置され、少なくともその一部が、素子分離領域(STI)より深い位置に延在するp型ウエル領域(Pwell)を設け、接地電位(VSS)に固定する。かかる構成によれば、トランジスタの閾値電位(Vth)をトランジスタがオン状態の時には高く、逆に、オフ状態の時には低くなるように制御し、また、p型ウエル領域(Pwell)とn型のバックゲート領域(nBG)との間のPN接合も順バイアスさせないよう制御することができる。

(もっと読む)

半導体装置の製造方法

【課題】寄生抵抗が低く、接合リーク電流が抑制されたトランジスタを容易に形成することができる半導体装置の製造方法を提供する。

【解決手段】実施形態にかかる半導体装置の製造方法は、シリコン基板中のチャネル領域上にゲート絶縁膜を介してゲート電極を形成し、シリコン基板に所望の不純物を注入することにより、チャネル方向に沿ってチャネル領域を挟むようにシリコン基板中にソース領域とドレイン領域とを形成し、ソース領域及びドレイン領域の表面をアモルファス化することにより、それぞれの表面に不純物を含むアモルファス領域を形成し、アモルファス領域の上にニッケル膜を形成し、マイクロ波を照射して、アモルファス領域とニッケル膜とを反応させてニッケルシリサイド膜を形成しつつ、アモルファス領域を固相成長させてアモルファス領域に含まれる不純物を活性化し、未反応のニッケル膜を除去する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク半導体上に形成されている場合においても、電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】フィン型半導体層1の両側面には、チャネル領域7のポテンシャルを制御するゲート電極4が配置され、チャネル領域7には、フィン型半導体層1のソース層2側から根元BM側にかけてポテンシャルバリアPB1、PB2が形成されている。

(もっと読む)

半導体装置

【課題】トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】半導体突出部2は、半導体基板1上に形成されている。ソース/ドレイン層5、6は、半導体突出部2の上下方向に設けられている。ゲート電極7、8は、半導体突出部2の側面にゲート絶縁膜4を介して設けられている。チャネル領域3は、半導体突出部2の側面に設けられ、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。

(もっと読む)

半導体装置

【課題】高い開口率を有し、安定した電気特性を有する薄膜トランジスタを有する、信頼

性のよい表示装置を作製し、提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動

回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物

半導体によって構成された駆動回路用薄膜トランジスタと、金属によって構成された駆動

回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体に

よって構成され且つ半導体層が酸化物半導体によって構成された画素用薄膜トランジスタ

と、酸化物導電体によって構成された表示部用配線とを有する。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインが、第1半導体結晶層を構成する原子とニッケル原子との化合物、第1半導体結晶層を構成する原子とコバルト原子との化合物または第1半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなり、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、第2半導体結晶層を構成する原子とニッケル原子との化合物、第2半導体結晶層を構成する原子とコバルト原子との化合物、または、第2半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなる半導体デバイスを提供する。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板1aの活性領域1cが素子分離絶縁膜2で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極8a、ソース・ドレイン領域及び被覆応力膜を有するNTrを有し、ソース・ドレイン領域の両側部に位置する素子分離絶縁膜2aの表面は、ソース・ドレイン領域の表面より低い位置に形成されており、ゲート電極8a、活性領域1c、及び表面がソース・ドレイン領域の表面より低い位置に形成された素子分離絶縁膜2aを被覆して、チャネル形成領域に対し引張応力を印加する被覆応力膜が形成されている構成とする。

(もっと読む)

半導体装置

【課題】1個の柱を用いてインバータを構成することにより、高集積なCMOSインバータ回路からなる半導体装置を提供する。

【解決手段】第1のシリコンと、該第1のシリコンとは極性が異なる第2のシリコンと、前記第1のシリコンと前記第2のシリコンとの間に配置され、基板に対して垂直方向に延びている第1の絶縁物とからなる1本の柱と、前記第1のシリコンの上下のそれぞれに配置され、前記第1のシリコンとは極性が異なる第1の高濃度不純物を含むシリコン層と、前記第2のシリコンの上下のそれぞれに配置され、前記第2のシリコンとは極性が異なる第2の高濃度不純物を含むシリコン層と、前記第1のシリコンと前記第2のシリコンと前記第1の絶縁物とを取り囲む第2の絶縁物と、前記第2の絶縁物を取り囲む導電体とを含む半導体装置により、上記課題を解決する。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板(1a,1b)の活性領域(1c,1d)が素子分離絶縁膜(2,6a)で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極(8a,8b)、ソース・ドレイン領域及び被覆応力膜を有するNTrとPTrを有し、活性領域におけるゲート長方向が<100>方向であり、素子分離絶縁膜としてNTrにおけるソース・ドレイン領域の両端部に第1の引張応力膜6aが形成され、ソース・ドレイン領域の両端部以外に第1の圧縮応力膜2が形成され、PTrの素子分離絶縁膜は第1の圧縮応力膜2が形成され、被覆応力膜としてNTrに第2の引張応力膜が形成され、PTrに第2の圧縮応力膜が形成されている構成とする。

(もっと読む)

21 - 40 / 986

[ Back to top ]