Fターム[5F048BF17]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 配線・電極・コンタクト (11,486) | S・Dとのコンタクト抵抗低減領域 (373)

Fターム[5F048BF17]に分類される特許

81 - 100 / 373

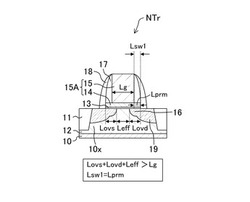

半導体装置及びその製造方法

【課題】短チャネル効果を抑制すると共に、MISトランジスタの駆動能力が劣化することを防止するMIS(Metal Inserted Semiconductor)トランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10における活性領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第1の導電膜14、及び該第1の導電膜14上に形成された第2の導電膜15からなるゲート電極15Aと、活性領域10xにおける第2導電膜15の側方下に形成されたエクステンション領域16と、第1の導電膜14上に、第2の導電膜15の側面と接して形成された第1のサイドウォール17とを備え、第1の導電膜14のゲート長方向の長さは、第2の導電膜15のゲート長方向の長さよりも大きい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 半導体層上に形成される絶縁膜の厚さを増大させることなく、絶縁膜の絶縁破壊に対する耐圧の向上を図る半導体装置およびその製造方法を提供すること。

【解決手段】 エピタキシャル層5の表面にLOCOS酸化膜8を形成する。また、エピタキシャル層5には、LOCOS酸化膜8の厚さよりも大きな厚さを有する第1絶縁体13を埋設する。そして、第1絶縁体13上に抵抗素子3を形成する。これにより、抵抗素子3とエピタキシャル層5との間に、第1絶縁体13を介在させる。エピタキシャル層5と抵抗素子3との間に印加される電圧が第1絶縁体13に分散されるので、抵抗素子3への電圧の印加に伴うLOCOS酸化膜8の印加電圧を低減することができる。

(もっと読む)

半導体装置の製造方法、半導体装置、電気光学装置、および電子機器

【課題】三次元半導体装置における特性を向上させることができる製造方法および装置構成を提供する。

【解決手段】第1半導体膜(9)上にカーボンナノチューブを備えるプラグ電極(15)を形成する工程、形成されたプラグ電極(15)の周囲に層間絶縁膜(16,18)を形成する工程、層間絶縁膜の表面を平滑化してプラグ電極(15)の頂部を露出させる工程、層間絶縁膜およびプラグ電極の頂部上に非晶質の第2半導体膜を形成する工程、非晶質の第2半導体膜にエネルギーを供給して露出したプラグ電極(15)を触媒として機能させて非晶質の第2半導体膜を結晶化させ結晶化した第2半導体膜(23)とする工程を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ブレークダウン電圧の向上とオン抵抗の低減を同時に可能とする半導体装置を提供する。

【解決手段】半導体装置は、第1領域12、ソース領域20、第2領域14、ドレイン領域30、ゲート絶縁層60、フィールド絶縁層50、ゲート電極40を具備する。第1領域12は表面領域に設けられる。ソース領域20は第1領域12の表面領域に設けられる。第2領域14は表面領域に設けられる。ドレイン領域30は第2領域14の表面領域に設けられる。ゲート絶縁層60はソース領域20と第2領域14との間の表面上に設けられる。フィールド絶縁層50はドレイン領域30とゲート絶縁層60との間の表面領域に設けられる。ゲート電極40はゲート絶縁層60とフィールド絶縁層50の一部を覆う。フィールド絶縁層50はゲート電極40と重なる部分で、ゲート絶縁層60側が薄くなるような段差51を有する。

(もっと読む)

CMISトランジスタの製造方法

【課題】本発明は、PMISトランジスタ側とNMISトランジスタ側とでシリサイド層の組成のバラツキを防止でき、またトランジスタのゲート形状の不安定化を防止できる、CMISトランジスタの製造方法を提供する。

【解決手段】ゲート絶縁膜103とN−metal104と多結晶シリコン106とが当該順に積層した第一のゲート構造G1を形成する。ゲート絶縁膜103と多結晶シリコン106とが当該順に積層した第二のゲート構造G2を形成する。第一、二のゲート構造G1,G2をマスクした状態で、各ゲート構造G1,G2の両脇における半導体基板101上を、シリサイド化させる。そして、第一、二のゲート構造G1,G2を構成する多結晶シリコン106を、シリサイド化させる。

(もっと読む)

半導体装置

【課題】トリプル・ウェル構造を有する半導体装置において、製造歩留まり及び製品信頼性を向上させることのできる技術を提供する。

【解決手段】p型の基板Sub内に形成された深いn型ウェルDNW0、浅いp型ウェルPW及び浅いn型ウェルNWが形成された領域と異なる領域に浅いp型ウェルPW100を形成し、この浅いp型ウェルPW100内に形成されたp型拡散タップPD100と、深いn型ウェルDNW0内の浅いn型ウェルNW0内に形成されたp型拡散タップPD0とを第2層目の配線を用いて結線し、深いn型ウェルDNW0内に形成されたnMIS200nのゲート電極及びpMIS200pのゲート電極と、基板Sub内に形成されたnMIS100nのドレイン電極及びpMIS100pのドレイン電極とを第2層目以上の配線を用いて結線する。

(もっと読む)

半導体装置の製造方法

【課題】スループットを向上できる半導体装置の製造方法を提供する。

【解決手段】第1絶縁膜15に覆われた第1半導体パターン13eを第1活性領域7の上方に形成し、第2半導体パターン13aを第2活性領域3の上方に形成し、第1絶縁膜15と第1、第2半導体パターン13a、13eの上方に第2絶縁膜25を形成し、第2絶縁膜25及び第1絶縁膜15をエッチングして第1半導体パターン13eに達する深さの開口を形成し、第2絶縁膜25をパターニングして第2半導体パターン13aの側面にサイドウォールを形成し、第1、第2半導体パターン13a、13eのそれぞれの上に金属膜を形成し、第1、第2半導体パターン13a、13eと金属膜31を反応させることによりシリサイド層31a、31eを形成する工程を含む。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、寄生容量を充放電する変位電流が発生することを抑制し、回路の誤動作を防止する手段を提供する。

【解決手段】低電位基準回路部LVと対応するように第1リードフレーム3aを配置すると共に、高電位基準回路部HVと対応するように第2リードフレーム3bを配置することにより、絶縁基板2のうち低電位基準回路部LVの下方に位置する部分に関しては、低電位基準回路部LVと第1リードフレーム3aとにより同電位に挟まれた状態となるようにし、絶縁基板2のうち高電位基準回路部HVの下方に位置する部分は、高電位基準回路部HVと第2リードフレーム3bとにより同電位に挟まれた状態となるようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】アンチヒューズ素子のゲート電極と半導体基板間で形成される導電パスの接触抵抗値を安定させる。また、導通状態におけるアンチヒューズ素子の抵抗値のばらつきを抑制し、抵抗値を低く保って、アンチヒューズ素子の導通状態の誤判定の発生を抑制する。

【解決手段】半導体基板と、第1ゲート絶縁膜と第1ゲート電極と、第1ゲート電極の下の半導体基板内に設けられた高濃度不純物領域と、半導体基板内の高濃度不純物領域を挟んだ両側に設けられ高濃度不純物領域と同じ導電型の不純物を含有する第1ソース・ドレイン領域と、を有するアンチヒューズ素子を備えたことを特徴とする半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】接触抵抗の増加が抑制されたピラー形状の縦型MOSトランジスタを用いた半導体装置を提供する

【解決手段】基部1aと複数のピラー部1Aとを有するシリコン基板1と、基部1aに設けられた一方のソースドレイン領域6と、ピラー部1Aの側面1bを覆うゲート絶縁膜4と、ゲート絶縁膜4を介してピラー部1Aの側面1bを覆うゲート電極5と、ピラー部1Aの上部に設けられた他方のソースドレイン領域12と、他方のソースドレイン領域12と接続されるコンタクトプラグ9とを備え、ピラー部1Aの上面1cの全面にコンタクトプラグ9が接続されていることを特徴とする半導体装置10。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】微細で精度が高く、歩留まりが向上した半導体装置を提供する。

【解決手段】半導体装置は、第1トランジスタ2と第2トランジスタ5とを具備する。第1トランジスタ2は、半導体基板100上に第1ゲート絶縁膜51を介して形成された第1ゲート電極21と第1ソース・ドレイン領域31と第1共通ソース・ドレイン領域30とを備える。第2トランジスタ5は、半導体基板100上に第2ゲート絶縁膜51を介して形成された第2ゲート電極22と第2ソース・ドレイン領域31と第1共通ソース・ドレイン領域30とを備える。第1ゲート電極21及び第2ゲート電極22は、第1共通ソース・ドレイン領域30のコンタクトである第1ノード電極41の両側壁に設けられている。

(もっと読む)

静電保護回路、静電保護素子および半導体装置

【課題】サージ電圧によって自身が破壊されるのを防止した静電保護回路を提供する。

【解決手段】pMOSトランジスタ20のゲート電極25が、接合ゲート型電界効果トランジスタ30のソース電極、ソース電位取出領域34、チャネル領域32、ドレイン電位取出領域35およびドレイン電極を介して参照電位線路L4に電気的に接続されている。pMOSトランジスタ20のソース電極とボディ電極とがそれぞれ信号線路L1に電気的に接続されている。これにより、信号線路L1にサージ電圧が印加され、サージ電圧がボディ領域21とソース領域22とに伝わり、ボディ領域21とソース領域22とがサージ電圧となった場合には、ボディ領域21のうちゲート電極25直下の部分にp型チャネル(図示せず)が形成され、ソース領域22のサージ電圧がp型チャネルを介してドレイン領域23に伝わり、参照電位線路L4へ放電される。

(もっと読む)

半導体装置及びその製造方法

【課題】プラズマプロセスによるゲート絶縁膜へのプラズマチャージを緩和させることができる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、基板上にゲート絶縁膜4及びゲート電極5を順に形成し、第1の層間絶縁膜8を形成後、コンタクトホール11a、11b及び11cと溝11を形成し、そこにWプラグ9a、9b、9c及び9を埋め込み、Al配線10a、10b及び10cを形成し、ゲート電極及び保護ダイオードを囲むAlシールド用配線10を形成し、第2の層間絶縁膜12を形成し、viaホール15及び15aを形成し、Wプラグ13及び13aを埋め込み、Al配線14を形成する工程を具備し、Wプラグ13とWプラグ13aは第3の配線14によって電気的に接続されていることを特徴とする。

(もっと読む)

半導体装置、その製造方法及び半導体基板

【課題】半導体層を剥離後の半導体基板を再利用しつつ、特性が均一なチャネル領域とソース/ドレイン領域とを提供することを課題とする。

【解決手段】予め半導体基板にチャネル領域とソース/ドレイン領域の複数層の厚さに対応するイオン注入領域を形成し、この基板を水素注入よる転写法に使用することで、上記課題を解決する。

(もっと読む)

スピンMOSFETを有する論理回路

【課題】長期間の動作が安定する、スピンMOSFETを有する論理回路を提供することを可能にする。

【解決手段】n型もしくはp型のスピンMOSFET4と、n(n≧2)個の入力端子と、スピンMOSFETのゲートとn個の入力端子との間にそれぞれ設けられたn個のコンデンサ6,8とを有する入力回路と、駆動電源とスピンMOSFETのゲートとの間に設けられた第1の抵抗Rp1と、駆動電源とスピンMOSFETのゲートとの間に第1の抵抗と直列に接続され、ゲートにリセット信号を反転した信号を受けるp型MOSFET101と、接地電源とスピンMOSFETのゲートとの間に設けられた第2の抵抗Rn1と、接地電源とスピンMOSFETのゲートとの間に第2の抵抗と直列に接続され、ゲートにリセット信号を受けるn型MOSFET121と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタの性能の低下を抑制できる半導体装置を提供する。

【解決手段】第一のトランジスタ11、第二のトランジスタ12、ゲート構造13を被覆する応力付与層16を設ける工程の前段で、第二のトランジスタ12上に他のシリコン酸化膜14を形成し第二のトランジスタ12上に所定の厚みのシリコン酸化膜18を形成する。第二のトランジスタ12及びゲート構造13上の応力付与層16を除去し第一のトランジスタ11上に応力付与層16を残す工程にて、第二のトランジスタ12上のシリコン酸化膜が第一のトランジスタ11上のシリコン酸化膜よりも過剰に薄くなってしまうことが防止される。第一のトランジスタ11及び第二のトランジスタ12上のシリコン酸化膜15,18等を除去する際に第二のトランジスタ12上のシリコン酸化膜が薄いため第二のトランジスタ12のソース領域、ドレイン領域が削れてしまうことを防止できる。

(もっと読む)

熱処理装置及び当該熱処理装置を用いたSOI基板の作製方法

【課題】熱処理において、基板の反りを抑制し、基板の局部的な温度変化によって生じる品質不良を抑制することを目的の一とする。

【解決手段】処理室と、処理室内に設けられた支持台と、支持台上に設けられ、被処理基板を支持する複数の支持体と、被処理基板を加熱する加熱手段とを設け、支持台に支持体を脱着可能な固定部を複数設け、複数の支持体を複数の固定部に選択的に取り付けることにより、複数の支持体の位置を可変可能とする。

(もっと読む)

半導体装置の製造方法

【課題】縦型MOSトランジスタの高集積化、高性能化。

【解決手段】基板上の絶縁膜上に平面状半導体層及び複数の平面状半導体層上の柱状半導体層を形成し、平面状半導体層を素子に分離し、平面状半導体層に不純物領域を形成し、その後に表面の少なくとも一部に絶縁膜を形成し、絶縁膜上に導電膜を形成し、絶縁膜及び前記導電膜をエッチバックし、柱状半導体層側面の絶縁膜及び導電膜を所望の長さに形成し、ゲート電極を形成し、導電膜及び絶縁膜を選択的にエッチングにより除去し、ゲート電極及び前記ゲート電極から延在するゲート配線を形成し、複数の柱状半導体層の各々に対応する複数のMOSトランジスタのうち、第1のMOSトランジスタの平面状半導体層に形成された不純物領域の表面の少なくとも一部と第2のMOSトランジスタの平面状半導体層に形成された不純物領域の表面の少なくとも一部とを接続する第1のシリサイド層を形成する。

(もっと読む)

半導体装置

【課題】電荷移動度を向上させる歪みをチャネル領域に発生させる結晶層をチャネル領域下に有し、かつリーク電流経路が形成されることを抑制できる半導体装置を提供する。

【解決手段】一態様に係る半導体装置は、半導体基板1と、前記半導体基板上に形成された第1の半導体結晶層14と、前記第1の半導体結晶層上にゲート絶縁膜11を介して形成されたゲート電極13と、前記第1の半導体結晶層内の前記ゲート絶縁膜下の領域に形成されたチャネル領域15と、前記第1の半導体結晶層内の前記チャネル領域を挟んだ領域に形成されたソース・ドレイン領域16と、前記半導体基板と前記チャネル領域との間に形成され、前記第1の半導体結晶層を構成する結晶よりも格子定数の大きい結晶からなり、前記半導体基板と前記第1の半導体層の間に、前記第2の半導体結晶層17を挟んで形成された埋込絶縁体層18と、を有する。

(もっと読む)

半導体装置とその製造方法

【課題】

ロジックプロセスとの整合性の高い、メモリセルを含む半導体装置及びその製造方法を提供する。

【解決手段】

半導体装置は、半導体基板の主面側に画定され、各々が、長尺状の平面視形状を有し、トランジスタ部とキャパシタ部を含む、複数の活性領域と、活性領域を取り囲んで半導体基板に形成された溝部と、該溝部を埋め込んだ絶縁材とを含むSTIと、各活性領域のキャパシタ部の幅方向両側のSTIの絶縁材を底部を残して掘り下げ、活性領域側壁を露出するキャパシタ用凹部と、各活性領域のトランジスタ部上面上に形成され、第1絶縁膜とその上の第1導電層とを含む絶縁ゲート電極構造と、各活性領域のキャパシタ部の上面上と露出された側面上に形成され、第1絶縁膜と同一材料で形成された第2絶縁膜と、第2絶縁膜を覆い、複数の活性領域に亘って、第1導電層と同一材料で形成された第2導電層とを含むMISキャパシタ構造と、を有する。

(もっと読む)

81 - 100 / 373

[ Back to top ]