Fターム[5F048BF17]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 配線・電極・コンタクト (11,486) | S・Dとのコンタクト抵抗低減領域 (373)

Fターム[5F048BF17]に分類される特許

61 - 80 / 373

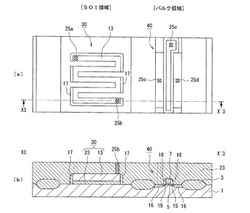

半導体装置の製造方法及び半導体装置

【課題】抵抗特性のばらつきが少ない抵抗素子を低コストで形成することを可能とした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】SOI領域のSi基板1上にSiGe層を形成する工程と、SiGe層上にSi層13を形成する工程と、Si層13及びSiGe層を平面視で抵抗素子の形状に形成する工程と、Si層13及びSiGe層の各側面にサイドウォール17を形成する工程と、SiGe層を露出する溝部19を形成する工程と、サイドウォール17によりSi層13の側面が支えられた状態で、溝部19を介してSiGe層をエッチングすることにより、Si層13とSi基板1との間に空洞部21を形成する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】1個の島状半導体を用いてインバータを構成することにより、高集積なSGTを用いたCMOSインバータ回路からなる半導体装置を提供する。

【解決手段】島状半導体層の周囲を取り囲む第1のゲート絶縁膜と、第1のゲート絶縁膜の周囲を取り囲むゲート電極と、ゲート電極の周囲を取り囲む第2のゲート絶縁膜と、第2のゲート絶縁膜の周囲を取り囲む筒状半導体層と、島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、島状半導体層の下部に配置された第2の第1導電型高濃度半導体層と、筒状半導体層の上部に配置された第1の第2導電型高濃度半導体層と、筒状半導体層の下部に配置された第2の第2導電型高濃度半導体層と、を有することを特徴とする半導体装置により、上記課題を解決する。

(もっと読む)

半導体装置

【課題】トランジスタに接続される配線がトランジスタのチャネル幅方向と垂直の方向から導入される場合においても、ESDに対する保護動作時にトランジスタ全体で均一に動作することのできるESD保護用のN型MOSトランジスタを有する半導体装置を提供する。

【解決手段】ドレイン領域とソース領域がひとつずつゲート電極を挟んで交互に配置された、複数のトランジスタが一体化した構造を有するESD保護用のN型MOSトランジスタにおいて、ドレイン領域に接続される第1のメタル配線とソース領域に接続される第1のメタル配線の片方あるいは両方が、第2のメタル配線と接続されており、第1のメタル配線と第2のメタル配線とを電気的に接続するための一定の大きさを有するビアホールの配置数を、ESD保護用のN型MOSトランジスタへ外部から配線される配線の距離に応じて、1から3までの個数比となるように形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置内の局所配線を簡単な工程で形成するための半導体装置の製造方法を提供する。

【解決手段】シリコン基板101上に1又は複数の半導体素子が作り込まれてなる半導体装置に局所配線構造を形成する際に、半導体素子の2つの導電領域を絶縁している絶縁領域に、この2つの導電領域を接続するようにシリコン膜104又は第1金属膜109を形成し(第1工程)、形成されたシリコン膜又は第1金属膜上に無電解めっき法により選択的に第2金属膜110を形成する(第2工程)。

(もっと読む)

半導体集積回路

【課題】トランジスタの特性ばらつきによる遅延回路の遅延時間の変動を抑制することが可能で、更に、製造工程における加工ばらつきに強く、レイアウト拡張性に優れた半導体集積回路を小面積に提供する。

【解決手段】第1の電源VDDと第2の電源(接地電源)との間に直列に接続されたP型MOSトランジスタMP11と2以上のN型MOSトランジスタMN11、MN12とが備えられる。入力端子INは前記P型MOSトランジスタMP11のゲート端子と前記N型MOSトランジスタMN11、MN12のゲート端子とに接続される。更に、P型MOSトランジスタMP11とN型MOSトランジスタMN11の接点である出力端子OUTに接続した1以上の容量素子C1を有し、P型MOSトランジスタMP11の駆動能力を、2以上に直列接続したN型MOSトランジスタMN11、MN12の総駆動能力よりも大きく構成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】相補型LDMOSトランジスタとCMOSトランジスタとを混載した半導体装置を、トランジスタ毎の特性のばらつきを抑制して製造する。

【解決手段】同一半導体基板にCMOSトランジスタと相補型LDMOSトランジスタを混載した半導体装置の製造方法であって、LDMOSトランジスタのp型及びn型ボディ層を形成する際、ゲート電極形成に用いたフォトレジストをそのままマスクとして用いる。

(もっと読む)

集積回路内のESD保護に要する面積を縮小する方法および装置

入力/出力(「I/O」)回路(100)は、シリサイドブロック(102)を用いて入力ピン(110)に結合された第1のNチャネル金属酸化物半導体(「NMOS」)電界効果トランジスタ(「FET」)(104)を有する。第1のPチャネル金属酸化物半導体(「PMOS」)FET(106)はこの入力ピンに直接結合され、そのNウェルはESDウェルバイアス回路(124)に電気的に結合される。NMOS低電圧差動信号(「LVDS」)ドライバ(222)も入力ピンに直接接続され、このドライバはカスケード接続されたNMOS FET(224,226)を有する。LVDSドライバの第1のNMOS FET(224)は、接地に電気的に結合された第1のPタップガードリング(308)およびESDウェルバイアスに結合されたNウェルガードリング(312)の中に作られる。LVDSドライバの第2のNMOS FET(226)は接地に電気的に接続された第2のPタップガードリング(324)の中に作られる。  (もっと読む)

(もっと読む)

半導体装置

【課題】ゲート・ドレイン間容量、ゲート・ソース間容量を低減し、微細プロセスに混載しやすい電界効果トランジスタの半導体装置を提供する。

【解決手段】基板10に設けられたPウエル11と、Pウエル11に設けられたN+ソース13と、N+ドレイン12と、Pウエル11とN+ドレイン12の間に設けられた低濃度N型領域40と、領域40に設けられた絶縁層17と、N+ソース領域13と領域40との間に挟まれたPウエル11上にゲート絶縁層を介して設けられた制御電極と、制御電極と離隔して、絶縁層17上に設けられた補助電極18と、N+ソース13と接続された第1の主電極31と、N+ドレイン12と接続された第2の主電極32と、を備え、主電極31,32間で流れる主電流の方向を第1の方向と規定し、第1の方向と垂直な方向を第2の方向と規定した場合、絶縁層17の第2の方向に沿った幅が、主電極32に向かって細くなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】 オン抵抗の小さいDMOSトランジスタを含む半導体装置の製造方法を提供することを目的とする。

【解決手段】

CMOSトランジスタ1は、ゲート電極9と、N+型のソース領域3と、N+型のドレイン領域4を備える。DMOSトランジスタ21は、ゲート電極29と、N+型のソース領域23と、N―型のドリフト領域30と、ドレイン領域24と、シリサイド層32aを備える。ゲート電極9のソース領域3側とドレイン領域4側の側部にはサイドウォール8Bが設けられ、ゲート電極29のソース領域23側とドレイン領域24側の側部にはサイドウォール28C、28Dが設けられている。ドレイン領域24側のサイドウォール28Cは、ソース領域23側のサイドウォール28D、及びサイドウォール2Bよりもチャネル方向に沿う厚さが厚い。さらに、シリサイド層32aがゲート電極9上面のドレイン領域24側端まで形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板上に設けられるNiPtSi電極の熱安定性を向上させる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体基板と、この半導体基板中のチャネル領域と、チャネル領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、チャネル領域の両側に形成され、NiおよびPtを主成分とする金属半導体化合物層からなるソース/ドレイン電極とを備え、金属半導体化合物層と半導体基板との界面において、金属半導体化合物層の単一の結晶粒と半導体基板との境界部の最大Pt濃度が、界面の平均Pt濃度よりも高いことを特徴とする半導体装置および半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】隣接する活性領域間が狭くなった場合においても、コンタクトプラグと拡散層とのコンタクト抵抗を低く抑えることが可能な半導体装置及びその製造方法を提供する。

【解決手段】X方向に延在する活性領域102内に設けられたゲートトレンチ103gt1、103gt2及びダミーゲートトレンチ103dgtと、活性領域102を横切るY方向に延在し、各トレンチ103gt1、103gt2、103dgt内にそれぞれ少なくとも一部が埋め込まれたゲート電極104g1、104g2及びダミーゲート電極104dgとを有し、ゲート電極104g1とその両側に設けられた拡散層105a1,105a2とからなるトランジスタ109と、ゲート電極104g2とその両側に設けられた拡散層105b1,105b2とからなるトランジスタ110は、拡散層105a2と拡散層105b1との間に配置されたダミーゲート電極104dgにより絶縁分離される。

(もっと読む)

半導体装置

【課題】PIDの影響を遮断することのできるレイアウト手法を用いてアンテナダイオードを配置することにより、PIDに起因する電界効果トランジスタの特性劣化を防止して、信頼度の高い半導体装置を実現する。

【解決手段】第1アンテナダイオードAD1とnMISのゲート電極16とを第1層目の配線M1を介して電気的に接続し、第2アンテナダイオードAD2と他の半導体素子とを第1層目の配線M1から第4層目の配線(アナログブロック内の最上層配線から1層下の配線)M4を介して電気的に接続する。さらに第1アンテナダイオードAD1と電気的に繋がる第4層目の配線M4と第2アンテナダイオードAD2と電気的に繋がる第4層目の配線M4とをアナログブロック内の最上層配線である第5層目の配線25によって結線する。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御でき、短チャネル効果を効果的に抑制できる半導体装置を提供する。

【解決手段】シリコン基板1と接してショットキー接合を形成するソース領域10,ドレイン領域11と、上記シリコン基板1とソース領域10との境界が露出する部分およびシリコン基板1とドレイン領域11との境界が露出する部分を被覆するように設けられた絶縁層を備える。上記絶縁層は、シリコン基板1とソース領域10との境界およびシリコン基板1とドレイン領域11との境界を跨ぐように、シリコン基板1とソース領域10に接すると共にシリコン基板1とドレイン領域11に接する固定電荷を含む領域8を有する。上記固定電荷は、熱平衡状態において荷電している。

(もっと読む)

半導体装置の製造方法

【課題】周辺トランジスタやメモリセルを構成するnMISトランジスタの駆動特性の劣化を抑制することができる半導体装置の製造方法を提供する。

【解決手段】n型の電界効果型トランジスタを含む半導体装置の製造方法において、半導体基板に対してp型不純物となる元素を有するp型不純物元素含有ガスを含むエッチングガスを用いて、半導体基板に素子分離溝を形成するとともに、素子分離溝の内面に、p型不純物を含む不純物層を形成する素子分離溝形成工程と、素子分離溝内に塗布型絶縁膜を埋め込んで素子分離絶縁膜を形成する素子分離絶縁膜形成工程と、を含む。

(もっと読む)

半導体装置

【課題】抵抗素子及び容量素子の三次元化によりこれらの面積を縮小する。

【解決手段】本発明の例に係る半導体装置は、半導体基板21と、半導体基板21上に積層され、導電性ポリシリコンから構成される複数の導電層R<00>〜R<04>, R<10>〜R<14>, R<20>〜R<24>, R<30>〜R<34>と、複数の導電層R<00>〜R<04>, R<10>〜R<14>, R<20>〜R<24>, R<30>〜R<34>上に配置される金属層M1とを備える。複数の導電層R<00>〜R<04>, R<10>〜R<14>, R<20>〜R<24>, R<30>〜R<34>の両端は、階段状にレイアウトされ、複数の導電層R<00>〜R<04>, R<10>〜R<14>, R<20>〜R<24>, R<30>〜R<34>は、その両端部において金属層M1を介して互いに直列接続され、抵抗素子を構成する。

(もっと読む)

絶縁ゲート型半導体装置

【課題】絶縁ゲート型半導体装置において、ゲートパッド部の下方にはトランジスタセルが配置できず、チップ上の無効領域となっていた。またソース電極層はゲートパッド部を除いて配置され、ソース電極層を基板水平方向に流れる電流の経路において、素子領域内で抵抗の偏りが発生する問題もあった。

【解決手段】電極構造を2層とし、2層目のゲート電極層(ゲートパッド部)の下方にトランジスタセルおよび1層目のソース電極層を配置する。2層目のゲート電極層は一部が1層目のゲート電極層と重畳し、これを介してゲート電極と接続する。ゲートパッド部下方にセルおよび1層目のソース電極層を配置できるので、ゲートパッド部下方の無効領域を従来と比較して大幅に低減できる。またソース電極層内を基板の水平方向に流れる電流について、全てのセルがソースパッド部から最短距離の電流経路となる。

(もっと読む)

半導体装置

【課題】チップの占有面積を有効に活用する。

【解決手段】P型半導体基板11上にN型エピタキシャル層12が形成され、LDMOSとJFETに共通なドレイン領域121を規定するP型素子分離領域13が形成される。ドレイン領域121内にボディ領域15が形成され、ボディ領域15内にN型ソース領域16が形成され、ドレイン領域121とソース領域16間のチャネル領域上にゲート電極20が配置され、LDMOSが形成される。ボディ領域15とP型素子分離領域13との間にJFETのソースとなるN型領域が形成される。ドレインに正のドレイン電圧が印加されると、PN接合が逆バイアスされ、ボディ領域15と分離領域13と半導体基板11とから空乏層が延び、JFETのチャネルを制御する。

(もっと読む)

半導体装置及び半導体装置の製造方法。

【課題】半導体装置の特性劣化を抑制し、半導体装置のサイズを縮小する技術の提供。

【解決手段】半導体装置は、半導体領域1A内に設けられる第1及び第2の拡散層2A,2Bと、拡散層2A,2B間に設けられる第3の拡散層2Cと、第1の拡散層2Aの周囲を取り囲んで、半導体領域1A表面のゲート絶縁膜3A上に設けられる第1のゲート電極4Aと、第2の拡散層2Bの周囲を取り囲んで、半導体領域1A表面のゲート絶縁膜上に設けられる第2のゲート電極4Bと、ゲート電極4A,4Bの側面上に設けられる第1及び第2の側壁絶縁膜12A,12Bとを具備し、第1及び第2のゲート電極4A,4Bは、側壁絶縁膜12A,12Bが直接接触する部分を有し、第3の拡散層2Cの周囲は、ゲート電極4A,4Bによって取り囲まれている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲートラストプロセスの適用に際して、トランジスタのフリンジ容量及びゲート抵抗の低減と、実効的なゲート長の短縮を実現する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板1上にゲート絶縁膜2、第1のダミーゲート部3及び第2のダミーゲート部4を順に積層して形成する工程と、それらをパターン加工するとともに、第1のダミーゲート部3をゲート長方向Xで第2のダミーゲート部4よりも後退させることにより、ノッチ部6を形成する工程と、ゲート絶縁膜2、第1のダミーゲート部3及び第2のダミーゲート部4の側方に絶縁材料からなる側壁7を形成し、かつ当該絶縁材料でノッチ部6を埋め込む工程と、第1,第2のダミーゲート部3,4を除去して、当該除去部分の底部にゲート絶縁膜2及びノッチ部6を残す工程と、除去部分を導電材料で埋め込むことによりゲート電極を形成する工程とを有する。

(もっと読む)

双方向スイッチ、及び半導体装置

【課題】オン抵抗を低減することのできる安定したスレッショールド電圧の双方向スイッチ、及び半導体装置を提供すること

【解決手段】本発明にかかる双方向スイッチは、P半導体基板1上に形成され、第1及び第2MOSスイッチM1、M2のドレインとなるNウェル領域2と、Nウェル領域2に設けられた第1トレンチ3内にゲート絶縁膜6を介して形成された第1ゲート電極71aと、Nウェル領域2に第1トレンチ3と離間して設けられた第2トレンチ3内にゲート絶縁膜6を介して形成された第2ゲート電極72aと、第1トレンチ3の側壁においてNウェル領域2の表面にPオフセット領域5を介して形成された第1N+ソース領域9と、第2トレンチ3の側壁においてNウェル領域2の表面にPオフセット領域5を介して形成された第2N+ソース領域10と、を備え、第1トレンチ3と第2トレンチ3との間の領域には、Nウェル領域2が形成されているものである。

(もっと読む)

61 - 80 / 373

[ Back to top ]