Fターム[5F048BG05]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 絶縁体分離 (5,896) | 素子領域側面・底面を絶縁物で分離するもの (666)

Fターム[5F048BG05]の下位に属するFターム

複数MOS(CMOS)で一部のみ (116)

複数MOS(CMOS)ですべて (452)

Fターム[5F048BG05]に分類される特許

21 - 40 / 98

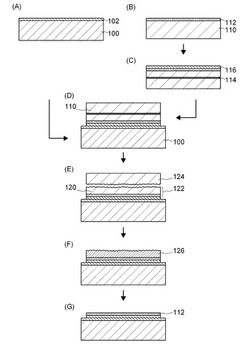

半導体基板の作製方法

【課題】炭化シリコンを含む半導体基板の新たな作製方法を提供することを目的の一とする。

【解決手段】シリコン基板表面に炭化処理を施して炭化シリコン層を形成し、シリコン基板にイオンを添加することにより、シリコン基板中に脆化領域を形成し、シリコン基板とベース基板とを絶縁層を介して貼り合わせ、シリコン基板を加熱して、脆化領域においてシリコン基板を分離することにより、ベース基板上に絶縁層を介して炭化シリコン層とシリコン層の積層構造を形成し、シリコン層を除去して炭化シリコン層の表面を露出させることにより半導体基板を作製する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

冷却機構を含む接合型半導体構造体とその形成方法

【課題】 冷却機構を有する接合型半導体基板を形成するための構造体、設計構造体、及びその形成方法を提供すること。

【解決手段】 2つの半導体基板を備える接合型基板が提供される。各々の半導体基板は、半導体デバイスを含む。少なくとも1つの基板貫通ビアが2つの半導体基板の間に設けられ、それらの間に単一の経路を提供する。2つの半導体基板の底側は、冷却機構を含む少なくとも1つの接合材料層によって接合される。1つの実施形態において、冷却機構は冷却チャネルであり、その中を通って冷却流体が流動し、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。別の実施形態において、冷却機構は、2つの端部とそれらの間の連続した経路を備えた導電性冷却フィンである。冷却フィンはヒートシンクに接続され、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子、ウェル、および回路単位で縦横方向が絶縁部材2aで分離された構造の素子3が形成された半導体装置において、高い分離耐圧を有し、さらにSOI基板を使わずに低コストで製造できる半導体装置、および、その製造方法を提供する。

【解決手段】絶縁部材2aで埋設された分離溝2と素子3とが形成された半導体基板1を、裏面1b側から絶縁部材2aの底部が突出するまで半導体基板1を薄厚化した後、絶縁層4を介して裏面1bを支持体6と接合する。これにより、絶縁部材2aの突出した部分が絶縁層4に埋め込まれた形状となり、半導体基板1における隣り合う領域が、分離溝2と絶縁層4とによって電気的に絶縁された構成となる。

(もっと読む)

縦型MOSFET

【課題】従来の縦型MOSFETは、埋め込み絶縁膜の上部に、ドレイン領域,チャネル領域,ソース領域の各領域となるための専用の半導体膜を3つ積層しなければならない。また、チャネル長は、チャネル領域となる半導体膜の膜厚で決まっていた。

【解決手段】本発明の縦型MOSFETは、埋め込み絶縁膜の上部には、ドレイン領域,チャネル領域,ソース領域の各領域となるための専用の半導体膜が必要ではなく、埋め込み絶縁膜の上部に半導体膜を少なくとも2つ積層すればよい。このため、これら半導体膜で生じる段差を少なくすることができる。また、チャネル領域を構成する半導体膜の膜厚に関係なく半導体膜に設ける拡散層の拡散深さでチャネル長を決めることができるため、チャネル長が異なるMOSFETを容易に同一の半導体基板上に構成することができる。

(もっと読む)

半導体装置および入力保護回路

【課題】静電気等の高電圧による破壊からMOSFETを保護する、SOI構造を有する入力保護回路を提供する。

【解決手段】

シリコン基板1の上に設けられた、そのシリコン基板1の表面の一部を露出させる開口部を有する埋込酸化膜2と、開口部の中に設けられたP型のシリコン層と、シリコン層と接してシリコン層の上に設けられたn型のシリコン層34と、シリコン層34に接続され、かつその一方端が入力パッドに接続され、その他方端が内部回路に接続された配線4とを備える。

(もっと読む)

半導体装置

【課題】従来のSOI基板を用いたMOS型トランジスタは、ハンプ特性を抑制するとゲート絶縁膜の絶縁性が低下するという問題があった。

【解決手段】本発明の半導体装置は、MOS型トランジスタを構成する活性領域とその周囲の素子分離領域との間に副絶縁膜を設ける。この副絶縁膜は、MOS型トランジスタを構成する主絶縁膜の一部と素子分離領域の一部とを覆うように設けている。このような構成とすることで、ゲート絶縁膜の絶縁性を低下させずにハンプ特性を改善することができる。

(もっと読む)

半導体装置とその製造方法

【課題】SGOI(110)基板上のp、n両領域で高移動度の半導体装置を実現する。

【解決手段】Si1-xGex(0.25≦x≦0.90)の(110)面を表面に有する半導体基板(1,2,3)と、(110)面上に形成されたn及びpチャネル型MISFETとを具備し、両MISFETは、[−110]方向が[001]方向より長い線状で、(311)若しくは(111)面のファセットを有する活性領域(5,6)を有し、活性領域の[−110]方向に、ソース領域・チャネル領域・ドレイン領域が形成され、nチャネル型MISFETのチャネル領域(5C)はSiで形成され、pチャネル型MISFETのチャネル領域(6C)はSi1-yGey(x<y≦1)で形成され、両MISFETのチャネル領域は、活性領域の[−110]方向に、一軸圧縮ひずみを有する。

(もっと読む)

半導体装置

【目的】チップ面積の増大を伴うことなく、高いサージ耐量を確保でき、さらにバッテリー逆接続保護もできるサージ保護素子を有する半導体装置を提供する。

【解決手段】p型半導体層1の表面層にn型拡散領域32、33が形成され、その表面には絶縁膜3を介して横型MOSFETが形成される。この横型MOSFETの下に形成された絶縁膜3下にサージ保護素子である縦型ダイオード構成する拡散領域32、33の一部を形成することにより、チップ面積の増加を伴わずに動作面積を広げることができて高いサージ耐量を確保できる。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ及び画像表示装置

【課題】簡便なプロセスで素子分離が可能な薄膜トランジスタの製造方法、薄膜トランジスタおよび画像表示装置を提供すること。

【解決手段】絶縁基板上にゲート電極、ゲート絶縁膜、一対の主電極領域を形成する工程と、一対の主電極領域上を含む絶縁基板上の全面に有機半導体層を形成する工程と、有機半導体層と一対の主電極領域との間のチャネル領域を覆う封止層を形成する工程と、有機半導体層の前記封止層の形成されていない領域を非活性化させる工程と、を備えたことを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

半導体集積回路及び製造方法

【目的】静電破壊に対して必要な保護性能を備える共に製造が容易な半導体集積回路及び製造方法を提供する。

【構成】埋め込み酸化膜上に形成されるSOI層の一部を各々が含む複数のMOSFETを含み、該複数のMOSFETのうちの少なくとも1つがESD保護トランジスタとして動作する半導体集積回路であり、該ESD保護トランジスタは、該SOI層上に形成されているゲート領域と、第1導電型を有すると共に該SOI層のうちで該ゲート領域と該埋め込み酸化膜との間に形成されている第1導電型領域と、第2導電型を有すると共に該SOI層のうちで該第1導電型領域を挟んで互いに対向する2つの第2導電型領域とを含み、 該第1導電型領域は、第1導電型濃度の高い領域をその深さ方向の中間位置よりも該埋め込み酸化膜に近い方に有する。

(もっと読む)

半導体装置及びその作製方法

【課題】N型薄膜トランジスタとP型薄膜トランジスタとを有する半導体装置を作製する場合において、TFTのばらつきを低減することを目的とする。また、マスク数の削減、製造工程数の低減、並びに製造工程期間の短縮を行うことを目的とする。

【解決手段】第1の薄膜トランジスタの島状半導体層を形成した後、第2の薄膜トランジスタの島状半導体層を形成する半導体装置の作製方法であって、前記第2の薄膜トランジスタの島状半導体層を形成する際、前記第2の薄膜トランジスタの島状半導体層と接するゲート絶縁膜を前記第1の薄膜トランジスタの島状半導体層の保護膜(エッチングストッパー膜)として兼用する。

(もっと読む)

積層型半導体集積装置

【課題】素子形成された複数の半導体層を積層し、集積可能な素子数を飛躍的に高めることができる積層型半導体集積装置を提供する。

【解決手段】本発明に係る積層型半導体集積装置は、基板上に直接、または緩衝層を介して積層されたGaN層と、前記GaN層の表面近傍に形成された複数のトランジスタと、前記トランジスタの表面及び側面を被覆する酸化膜または窒化膜と、前記酸化膜または窒化膜を含む前記GaN層上に、ELOによって積層されたAlGaN層と、を集積すべきトランジスタの数量に応じて繰り返し積層して形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 結晶欠陥の発生を防止することができる半導体装置及び半導体装置の製造方法を実現する。

【解決手段】 SOI基板11に形成され、トレンチ11eにより分離された複数の素子形成領域内に、バイポーラトランジスタ12及びCMOS13を形成するBiCMOSである半導体装置10において、バイポーラトランジスタ12の表面のみを覆って形成された耐酸化膜19を備えているため、CMOS13に熱酸化法によりゲート酸化膜24及びゲート保護膜26を形成する際にも、バイポーラトランジスタ12の表面を熱酸化しないようにすることができる。これによれば、高濃度のイオンが注入されたコレクタ16、エミッタ17などのイオン注入領域が、熱酸化されることがないので、結晶欠陥の発生を防止することができる。

(もっと読む)

半導体装置

【課題】印加されたサージによって破壊されることをより抑制することのできる半導体装置を提供する。

【解決手段】半導体装置1は、薄膜SOI基板10の薄膜SOI層40に、入力保護用のダイオード5を有する。そして、このダイオード5を構成する高濃度P型領域41に電気的に接続された電極50aと、同じくダイオード5を構成する高濃度N型領域42に電気的に接続された電極50bとのいずれか一方を介して印加されたサージが、これら両電極50a及び50bのうちの他方の電極に向けて薄膜SOI層40の内部を流れることに起因して該薄膜SOI層40で発生する熱を、熱吸収部材60の相変化を通じて吸収する。

(もっと読む)

半導体集積回路

【課題】パワー・トランジスタに流れる電流ルートを明確にすると共に、パワー・トランジスタに流れる電流の最適化を図ることにより、パワー・トランジスタへのダメージ又はストレスを低減し、信頼性に優れた半導体集積回路を提供する。

【解決手段】半導体集積回路は、パワー・トランジスタ(100A)と、パワー・トランジスタ(100A)の直上に形成され、複数の第1のバス(140〜142)と、複数の第2のバス(150〜152)と、複数の第1のバス(140〜142)及び複数の第2のバス(150〜152)の各々に1つずつ設けられたコンタクト・パッド(304)とを備える。複数の第1のバス(140〜142)と複数の第2のバス(150〜152)は、外部の接続部材(307)に近い側に位置するものから遠くに位置するものへと順に面積が小さくなるように形成されている。

(もっと読む)

半導体装置および集積回路

【課題】TFTを電気的に駆動する場合にチャネル領域から発生する熱は、例えばゲート絶縁膜などの酸化シリコン膜を介して放熱していくが、酸化シリコンの熱伝導率は1.3W/(m・K)であり、シリコンの熱伝導率148W/(m・K)と比べ2桁以上低くTFTからの放熱が妨げられるため、熱の蓄積による温度上昇に伴うリーク電流の増加などTFT電気的特性の変動を抑えることが困難となる課題がある。

【解決手段】バッファ領域13上に配線22を配置する。チャネル21で消費された電力は熱に変わり、ソース18を介してバッファ領域13側に伝導され、配線22に伝導されて外部に放出される。バッファ領域13上にゲート絶縁膜14と層間絶縁膜16を介して配線22を通すことでチャネル21で発生した熱を効果的に逃がし、また配線22を設けることで集積度を向上させた半導体装置および集積回路を得ることができる。

(もっと読む)

静電放電に対する半導体保護構造体

【課題】本発明の基礎となる課題は、静電放電に対する半導体保護構造体を、とりわけスナップバック電圧の低減の点でさらに発展することである。

【解決手段】本半導体保護構造体は、電界効果トランジスタを有する。電界効果トランジスタの半導体領域は、寄生的なバイポーラトランジスタの半導体領域も形成する。電界効果トランジスタのソースは、前記バイポーラトランジスタのエミッタを形成する。電界効果トランジスタのボディは、前記バイポーラトランジスタのベースを形成する。電界効果トランジスタのドレインは、前記バイポーラトランジスタのコレクタを形成する。これらのドレイン領域は導体を介して相互に接続される。

(もっと読む)

横型バイポーラトランジスタ

【課題】この発明はSOI構造の基板上に形成される横型バイポーラトランジスタに関し、MOSプロセスの流用により形成することができ、かつ、十分な増幅率を確保することを目的とする。

【解決手段】SOI構造の基板上にP+ベース引き出し拡散層14を形成する。P+ベース引き出し拡散層14の両側に分離絶縁膜17B,17Cを介してN+エミッタ拡散層15A,15Bを形成する。それらを囲むように、ベース拡散層として機能するP型SOI層を形成し、その上に導電層22を形成する。更にそれらを囲むように、N+コレクタ拡散層16を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】局在準位の発生を抑制すると共に、半導体層の厚みを容易且つ高精度に制御できるようにする。

【解決手段】第1絶縁層11と、第1絶縁層11を挟むように配置された第1半導体層12及び第2半導体層13とにより構成されたSOI構造10を備えている。そして、第1半導体層12は、第1活性領域15が形成されると共に、平坦化膜16を介して支持基板17に貼り付けられている。

(もっと読む)

21 - 40 / 98

[ Back to top ]