Fターム[5F058BB06]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜形成基板、処理対象 (706) | 絶縁体 (237)

Fターム[5F058BB06]の下位に属するFターム

ガラス (116)

Fターム[5F058BB06]に分類される特許

1 - 20 / 121

半導体装置、および半導体装置の作製方法

【課題】水分による電気特性劣化が抑制された半導体装置および半導体装置の作製方法を提供する。

【解決手段】トランジスタを覆う層間絶縁層に接して金属酸化物層が位置する構造とし、金属酸化物層を、アモルファス構造を有する第1の金属酸化物層と、多結晶構造を有する第2の金属酸化物層を含む積層構造とする。アモルファス構造を有する第1の金属酸化物層は結晶粒界が存在せず、また、結晶状態の金属酸化物層と比較して格子間隔が広いため格子間に水分をトラップしやすい。多結晶構造を有する第2の金属酸化物層は、結晶粒界部分を除く結晶部分については緻密な構造を有しており、水分の透過性が非常に低い。このため、第1の金属酸化物層および第2の金属酸化物層を含む金属酸化物層が層間絶縁層に接する構造とすることにより、トランジスタ中への水分の侵入を効果的に防止できる。

(もっと読む)

半導体素子

【課題】酸化物半導体層を用いた半導体素子であって、Vthの変化が抑制された、特性の安定化した半導体素子を提供する。

【解決手段】In(インジウム)およびO(酸素)を含む酸化物半導体層と、Si(珪素)、F(フッ素)およびN(窒素)を含む絶縁層と、を有する半導体素子である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、より優れたゲート絶縁膜を有する半導体装置を提供する。また、現在実用化されている量産技術からの膜構成、プロセス条件、または生産装置等の変更が少なく、半導体装置に安定した電気特性を付与し、信頼性の高い半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、を有し、ゲート絶縁膜は、窒化酸化シリコン膜と、窒化酸化シリコン膜上に形成された酸化窒化シリコン膜と、酸化窒化シリコン膜上に形成された金属酸化膜と、を含み、金属酸化膜上に酸化物半導体膜が接して形成される。

(もっと読む)

半導体装置

【課題】電流コラプスを低減し、ドレイン電流を増大しながら、ゲートリーク電流を減少できるようにする。

【解決手段】半導体装置は、基板1と、基板1の上に形成されたIII族窒化物からなる半導体層2、3と、半導体層2、3の上に、それぞれ形成されたソース電極5、ゲート電極7及びドレイン電極6と、半導体層2、3の上に、ゲート電極7の下部及び半導体層2、3と接し、且つ、ソース電極5及びドレイン電極6と離間するように形成されたシリコンを含まない第1保護膜8と、半導体層2、3の上に、半導体層2、3と接し且つゲート電極7の下部と離間するように形成され、第1保護膜8と組成が異なり且つ窒素を含む第2保護膜9とを備えている。

(もっと読む)

半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

プラズマCVD装置およびプラズマCVD方法

【課題】異常放電を抑制し、発生するパーティクルが膜に混入することを防ぎ、均一で高品質な薄膜を形成できるプラズマCVD装置および方法を提供する。

【解決手段】真空容器内に、メインロール6と、プラズマ発生電極7とを備え、長尺基材を前記メインロールの表面に沿わせて搬送しながら前記長尺基材の表面に薄膜を形成する真空成膜装置であって、前記メインロールと前記プラズマ発生電極とで挟まれる成膜空間を囲むように、前記成膜空間を挟んで前記長尺基材の搬送方向の上流側および下流側に、前記長尺基材の幅方向に延在する少なくとも1枚ずつの側壁8を設け、前記側壁は前記プラズマ発生電極とは電気的に絶縁されており、前記長尺基材の搬送方向の上流側および下流側のいずれか一方の側壁に、前記長尺基材の幅方向に一列に並んだ複数のガス供給孔が形成するガス供給孔列9を1列以上備えるプラズマCVD装置。

(もっと読む)

半導体装置

【課題】金属酸化物中の酸素欠損を低減し、電気的特性の安定した半導体装置を提供することを目的の一とする。

【解決手段】ゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の金属酸化物膜と、第1の金属酸化物膜に接して設けられたソース電極及びドレイン電極と、ソース電極及びドレイン電極上に設けられたパッシベーション膜と、を有し、パッシベーション膜は、第1の絶縁膜と、第2の金属酸化物膜と、第2の絶縁膜とが順に積層された半導体装置である。

(もっと読む)

半導体基板の表面処理方法および基板処理装置

【課題】安定して強い酸化力で基板の表面を酸化しシリル化することができる半導体基板の表面処理方法および基盤処理装置を提供する。

【解決手段】半導体基板の表面処理方法は、硫酸を電気分解して酸化性溶液を生成する工程と、酸化性溶液を用いて半導体基板の表面に酸化膜を生成する工程とを備える。酸化性溶液を用いて半導体基板の表面を酸化しOH基を生成し、半導体表面にシリル化剤を供給し、OH基とシリル化剤に含まれる有機物の加水分解により得られるOH基との結合及び脱水縮合反応により半導体基板の表面を疎水化する。

(もっと読む)

成膜方法

【課題】窒化シリコン膜と酸化シリコン膜との積層構造体を単一のプラズマCVD装置にて一貫して成膜する際に、両膜間に異質な薄膜が形成されないという機能を有しつつ、短時間で効率のよい成膜が可能な成膜方法を提供する。

【解決手段】本発明の成膜方法は、反応室2aに処理すべき基板Wを設置し、真空雰囲気中にてシリコンを含む原料ガスと窒素を含む一の反応ガスとを反応室内に導入し、放電用の高周波電力を投入してプラズマCVD法にて窒化シリコン膜を成膜する第1工程と、前記原料ガスを供給しながらプラズマ放電を維持した状態で、反応室内の窒素分圧を高める第2工程と、一の反応ガスの供給のみを停止し、酸素を含む他の反応ガスを反応室内に供給してプラズマCVD法にて酸化シリコン膜を成膜する第3工程とを含む。

(もっと読む)

シリコン含有膜の製造方法

【課題】

高い水蒸気バリア性、耐湿熱性を示すシリコン含有膜の製造方法を提供すること

【解決手段】

乾式法により少なくともケイ素原子、窒素原子を含む乾式堆積膜を基材上に堆積させた後に、膜表面に波長が150nm以下の光照射を行い、膜の少なくとも一部を変性するシリコン含有膜の製造方法。本発明の方法は、蒸着法、反応性蒸着法、スパッタ法、反応性スパッタ法、化学気相堆積法から選ばれた手法により形成され、少なくともSi−H結合、もしくはN−H結合に由来する水素を含む乾式堆積膜に好適に使用できる。

(もっと読む)

膜形成材料および膜形成方法

【課題】爆発の危険性が高いSiH4を用いずとも、安全、比較的低温度で、しかも低廉なコストでSi系膜を提供できる技術を提供することである。

【解決手段】Si系膜を形成する為の膜形成材料であって、前記膜形成材料が、t−C4H9SiX3(Xは任意の基)と、前記t−C4H9SiX3と反応する反応性化合物とを有する。

(もっと読む)

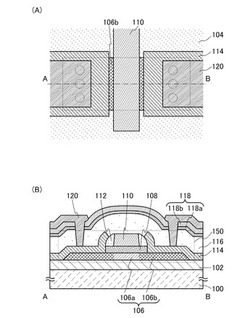

半導体装置

【課題】酸化物半導体を用いたトランジスタの電気的特性のばらつき及び電気的特性の劣化は、半導体装置の信頼性を著しく低下させる。

【解決手段】基板上に形成される酸化物半導体層と、酸化物半導体層と電気的に接続する、端部がテーパー角を有し、かつ上端部が曲面形状を有するソース電極及びドレイン電極と、酸化物半導体層の一部と接し、かつ酸化物半導体層、ソース電極及びドレイン電極を覆うゲート絶縁層と、酸化物半導体層と重畳する、ゲート絶縁層上のゲート電極と、を有する。

(もっと読む)

シリコン酸化膜のパターニング方法

【課題】シリコン酸化膜を、簡便で低コストに、パターニングする方法を提供する。

【解決手段】本発明は、基板上に油性インクのパターンを形成する工程と、前記油性インクのパターンが形成された基板上に有機ケイ素ポリマーを塗布する工程と、ホットプレート法により、前記基板上に形成された前記有機ケイ素ポリマーを酸化してシリコン酸化膜を形成すると共に、前記油性インクを分解することにより油性インクのパターン上のシリコン酸化膜を剥離し、前記油性インクのパターンとは逆のパターン形状を有するシリコン酸化膜のパターンを形成する工程と、前記シリコン酸化膜のパターンが形成された基板を洗浄して、前記分解した油性インクおよび剥離したシリコン酸化膜を除去する工程と、を有することを特徴とするシリコン酸化膜のパターニング方法である。

(もっと読む)

デバイスの製造方法

【課題】基板側面に付着した異物の効率的な除去が可能な、デバイスの製造方法を提供する。

【解決手段】基板10Aの側面に保護材3を形成する工程と、基板10Aの少なくとも一方の主面に機能層4Aを形成する工程と、保護材3を基板10Aから剥離する工程と、

を有することを特徴とする、デバイスの製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】保護膜としてSiN膜が使用されている場合であっても、素子動作特性の変動を軽減することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置2は、ドレインドリフト領域12を有する半導体基板11と、ドレインドリフト領域12上に形成されたフィールド酸化膜17と、ゲート電極18と、中間絶縁膜17と、メタル層21,22と、これらを覆うSiN膜23と、SiN膜23上にO3−TEOSを用いたCVD法により形成され、カーボンを含有するPSG膜24とを有する。

(もっと読む)

シリコンオキシナイトライド膜の形成方法およびそれにより製造されたシリコンオキシナイトライド膜付き基板

【課題】エネルギーコストを抑制できるシリコンオキシナイトライド膜の製造方法とそれにより製造されたシリコンオキシナイトライド膜付き基板の提供。

【解決手段】基板表面にポリシラザン化合物を含む被膜形成用組成物を塗布して塗膜を形成させ、前記塗膜に含まれる過剰の溶媒を除去し、溶媒除去後の塗膜を150℃未満の温度条件下で紫外線を照射することを含むシリコンオキシナイトライド膜の形成方法。

(もっと読む)

デバイス作製法

【課題】Si−O−Si結合を含む化合物等の基体に対して極めて平滑な膜を、薄膜から厚膜まで広い膜厚範囲で、マイクロ/ナノ領域に位置選択的に形成可能とした基体への膜形成法を用いた、マイクロ/ナノデバイスの作製のための基盤技術となるデバイス作製法を提供する。

【解決手段】予め改質が施された改質部分2aを有する基体2上に、マスクを密着配置して、前記改質部分2aを覆うように、気相中で膜6を位置選択的に形成する工程と、その後、前記改質部分2aのみを化学エッチングする工程とを備える。これによって、基体2及び膜6からなるマイクロトンネル構造を得る。

(もっと読む)

非晶質酸化物薄膜の製造方法及び電界効果型トランジスタの製造方法

【課題】熱処理工程時の温度ムラによる特性のバラつきを抑制し、かつ、高抵抗率に制御可能とする。

【解決手段】In、Ga及びZnを含有し、In及びGaの合計に対するGaのモル比率が0.50<Ga/(In+Ga)の関係を満たす非晶質酸化物薄膜を基板上に成膜する成膜工程と、非晶質酸化物薄膜のGaのモル比率が0.50<Ga/(In+Ga)<0.75の関係を満たす場合には、成膜工程後に100℃以上150℃以下又は350℃以上600℃以下の温度で非晶質酸化物薄膜を熱処理し、非晶質酸化物薄膜のGaのモル比率が0.75≦Ga/(In+Ga)の関係を満たす場合には、成膜工程後に100℃以上200℃以下又は350℃以上600℃以下の温度で非晶質酸化物薄膜を熱処理する熱処理工程と、を有する。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】信頼性および再現性が優れるとともに、歩留まりが高く生産性が優れた薄膜トランジスタおよびその製造方法を提供する。

【解決手段】薄膜トランジスタの製造方法は、基板上にゲート電極を形成する工程と、ゲート電極を覆って基板上に第1の絶縁膜を形成し、第1の絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第2の絶縁膜を形成して、第1の絶縁膜、酸化物半導体膜および第2の絶縁膜からなる積層体を得る工程と、積層体の第1の絶縁膜、酸化物半導体膜および第2の絶縁膜をパターニングして、それぞれゲート絶縁層、活性層およびチャネル保護層を形成する工程と、ソース電極およびドレイン電極を形成する工程とを有する。第1の絶縁膜、酸化物半導体膜および第2の絶縁膜は、大気に曝されることなく連続して形成される。

(もっと読む)

電子デバイスの製造方法、薄膜トランジスタ、電気光学装置及びセンサー

【課題】簡便に界面の欠陥を低減することを可能とする。

【解決手段】大気と遮断された真空成膜室内で、基板上に酸素不定比性のある酸化物を含有する第1層を成膜する第1成膜工程と、前記第1層上に前記第1層と同一材料又は異なる材料からなる第2層を成膜する第2成膜工程と、前記第1成膜工程後前記第2成膜工程前までの間、前記第1層を、前記真空成膜室を含む大気と遮断された室内で、前記第1成膜工程における前記真空成膜室内の酸素分圧よりも高い酸素分圧下に保持する分圧制御工程と、を有する。

(もっと読む)

1 - 20 / 121

[ Back to top ]