Fターム[5F064AA04]の内容

ICの設計・製造(配線設計等) (42,086) | ICの形式 (1,534) | カスタムIC (1,426) | セミカスタムIC (1,415) | 標準セル、スタンダードセル (922)

Fターム[5F064AA04]の下位に属するFターム

ポリセル (86)

ビルディングブロック (241)

Fターム[5F064AA04]に分類される特許

41 - 60 / 595

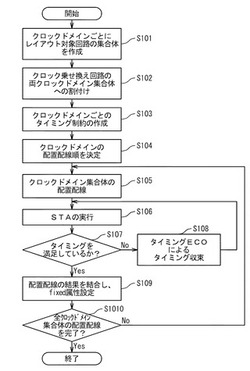

半導体集積回路のレイアウト設計方法

【課題】LSIのレイアウト設計において、TAT(Turn Around Time)を増加させることなくタイミング収束を実現する。

【解決手段】LSIのレイアウト設計方法は、レイアウト対象の集積回路のネットリストに基づいて、前記集積回路をクロックドメインに分けることでクロックドメイン回路集合体に区分する工程と、前記クロックドメイン回路集合体の各々に対するタイミング制約を作成する工程と、所定の基準に基づいて前記クロックドメイン回路集合体間の配置順序を決定する工程と、前記クロックドメイン回路集合体を前記配置順序に従って配置し配線することにより前記集積回路のレイアウトを作成する工程とを備える。レイアウト設計後のタイミング収束のTATを短縮することが可能となる。

(もっと読む)

タイミング解析方法、タイミング解析装置、およびタイミング解析プログラム

【課題】遅延計算に要する処理時間を短縮して、タイミング解析全体に要する処理時間を短縮可能とする。

【解決手段】タイミング解析方法は、半導体チップ上にレイアウトされた回路に対して電圧降下解析を行い、電圧降下解析結果に基づいて、チップ上の電圧降下を所定の電圧範囲ごとの領域として電圧降下領域ファイルを作成し、遅延のばらつきを表現する第1OCV係数が電圧降下を考慮して所定の電圧ごとに対応付けられたOCV係数ファイルを用いて、電圧降下領域ファイルの所定の電圧範囲に対応する第2OCV係数を領域ごとに算出し、算出した第2OCV係数と領域とを対応付けてOCV領域ファイルを作成し、遅延ライブラリを用いてレイアウトされた回路に対して遅延計算を行い、遅延計算結果とOCV領域ファイルの領域ごとの第2OCV係数を用いてタイミング解析を行う。

(もっと読む)

半導体設計支援装置、タイミング制約生成方法、およびプログラム

【課題】半導体集正規回路の設計時に論理合成以後にあたる下流工程に用いる設計ツールに、設計者に依存することなく適切なタイミング制約を与える。

【解決手段】半導体設計支援装置に、非同期回路を内在する電気回路の設計時に ソースコードに対して行われたCDC検証結果と 当該ソースコードのコーディングに用いられた仕様策定工程で定められた既知情報とから、ソースコードに含まれる全てのクロックについて明確化処理してCDC検証用設定ファイルとして収集取得する手段と、CDC検証用設定ファイルとCDC検証結果から得られた非同期パス毎の入出力パスと から、下流工程で用いられる設計ツールで読み込み可能な形式に合わせるように所定の情報を抽出処理してタイミング制約ファイルを生成出力する手段を設ける。

(もっと読む)

レイアウト修正・ライブラリセル置換モジュール及び半導体装置設計用EDAツール

【課題】効率的に検出率を向上する方法及び未検出箇所が不良になる確率を低減させる手法により、多層配線層の検査工程を含む半導体製品の製造技術において、検査の迅速性を損なうことなく、半導体製品の製造歩留まりを向上させる技術を提供する。

【解決手段】不良の検出が困難な未検出領域について、パターン等の変更を行い検出率、致命率の改善を行う。例えば、検出が困難な未検出領域についてパターンを追加することで検出可能とする、パターンの間隔を広げることで不良率を低下させることなどが考えられる。

(もっと読む)

デューティ調整回路の設計装置及び設計方法

【課題】任意のデューティ比であるデューティ調整回路が設計可能なデューティ調整回路の設計装置を提供する。

【解決手段】調整方法決定部は、デューティ調整回路のネットリストと、デューティ調整回路の初期状態のタイミング情報と、ドライバビリティ指定情報と、デューティ比の目標値と、を入力し、立ち上がり時間と立ち下がり時間のどちらの調整によりデューティ比の調整をするか決定する。置換セル数決定部は、調整方法決定部の決定に基づいて置き換える遅延セルの数と種類を遅延調整セルライブラリの中から選択する。遅延調整セル置換部は、置換セル数決定部の決定に基づいて、デューティ調整回路に含まれる複数の遅延調整セルの中から選択した遅延調整セルを初期状態とは異なる遅延調整セルに置き換える。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】内部電源と、該内部電源に電源を供給する補償容量部を有する半導体装置では、コンデンサの容量値が配置場所で変化するため、容量値の見積もりが煩雑になるという問題を解決する。

【解決手段】内部電源と、該内部電源に電源を供給する補償容量部を有する半導体装置の補償容量部のレイアウト配置の際に、補償容量部を構成する領域に拡散層の矩形領域を配置する。また、該拡散層の矩形領域の各辺に対し、各辺の中心が直行する箇所に矩形開口部を設ける。また、該拡散層の矩形領域の中心線近傍に沿ってゲート電極を直行するように形成する。また、該拡散層の該矩形領域の四隅に上層の金属層と接続するためのコンタクトを形成する。また、該ゲート電極と該拡散層の矩形開口部の重なる箇所にゲート電極と上層の金属層を接続するコンタクトを形成する。また、該ゲート電極が直行する箇所で容量を形成する。また、補償容量の単位セルを構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率の絶縁膜を有するnチャネル型トランジスタやpチャネル型トランジスタを有する半導体装置の製造方法において、nチャネル型トランジスタのゲート絶縁膜の側面への異物の付着を抑制する。

【解決手段】半導体基板の主表面上の、p型不純物領域PWLに機能用nチャネル型トランジスタが、n型不純物領域NWLに機能用pチャネル型トランジスタが形成される。p型不純物領域PWLの、平面視における機能用nチャネル型トランジスタ以外の領域に形成される複数の第1の周辺用トランジスタは、周辺用n型ゲート構造体と周辺用p型ゲート構造体とが混在するように形成される。

(もっと読む)

半導体集積回路装置

【課題】メーカーの設計負担を増加させることなくセルタイプの異なるICを実現することができるとともに、チップサイズおよび消費電力並びに動作速度が最適化された半導体集積回路を容易に実現可能な設計技術を提供する。

【解決手段】所望の機能を有する回路セルの設計情報を目的別にオブジェクトとして記述し、所定のオブジェクトの情報の削除もしくは追加のみで基体電位固定型セルと基体電位可変型セルのいずれをも構成可能なセル情報として、セルライブラリに登録するようにした。

(もっと読む)

集積回路のレイアウト設計方法、レイアウト設計装置、及び設計プログラム

【課題】高駆動素子が含まれている論理素子経路に遅延素子を挿入してホールドタイム違反を解消する際に、セットアップタイム違反が新たに発生することを防止する。

【解決手段】レイアウト設計方法が、第1フリップフロップ101と、第2フリップフロップ102と、第1フリップフロップ101の出力と第2フリップフロップ102の入力の間の論理回路とを含む集積回路について配置及び配線を行うステップと、ホールドタイム違反を検出するステップと、遅延素子302をホールドタイム違反を解消するように挿入するステップとを備えている。遅延素子302を挿入するステップでは、第1フリップフロップ101と第2フリップフロップ102間の論理素子経路に高駆動素子105が配置されているかが確認され、高駆動素子105が配置されている場合、高駆動素子105の出力に直接に接続されないように遅延素子302が配置される。

(もっと読む)

半導体装置

【課題】 データ保持回路を備えた半導体装置において、回路面積の低減及び動作速度の向上を図ること。

【解決手段】 本半導体装置100は、少なくとも1以上の不揮発性のメモリセルFCと、メモリセルFCへの書き込みデータ又はメモリセルFCからの読み出しデータを格納するラッチ回路30とを含み、メモリセルFC及びラッチ回路30がアレイ状に配置された複数の不揮発性メモリ回路20と、複数の不揮発性メモリ回路20におけるラッチ回路30のそれぞれに接続され、データを一時的に保持する複数のデータ保持回路10と、を備える。

(もっと読む)

半導体装置

【課題】2つの入力端子の配置形態を工夫することにより配線層の増設スペースを確保しスタンダードセルの原価低減を図る。

【解決手段】入力端子34bはゲート配線2bに接続され、入力端子34cはゲート配線2cに接続される。また、入力端子34b、34cは、Y方向に互いに近接して配置され、入力端子34bの第2コンタクト配線4bは、第1コンタクト配線3bと隣接し、且つ該第1コンタクト配線3bに対しX方向に延在する。入力端子34cの第2コンタクト配線4cは、第1コンタクト配線3cと隣接し、且つ該第1コンタクト配線3c対して第2コンタクト配線4bとは逆のX方向に延在する。即ち、入力端子34bの第1コンタクト配線3bと入力端子34cの第2コンタクト配線4cとはY方向に互いに対向して配置され、入力端子34bの第2コンタクト配線4bと入力端子34cの第1コンタクト配線3cはY方向に互いに対向して配置される。

(もっと読む)

回路設計支援装置、回路設計支援方法および半導体集積回路

【課題】半導体集積回路の遅延時間の変動を抑制すること。

【解決手段】回路設計支援装置1は、選択部1bと配置部1cとを有している。選択部1bは、設計対象の半導体集積回路モデルが備えるレジスタモデル2bにクロック信号を供給するクロック信号線の分岐点P1からレジスタモデル2bのクロック信号入力端子に至る第1の経路と、分岐点P1からレジスタモデル2bのデータ信号入力端子に至る第2の経路の、配線に関する物理パラメータの差分値に基づいて、物理パラメータが異なる配線負荷を有する複数の遅延回路モデルから遅延回路モデルBを選択する。配置部1cは、選択された遅延回路モデルBをデータ信号入力端子に接続されるデータ信号線に配置する。

(もっと読む)

回路設計支援装置、回路設計支援方法および半導体集積回路

【課題】配線の遅延特性のばらつきを抑制すること。

【解決手段】回路設計支援装置1は、設定部1aと生成部1bとを有している。設定部1aは、半導体集積回路モデル2の層2a、2bそれぞれに、積層方向および面方向に隣接するユニット3の配線方向が互いに異なる方向に配線が生成される複数の矩形のユニット3を設定する。生成部1bは、ユニット3の境界で異なる層のユニット3に跨る配線を生成する。

(もっと読む)

回路レイアウト設計システム、リーク対策セル、回路レイアウト設計方法及びプログラム

【課題】正規回路のタイミングを変えずに、未使用セル群の全てのセルのダイナミック電流及びチャンネルリーク電流を削減することができる回路レイアウト設計システムを提供する。

【解決手段】本発明の回路レイアウト設計システムは、レイアウトデータから、出力端子がオープン状態の未使用インバーターセルを検出する出力オープンセル検出部と、オープンセル検出部が検出した未使用インバーターセルの出力オープンセル情報を、出力オープンセル情報ファイルに格納する出力オープンセル情報抽出部と、レイアウトデータから、未使用インバーターセルを削除する出力オープンセル削除部と、出力オープンセル情報のセル名を、リーク対策セルに対応するセル名に変換した置換情報ファイルに格納するセル名変換部と、置換情報ファイルを参照して、レイアウトデータの未使用インバーターセルをリーク対策セルに置換する出力オープンセル置換部とを備える。

(もっと読む)

クロックツリー生成装置及びクロックツリー生成方法

【課題】クロック遅延などを調整し易くすることで、タイミングエラーを適切に収束させる。

【解決手段】クロックツリー生成装置は、クロックツリーに関する情報と、クロックツリーに含まれる複数のフリップフロップが用いている複数のクロックに関する情報とを取得する取得手段と、取得手段によって取得された複数のクロックごとに、それぞれのクロックで駆動されるフリップフロップの数を特定するフリップフロップ数特定手段と、フリップフロップ数特定手段によって特定された複数のクロックごとのフリップフロップの数に基づいて、複数のクロックの中でフリップフロップの数が少ない上位のクロックを所定数だけ特定するクロック特定手段と、クロック特定手段によって特定されたクロックで駆動されるフリップフロップを基準にして、クロックツリーを分割する分割手段と、を備える。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の設計プログラム

【課題】半導体装置において、所望の数のトランジスタをハンドリングすること。

【解決手段】半導体装置は、半導体基板内に形成された第1導電型の第1から第4の拡散層と、半導体基板内に形成された第2導電型の第5から第8の拡散層と、第1と第2の拡散層の間及び第5と第6の拡散層の間の上方に形成された第1の電極と、第3と第4の拡散層の間及び第7と第8の拡散層の間の上方に形成された第2の電極と、第6の拡散層と第7の拡散層との間の上方に形成された絶縁膜及び第3の電極を備える。第3の電極は、第1電位に接続されている。

(もっと読む)

未知の半導体装置の機能の非破壊的な決定

【課題】外部放射線に対して応答する接合を分析することを通して機能を推測することによる、集積回路の非破壊的なリバースエンジニアリングのためのシステム及び技術を提供する。

【解決手段】少なくとも1つの電源と電気的に導通している複数の半導体接合を含む半導体装置の機能を決定するための以下を含む方法。

・半導体装置の表面を照射すること;

・照射に応答する複数の半導体接合のうち少なくとも幾つかのレイアウトを決定すること;

・決定されたレイアウト内で、複数の半導体接合の少なくとも幾つかのグルーピングを同定し、各ブルーピングはそれぞれの機能セルを表すこと;

・複数の外部アクセス可能な接点のうち少なくとも1つへの刺激を変化させること;及び

・前記変化した刺激に応答して複数の相互接続された機能セルの1つ以上の接続を推測すること。

(もっと読む)

制御電圧生成回路、定電流源回路及びそれらを有する遅延回路、論理回路

【課題】回路規模を増大させることなくトランジスタの閾値電圧に応じた制御電圧を精度良く生成することが可能な制御電圧生成回路を提供すること。

【解決手段】本発明にかかる制御電圧生成回路は、高電位側電源と低電位側電源との間に直列に接続された同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのドレイン電圧を参照電圧Vp1として生成する参照電圧生成部11と、高電位側電源と低電位側電源との間に直列に接続され参照電圧生成部11と同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのゲートに参照電圧が供給され、何れかのMOSトランジスタのドレイン電圧を制御電圧(バイアス電圧)として出力する電圧変換部12と、を備える。

(もっと読む)

半導体集積回路のレイアウト変更方法および、レイアウト装置及び半導体集積回路

【課題】 最小限度の層の変更のみでレイアウト変更を可能にし、マスク製作費用を最小限に抑え、変更箇所以外でのタイミングを保持する。

【解決手段】 半導体集積回路のレイアウト変更方法は、半導体集積回路のレイアウト上の所定の箇所に、既存の配線層とは接続しない不接続層を含む複数層にわたるスタック構造のダミービアをあらかじめ配置し、レイアウト変更時に、所望の位置のスタック構造のダミービアに接続する新規配線を配置し、当該選択されたダミービアの前記不接続層にビア層を挿入する。

(もっと読む)

半導体集積回路の設計方法

【課題】設計期間の短縮が可能な半導体集積回路の設計方法を提供する。

【解決手段】本実施形態によれば、半導体集積回路の設計方法は、第1配線層、前記第1配線層上に設けられる第2配線層、及び前記第2配線層上に設けられる第3配線層を有する半導体集積回路の設計方法である。この方法は、前記第2配線層に、第1方向に沿って複数のスペア配線を配置し、前記第3配線層に、前記第1方向に直交する第2方向に沿って複数のスペア配線を配置する工程を備える。さらに、この方法は、前記スペア配線の配置後に、前記第1配線層に素子を配置する工程と、前記素子の配置後に、前記第1乃至第3配線層の少なくともいずれか1つに信号配線を配置する工程と、前記スペア配線を用いて、配線の設計変更を行う工程と、を備える。

(もっと読む)

41 - 60 / 595

[ Back to top ]