Fターム[5F064AA04]の内容

ICの設計・製造(配線設計等) (42,086) | ICの形式 (1,534) | カスタムIC (1,426) | セミカスタムIC (1,415) | 標準セル、スタンダードセル (922)

Fターム[5F064AA04]の下位に属するFターム

ポリセル (86)

ビルディングブロック (241)

Fターム[5F064AA04]に分類される特許

21 - 40 / 595

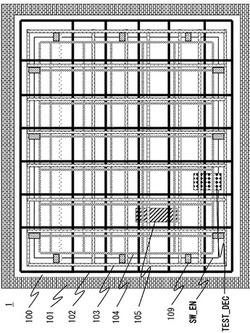

半導体集積回路および半導体集積回路の設計方法

【課題】半導体集積回路の面積を増大させることなく、配線性のよいテスト専用回路の電源遮断を実現する半導体集積回路を提供する。

【解決手段】テスト実行時のみ動作するテスト専用回路を有する半導体集積回路1であって、当該半導体集積回路1の内部回路領域(内部制御回路部100)に電源を供給する通常電源(通常動作用電源)104と、当該内部回路領域の全面にメッシュ状に配線され、テスト専用回路に電源供給するテスト用電源103と、テスト用電源103と通常電源104とを接続及び遮断して、通常電源104からテスト用電源103への電源供給を制御する電源遮断スイッチ109と、を備える。

(もっと読む)

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップサイズ見積もり方法

【課題】精度よく簡便にチップサイズを見積もることができる、半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップ見積もり方法を提供する。

【解決手段】回路の機能の実現に最小限必要なゲート数である最小機能ゲート数を入力する入力部1と、セルライブラリごとに所定の動作速度の達成に必要となるゲート数と前記最小機能ゲート数との比率である性能考慮ゲート数係数が予め設定された設定値保持部21と、前記最小機能ゲート数と前記性能考慮ゲート数係数とから算出されるゲート数を用いて前記回路の総面積を見積もる計算部22と、を備えたことを特徴とする。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップ面積の増大を抑制しつつ、ダミー配線パターンの配置にかかる工数を低減する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、レイアウト領域に対して、半導体集積回路の配置配線(S1)を行った後、レイアウト領域に配置されているバルクセルを抽出し(S2)、レイアウト領域において、抽出したバルクセルの周囲に、所定の大きさを備える空き配線領域が存在するかどうかを検索し(S3)、検索の結果、所定の大きさを備える空き配線領域を検出した場合、抽出したバルクセルの座標を基準にして、検出した空き配線領域にダミー配線パターンを配置(S4)する。

(もっと読む)

セル・ライブラリから選択された信号スキュー調整セルを備えた集積回路

【課題】 少なくとも1つのデジタル論理セルおよび少なくとも1つのスキュー調整セルを有するデジタル回路機構を備えた集積回路を提供すること。

【解決手段】 スキュー調整セルは、集積回路のデジタル回路機構における信号のスキューを所望の量に調整するように構成される。デジタル論理セルおよびスキュー調整セルはセル・ライブラリから選択される。

(もっと読む)

ガードバンドセル及びガードバンド

【課題】電源供給が遮断されるIO領域が存在する場合でも、ランダムロジック領域内でのラッチアップの発生を防止するガードバンドセル及びガードバンドを提供すること。

【解決手段】本発明の一態様に係るガードバンドセル11は、NウェルNW1を有する。また、本発明の一態様に係るガードバンドセル11は、NウェルNW1の上に形成された、Nウェル層と同じ導電型であるN型ガードバンド拡散層NGB1を有する。N型ガードバンド拡散層NGB1は、十分な低抵抗の配線により、ランダムロジック領域2の電源電位と接続される。

(もっと読む)

レイアウト設計方法及びレイアウト設計装置

【課題】チップ面積を小さくすることのできるレイアウト設計方法を提供する。

【解決手段】レイアウト設計方法は、所定のタイミング制約F1を満足させるように、セルを配置し、低抵抗配線が形成される第1配線層を使用してセル間のパスの接続配線を形成する処理(ステップS2〜S4)を有する。また、レイアウト設計方法は、タイミング制約F1を満足させたまま、パスの接続配線のうち、セル間に配置されるバッファ回路によって区切られる複数のステージ中の少なくとも一つのステージに対応する接続配線におけるレシーバ側からの一部を、第1配線層から該第1配線層よりも配線遅延が大きくなる第2配線層に置き換えて形成する配線置換処理(ステップS5)を有する。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップサイズを縮小する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、半導体集積回路のレイアウト設計を階層別に行う階層レイアウト設計における上位階層において、上位階層の下の階層で配置配線が行われる所定の機能を備えた階層ブロックが配置される領域であって、空きユニットセル配置領域3と階層ブロック用のユニットセル配置領域4とを含む階層ブロック配置領域2を、チップ領域1に設定し、チップ領域1における階層ブロック配置領域2を包囲する周辺領域5のユニットセル配置領域、および、階層ブロック配置領域2内の空きユニットセル配置領域3を用いて、配置配線を行う。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、レイアウトの面積効率の低下を抑制可能となる、マルチハイトセルのレイアウト構造を提供する。

【解決手段】標準論理セル10は、電源配線または接地配線となるメタル配線12を共有するようにY方向に隣接して配置された第1および第2回路領域A1,A2を備えている。X方向において、第1回路領域A1の両端部の位置x1a,x1bと第2回路領域A2の両端部の位置x2a,x2bとは、少なくともいずれか一方が異なっている。すなわち、標準論理セル10の外形形状CFは、第1および第2回路領域A1,A2の外形形状が矩形であるにもかかわらず、非矩形となっている。

(もっと読む)

半導体集積回路のレイアウト装置、レイアウト方法及びそれらに用いられるセルデータ

【課題】タイミング違反を容易に解消して工数の増大を抑制すること等が可能な半導体集積回路のレイアウト装置を提供すること。

【解決手段】本発明にかかる半導体集積回路のレイアウト装置は、セルデータを記憶する記憶装置13と、記憶装置13からセルデータを読み出して自動配置配線を行うレイアウト部242と、を備える。また、セルデータは、ターゲットセルに対する配置の状況に応じた遅延をターゲットセルに対して付加する遅延考慮フィラーセルの情報を有する。

(もっと読む)

半導体集積回路装置

【課題】標準論理セルのセル高さを縮小する。

【解決手段】第1,第2,第3の電源配線(WP1,WP2,WP3)および複数の第1の信号配線(WS1)は、半導体基板の上層に形成され、少なくとも1つの第2の信号配線(WS2)は、複数の第1の信号配線(WS1)の上層に形成される。第1および第2の電源配線(WP1,WP2)は、セル高さ方向に互いに離間してセル幅方向に延伸する。第3の電源配線(WP3)は、第1および第2の電源配線(WP1,WP2)の間をセル幅方向に延伸する。複数の第1の信号配線(WS1)は、第1,第2,第3の電源配線(WP1,WP2,WP3)から離間し、複数の回路要素(DF,GW)の少なくとも1つに電気的に接続される。少なくとも1つの第2の信号配線(WS2)は、セル幅方向に延伸し、複数の回路要素(DF,GW)および複数の第1の信号配線(WS1)の少なくとも1つに電気的に接続される。

(もっと読む)

半導体集積回路装置

【課題】セル高さが低減した場合であっても、容量セルの容量値を十分に確保可能なレイアウト構成を提供する。

【解決手段】第1の電源電圧を供給する電源配線11が第1の方向に延びており、電源配線11と平行に、第2の電源電圧を供給する電源配線12および第3の電源電圧を供給する電源配線13が延びている。容量素子16は、ソースおよびドレインに第1の電源電圧が与えられ、ゲートに第2または第3の電源電圧が与えられるトランジスタによって構成されている。容量素子16は電源配線11の下に、電源配線12側の領域から電源配線13側の領域にわたって形成されている。

(もっと読む)

半導体装置

【課題】半導体装置の電源線および接地線の高抵抗化を抑制する。

【解決手段】第1の方向に延伸された第1の回路セル列及び第2の回路セル列と、第1の方向に延伸され、第1の回路セル列上に配置され、第1の電源線には第1の電源電位が供給される、第1及び第2の電源線と、第1の方向に延伸され、第2の回路セル列上に配置され、第2の電源電位が供給される第3の電源線と、第2の電源線と第3の電源線との間に接続され、導通状態において第2の電源線と第3の電源線とを接続して第3の電源線から第2の電源線に第2の電源電位を供給し、非導通状態において第2の電源線と第3の電源線とを電気的に切り離す第1のトランジスタと、第1の回路セル列に配置され、第1の電源線から供給される第1の電源電位と第2の電源線から供給される第2の電源電位との間の電源電圧で動作する第1の回路素子とを備える。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、及び設計支援装置

【課題】半導体集積回路の設計TATを短縮する。

【解決手段】本発明による半導体集積回路の設計方法は、コンピュータ装置10によって実行される半導体集積回路の設計方法であって、論理セル500と配線セル400をチップ上に配置するステップと、論理セル500内のゲート505に対するアンテナルール122を配線セル400の第1アンテナ用ライブラリ101に追加することで、第1アンテナ用ライブラリ101を第2アンテナ用ライブラリ201に変更するステップと、配線セル400と他の論理セル510を第1配線550で接続するステップと、第2アンテナ用ライブラリ201に規定されたアンテナルール122に従い、ゲート505の面積に対する前記第1配線550の面積の比を検証する第1検証ステップとを具備する。

(もっと読む)

論理回路の遅延計算・タイミング検証方法および遅延検証装置

【課題】より実動作に近いタイミング判定を行う。

【解決手段】遅延計算・タイミング検証方法は、被検証回路を示すネットリストを保持するステップと、被検証回路に含まれる順序回路間のパスを抽出するステップと、順序回路の出力がメタステーブル状態になることを許容して設定されるセットアップ時間およびホールド時間を示す緩和制約時間に対する入力信号のタイミング余裕度を算出するステップと、タイミング余裕度に基づいて、順序回路の出力信号の値が確定する出力遅延時間を算出するステップと、順序回路間のパスにおける遅延時間を示す伝搬遅延時間を算出するステップと、出力遅延時間と伝搬遅延時間と緩和制約時間とに基づいてタイミング検証するステップとを具備する。

(もっと読む)

半導体装置の設計支援装置、設計支援プログラム及びレイアウト情報生成方法

【課題】従来の設計支援装置により生成したインダクタは、周囲の回路の影響により特性ずれが生じる問題があった。

【解決手段】本発明の設計支援装置は、生成対象のインダクタに接続される接続対象回路領域の第1、第2の接続端子の位置情報を回路設計情報から生成されるフロアプラン結果から得て、インダクタを他の回路と接続する第3、第4の接続端子を、第1の接続端子と第3の接続端子との間及び第2の接続端子と第4の接続端子との間が最短の配線によって接続可能な位置に設定する端子位置設定部10と、第3、第4の接続端子の位置を基準としてインダクタの配線パターンを生成し、当該配線パターンに基づきインダクタのレイアウト情報を生成するパターン生成部13と、を有する。

(もっと読む)

レイアウト設計方法、レイアウト設計プログラム及びレイアウト設計装置

【課題】被クリップセルとクリップセル間の配線引き回しを抑え、配線引き回しに起因した不具合を回避する。

【解決手段】レイアウト設計において、ネットリストを用い、被クリップセルと、その被クリップセルに接続されるクリップセルとを抽出し(ステップS1)、抽出された被クリップセルとクリップセルとを関連付けた関連付け情報を生成する(ステップS2)。そして、生成された関連付け情報に基づき、被クリップセルとクリップセルとを隣接させる等して一体で配置し(ステップS3)、配置された被クリップセルとクリップセルとを配線で接続する(ステップS4)。

(もっと読む)

半導体装置

【課題】小型化を実現し得る半導体装置を提供することにある。

【解決手段】半導体基板に形成され、素子分離領域により画定された第1の素子領域12bと、第1の素子領域上に形成された第1のゲート電極21bと、第1のゲート電極の第1の側における第1の素子領域に形成された第1のソース領域32Sと、第1のゲート電極の第2の側における第1の素子領域に形成された第1のドレイン領域32Dとを有する第1のトランジスタ36と、第1のゲート電極の第1の側における素子分離領域上に、第1のゲート電極と並行するように形成された第1のパターン38aと、第1のソース領域に接続された第1の導体プラグ44cとを有し、第1の導体プラグは、接地線及び電源線のうちの一方に電気的に接続されており、第1のパターンは、接地線及び電源線のうちの他方に電気的に接続されている。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

半導体集積回路の設計方法及び半導体集積回路の設計支援装置

【課題】論理回路の面積縮小化を実現しつつ、設計TATの短縮を可能とする技術を提供する。

【解決手段】複合論理マクロセルを、基本マクロセルに置き換えて面積の総和を抽出し、その面積の総和と複合論理マクロセルの面積とを比較して面積縮小化に有効となる複合論理マクロセルを選択する。その選択された複合論理マクロセルにフラグを設定する。フラグを設定したマクロセルと同等の論理を論理情報から検索する論理構造検索処理を行い、置換対象となる基本マクロセルにフラグを設定する。置換対象のフラグを設定した基本マクロセルを、フラグ設定した複合論理マクロセルに置き換える等価論理置換処理を行う。

(もっと読む)

21 - 40 / 595

[ Back to top ]