Fターム[5F064CC12]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | トランジスタ (1,639) | FET (1,516) | MOS−FET(MISも含む) (1,456) | CMOS (629)

Fターム[5F064CC12]に分類される特許

141 - 160 / 629

半導体装置およびその製造方法

【課題】基板上にヒューズ素子を備える半導体装置において、ヒューズを切断しやすくし、かつヒューズ切断状態を確実に得る。

【解決手段】半導体装置1は、基板10上に、MIPS構造を有するMOSトランジスタとヒューズ素子100を備える。ヒューズ素子100は、基板10の上に設けられた金属膜28と、金属膜28の上に設けられた絶縁膜30と、絶縁膜30の上に設けられたシリコン層34と、シリコン層34の上の少なくとも一部を覆うシリサイド層73と、からなる。

(もっと読む)

半導体装置

【課題】半導体を実装するプリント基板の不要輻射経路の複雑化、不要輻射の影響を抑制するとともに、コスト増を抑制することが可能な半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、第1動作周波数又はサンプリング周波数により動作する第1論理回路ブロック10と、第1論理回路ブロック10に、第1電源配線12を介して接続された第1電源端子11及び第1接地配線14を介して接続された第1接地端子13と、第1動作周波数又はサンプリング周波数と異なる第2動作周波数又はサンプリング周波数により動作する第2論理回路ブロック20と、第2論理回路ブロック20に第2電源配線22を介して接続された第2電源端子21及び第2接地配線24を介して接続された第2接地端子23とを備える。

(もっと読む)

トリミング回路

【課題】トリミング処理部にヒューズ等の配線の再接続対策を施した場合でも、その再接続判定結果を保持するための特別なレジスタを不要とし、製造コストを最小限に抑えることが実現できるようにする。

【解決手段】トリミングデータをトリミング対象回路140に入力させることによって該トリミング対象回路140の回路特性値を調整するとき、トリミング対象回路140に入力させるトリミングデータを格納するシフトレジスタ130と、ヒューズの切断/非切断によってトリミングデータを発生するトリミング処理部110と、プリテスト時に外部入力したテスト用のトリミングデータTDATAをシフトレジスタ130に転送し、実際のトリミング時にトリミング処理部110で発生したトリミングデータをシフトレジスタ130に転送するセレクタ部120とを備える。

(もっと読む)

半導体集積回路装置

【課題】 半導体集積回路装置の特性を保持或いは高めると共に小型化を図る。

【解決手段】 主面および前記主面とは反対側の裏面を有し、第1辺を含む平面形状が矩形状の半導体基板と、前記主面上に形成された複数のボンディングパッドと、前記主面上に形成された内部回路形成部と、前記第1辺と前記内部回路形成部との間に配置されており、前記内部回路形成部に電位を供給する内部回路用電源配線と、前記第1辺と前記内部回路用電源配線との間に配置されており、前記複数のボンディングパッドと電気的に接続され、トランジスタを備えた複数のセルと、前記複数のセル上に配置され、前記複数のセルに電位を供給するセル用電源配線と、を有し、前記複数のセルは、外部からの入出力信号を送受信する回路を含む入出力セルを有し、前記複数のボンディングパッドのそれぞれは、前記入出力セルと平面的に重なるように配置されている。

(もっと読む)

ヒューズ回路及びそれを備える半導体装置

【課題】ヒューズを含む電流経路で駆動される出力端の電圧レベルを所定の電圧レベルと比較できるヒューズ回路を提供すること。

【解決手段】本発明のヒューズ回路は、ヒューズイネーブル信号EN_ADDに応答してヒューズ412を含む電流経路を介して出力端COMを駆動するヒューズ部410と、所定レベルの基準電圧VREFと前記出力端の電圧レベルとを比較し、ヒューズ状態信号FOUTを生成する比較部450とを備える。

(もっと読む)

半導体集積回路

【課題】半導体集積回路の動作速度を向上し、アクティブ時の消費電力、スタンバイ時の消費電力を共に低減し、チップ面積を小さくする。

【解決手段】半導体集積回路は、クロックにより制御される第1、第2、第3フリップフロップ回路、第1論理回路段及び第1論理回路段より段数の少ない第2論理回路段を有する。第1電位を有する第1電位組を動作電源とする第1論理ゲートと第1電位より小さい第2電位を有する第2電位組を動作電源とする第2論理ゲートを含む。第1論理ゲートを構成する第1MISトランジスタはウエル領域に第1電位組の何れかの電位が与えられる。第2論理ゲートを構成する第2MISトランジスタはウエル領域に第1電位組の何れかの電位が与えられる。第2論理回路段は、第1論理回路段より第2論理ゲートの数が多い。

(もっと読む)

ヒューズ回路

【課題】種々の半導体用途において使用されるヒューズ回路を提供する。

【解決手段】ヒューズ回路は、インタクト状態とブロー状態を有するヒューズを備える。上記ヒューズは、上記ヒューズにブロー電流を流すことにより、ブロー状態に切り換えられる。上記ヒューズは、第1のトランジスタと第2のトランジスタとの間に直列に接続される。上記第1のトランジスタおよび第2のトランジスタは、相補的なトランジスタであり、上記ヒューズを流れる静電放電電流を低減するように作動する。第1のトランジスタおよび第2のトランジスタは、ターンオンされて、上記ヒューズにブロー電流を流す。

(もっと読む)

スタンダードセルおよび半導体装置

【課題】回路動作に必要な配線を形成するための領域が広く、回路の高速動作が可能なスタンダードセルを提供する。

【解決手段】第1のMOS素子および第2のMOS素子に信号を供給するための信号線が、電源配線および接地配線の2つの配線と平行に設けられ、これら2つの配線に挟まれ、かつ、第1の導電型MOS素子および第2の導電型MOS素子のそれぞれから等しい距離に配置されている構成である。

(もっと読む)

半導体集積回路装置およびその設計方法

【課題】オフリーク電流を抑制でき、動作速度および駆動力に優れた半導体集積回路装置およびそのような半導体集積回路装置の設計方法を提供する。

【解決手段】スタンダードセルを配置して動作タイミングおよび消費電力の少なくともいずれかを解析し、得られた解析結果に基づいて特性の改善が望まれるスタンダードセルを着目セルとして特定し、ウェル近接効果の影響を考慮して前記着目セル周辺の空き領域の配置および形状を最適化し、最適化された空き領域のうち、ウェル近接効果を利用できる空き領域を特定し、特定された空き領域のレイアウト、または特定された空き領域および前記着目セルのレイアウトを、所望の特性に応じてウェル近接効果の影響が変動するように変更する。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】

使用現場で使用者や顧客の要望に応じて、回路システムを形成することのできる薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】

薄膜トランジスタ装置において、TFTにより構成した複数の集積回路ブロック1,2と、これらの集積回路ブロックを相互に接続するための網目状に交差したマトリックス配線3、4、5、6を設ける。相互の集積回路ブロック間の接続は、使用現場で使用者や顧客の要望に応じて導電性材料を印刷等により、マトリックス配線の各々の配線交差部に選択的に設けることにより行い、所望の回路システムを構成する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路の回路修正時の変更を最小限度にする。

【解決手段】半導体集積回路に適用されるクロックドインバータCLKINV1は、PchMOSトランジスタPMT11、PchMOSトランジスタPMT12、NchMOSトランジスタNMT11、及びNchMOSトランジスタNMT12から構成され、3層目配線までのレイヤを用いてセル内の論理が構成され、セル内のセカンドビア(2’nd Via)の配置を変更することにより、入力の接続先或いは出力の接続先を変更することができる構造となっている。

(もっと読む)

半導体製品ダイのテスト方法及び同テストのためのテストダイを含むアセンブリ

【課題】製品ダイ(2011,300)の製品回路(202,302,304)をテストするためのテストアセンブリ(2000)を提供すること。

【解決手段】一実施形態では、テストアセンブリは、テストダイ(2010,400)及び該テストダイをホストコントローラ(2002)へ電気的に結合する相互接続基板(2008)を含む。該テストダイは、テスト回路(202A,402,404)及び製品回路を統合化された設計(102)に同時に設計するステップを含むテストダイ及び製品ダイに関する設計方法論(100)に従って設計可能である。テスト回路は、該テスト回路により必要とされるシリコン領域の量にほぼ関係なく、対応する製品回路に関して高度の欠陥検出範囲を提供するよう設計可能である。次いで該設計方法論は、統合化された設計をテストダイ及び製品ダイへと分割する(104)。テストダイはテスト回路を含み、製品ダイは製品回路を含む。

(もっと読む)

XOR及びXNORロジックの回路及びレイアウト

XOR回路は、第2の入力ノードによって制御されるパスゲートを備える。そのパスゲートは、制御されたとき、第1の入力ノードに存在するロジック状態のバージョンを出力ノードに通すように接続されている。伝送ゲートが、第1の入力ノードによって制御される。その伝送ゲートは、制御されたときに、第2の入力ノードに存在するロジック状態のバージョンを出力ノードに通すように接続されている。プルアップロジックが、第1及び第2の入力ノードの両方によって制御される。そのプルアップロジックは、第1及び第2の入力ノードの両方がハイのときに、出力ノードをロウに駆動するように接続されている。XNOR回路は、プルアップロジックが、第1及び第2の入力ノードの両方がハイときに出力ノードをハイに駆動するように接続されたプルダウンロジックに置換されることを除いて、XOR回路と同様に画定される。  (もっと読む)

(もっと読む)

集積半導体回路

【課題】ダミーゲートアレイのPN貫通電流による短絡現象により、本来の集積半導体回路構成の不良率に不良率が上乗せされるので、本来の集積半導体回路構成の不良率より高い不良率となっていまい、本来の回路の収率より集積半導体回路全体の収率が下がっていたので、本来の回路が正常であれば、ダミーゲートアレイに不良があってもそのダミーゲートアレイさえ使わなければ正常動作する集積半導体回路を提供する。

【解決手段】メタル層で配線がなされるとともにダミーゲートアレイを有する集積半導体回路において、ダミーゲートアレイの電源回路にスイッチング素子を設けたことを特徴とする集積半導体回路を提供する。

(もっと読む)

半導体装置およびそれを用いた情報処理装置

【課題】LSIに複数の電源を供給して回路ブロックごとに必要な電圧の電源を供給し、LSIの必要情報処理能力を維持したまま消費電力を最小化するとともに、電源の供給に必要な配線を極力低減し、2種類の電源を供給することによって発生する、LSIのチップ面積の増加や信号配線の性能低下を抑えることである

【解決手段】2種類の電源が供給されるLSIにおいて、高い電圧の電源の配線の密度を、低い電圧の電源の配線の密度よりも高くする。これにより、回路ブロックの性能にしたがって供給する電源を選択することによって、LSIで処理される情報量を高く保ったまま、不必要な電力を抑制し、消費電力を低減することが可能である。

(もっと読む)

レイアウト設計装置、レイアウト設計方法、及びレイアウト設計プログラム

【課題】チップサイズが小さくなるように、半導体集積回路を設計できるレイアウト設計装置を提供する。

【解決手段】ネットリスト及び遅延情報に基づいて、タイミング解析を行うタイミング解析部103と、タイミング解析にタイミングエラーが生じる場合、タイミングエラーに関連している調整対象セルを抽出する調整対象抽出部104と、第1セル枠は調整対象セルの境界線であり、第2セル枠の外側に第1拡散領域を有する複数の補強フィルセルを格納する補強フィルセルライブラリ105と、第2セル枠は複数の補強フィルセルの各々の境界線であり、調整対象セルに隣接する通常フィルセルと同じ大きさの第1補強フィルセルを、複数の補強フィルセルから抽出し、第1セル枠と第2セル枠とが隣接配置するように通常フィルセルを第1補強フィルセルに置き換え、トランジスタと第1拡散領域とを接続するセル置換部106とを具備する。

(もっと読む)

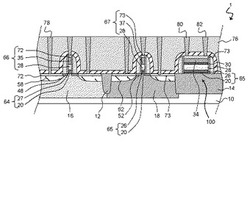

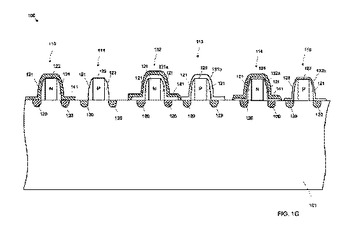

ストレス低減層を有する集積回路装置

集積回路装置が開示され、集積回路装置はNMOSゲート薄膜スタック(122)を覆う張力ストレス層(141)を有するデュアルストレスライナーNMOSデバイス(110)と、PMOSゲート薄膜スタック(123)を覆う圧縮ストレス層(142)を有するデュアルストレスライナーPMOSデバイス(111)と、張力ストレス層(141)とNMOSゲート薄膜スタック(124)との間に延在するストレス低減層(131a)を有する低減ストレスのデュアルストレスライナーNMOSデバイス(112)と、圧縮ストレス層(142)とPMOSゲート薄膜スタック(125)との間に延在するストレス低減層(131b)を有する低減ストレスのデュアルストレスライナーPMOSデバイス(113)とを含む。発明の実施形態において、追加の低減ストレスのデュアルストレスライナーNMOSデバイス(114)と低減ストレスのPMOSデバイス(115)とは、ストレス低減層(132a,132b)の厚みおよび/または材料特性を変更することによって形成される。  (もっと読む)

(もっと読む)

スピントランジスタ、このスピントランジスタを備えたリコンフィギャラブル論理回路および磁気メモリ

【課題】電子と正孔の相互作用による、磁化方向が略平行なときの電流IDPと、磁化方向が略反平行なときの電流IDAPとの差の絶対値の減少を抑制することを可能にする。

【解決手段】表面にn型の半導体領域が設けられた半導体基板10と、半導体領域上に離間して設けられたソース電極30aおよびドレイン電極30bであって、ドレイン電極は半導体領域上に設けられ半導体領域の半導体よりもバンドギャップが大きくかつ価電子帯端が半導体領域の半導体の価電子帯端よりも低いエネルギーを有するn型の第1半導体層31bと、第1半導体層上に設けられた第1強磁性層34bとを有し、ソース電極は半導体領域上に設けられた第2強磁性層34aを有する、ソース電極およびドレイン電極と、ソース電極とドレイン電極との間の半導体領域に設けられたゲート電極24と、を備え、第1および第2強磁性層のうちの一方は磁化方向が不変であり、他方は磁化方向が可変である。

(もっと読む)

半導体回路装置の設計方法

【課題】チップ面積の増大を抑制し、且つ、電源がオフ状態である領域から電源がオンである領域に不定信号が伝播されることを防止すること。

【解決手段】本発明では、第1電源分離領域の出力が第2電源分離領域の入力に接続されているときに、第1電源分離領域に供給される第1電源をオフする場合、第1電源分離領域の出力に最も近いリテンションフリップフロップを表す第1検索セルを検索し(S10、S11−Yes)、第1検索セルと第1電源分離領域の出力との間の第2検索セルを検索する(S13、S11−No)。この場合、第1検索セルの出力に供給される電源を、第1電源から、第1電源と同じ電圧であり、且つ、常にオンしている第2電源に置き換え(S16)、第2検索セルに供給される電源を第1電源から第2電源に置き換える(S17)。

(もっと読む)

半導体装置及び半導体装置の補償容量の配置方法

【課題】回路セル内の領域を有効活用して十分な補償容量を確保し、電源電圧の変動を確実に抑制し得る半導体装置等を提供する。

【解決手段】本発明の半導体装置は、第1の方向に並んで配置された複数の素子を含む回路セル2と、この回路セル2の第1の方向に隣接して配置され回路セル2の電源に接続可能な補償容量C1、C2を有する基本端セル1(1a)とを備えて構成される。補償容量C1、C2を構成する拡散層10、11は、回路セル2の所定領域(素子間接続領域R1)を第1の方向に沿って延伸形成されている。また、拡散層10、11の上部にはゲート配線16、17が延伸形成されている。本発明の構成により、回路セル2の素子間接続領域R1を有効に活用しつつ、補償容量のC1、C2の容量値を増加させて電源変動の変動を確実に抑えることが可能となる。

(もっと読む)

141 - 160 / 629

[ Back to top ]