Fターム[5F067AA00]の内容

IC用リードフレーム (9,412) | 目的、効果 (1,630)

Fターム[5F067AA00]の下位に属するFターム

小型化 (423)

積層化、素子の相互接続 (75)

放熱 (191)

耐湿性向上(樹脂との密着性向上) (155)

リードの抜け防止 (85)

樹脂との熱膨張差による応力の吸収 (55)

樹脂クラック防止 (42)

外部リード保護(モールド) (9)

バリ除去・バリ発生防止、金属バリ (120)

多ピン化 (73)

リードフレームの湾曲防止 (55)

リードの曲がり検出・修正 (14)

リードのプリント基板への取付け容易 (125)

半田ブリッジ形成防止 (21)

半田流れ防止 (21)

不要接触防止(ボンディングワイヤ、内部リードとの接触防止) (35)

検査(製造中の検査) (26)

時計用リードフレーム

Fターム[5F067AA00]に分類される特許

1 - 20 / 105

半導体装置

【課題】ワイヤボンディング不良の発生を抑制した半導体装置を提供する。

【解決手段】半導体チップと、半導体チップを搭載するダイパッドと、ダイパッド上に半導体装置に接着するためのダイボンド材と、ダイパッドの周縁部に形成された溝構造と、溝構造に連結され、半導体チップの下面からはみ出したダイボンド材を溜める液溜まり構造と、を備えた。

(もっと読む)

端子曲げ加工装置および半導体装置

【課題】表面を傷つけることなく、外部導出端子を90°折り曲げる。

【解決手段】半導体装置10に相対的に固定された側板100c1,100c2に対して押し下げ部材100dを下向きに移動させ、押し下げ部材100dの押し下げ面100d1aによって支持部材100b1の当接部100b1b3,100b1c3を押し下げ、姿勢を維持したまま、支持部材100b1および押し当て部材100a1を側板100c1,100c2のガイド溝100c1a,100c2aに平行に斜め下向きに移動させ、押し当て部材100a1の側面100a1bを、鉛直方向上向きに延びている外部導出端子10b1に当接させ、次いで、外部導出端子10b1が折れ曲がり始めると、押し当て部材100a1の橋絡面100a1cを外部導出端子10b1に当接させ、次いで、押し当て部材100a1の下面100a1aが外部導出端子10b1に当接する時に、外部導出端子10b1の折り曲げ角度が90°になる。

(もっと読む)

半導体装置

【課題】信号伝送速度を高速化しても信頼性が高く、かつ、汎用的なリードフレームを利用可能な半導体装置を提供する。

【解決手段】本発明に係る半導体装置1は、内側ワイヤボンディング20、内側ボンディング用端子100、配線110、外側ボンディング用端子120、外側ワイヤボンディング30を具備し、この順に、ボンディングパッド90からインナーリード60までを電気的に接続する信号伝送手段を有する。内側ボンディング用端子100、配線110、外側ボンディング用端子120は、絶縁性部材40上に形成されている。信号伝送手段は、ボンディングパッド90から前記アウターリード70の先端までの信号伝送路の距離が実質的に等しくなるように、配線110の配線長によって調整されている。

(もっと読む)

半導体装置

【課題】ノイズの影響を抑制することができる半導体装置を提供する。

【解決手段】モールド樹脂50を樹脂50aに磁性材料50bを混入して構成する領域を有しるものとする。または、隣接するリード30の間に配置されるモールド樹脂50を、樹脂50aに誘電性材料50cを混入して構成する。これによれば、半導体装置のインダクタンスまたは容量を大きくすることができ、共振周波数を低くすることができる。したがって、増幅されるノイズの周波数を低くすることができ、当該ノイズが増幅されたとしても半導体チップ20に対する影響を抑制することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】リードフレームへ導電性リボンや太線ワイヤなどの接続体をボンディングする際に、高い超音波出力を用いる。その際、インナーリードの超音波振動方向への振動を規制し、高品質で且つ信頼性が高いボンディングを実現できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】インナーリード7aを有するリードフレーム4と、リードフレーム4に搭載された、電極パッド3aを有する半導体素子2と、電極パッド3aとインナーリード7aとを接続する導電性の接続体8とを有し、インナーリード7aにおける、接続体8が接合される接合領域11の近傍に、凹部12を配置された半導体装置を提供する。

(もっと読む)

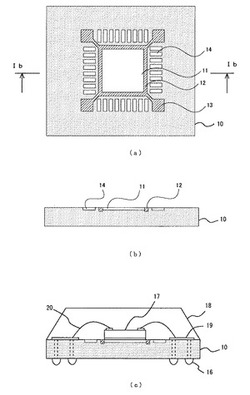

半導体パッケージ

【課題】取り扱いが容易な半導体パッケージを提供する。

【解決手段】半導体パッケージ1は、相互に離隔した第1及び第2のリードフレーム11,12と、第1及び第2のリードフレームの上方に設けられ、一方の端子14aが第1のリードフレーム11に接続され、他方の端子14bが第2のリードフレーム12に接続された半導体チップ14と、樹脂体17と、を備える。第1及び第2のリードフレームは、それぞれ、ベース部11a,12aと、ベース部から延出した複数本の吊ピン11b〜11e,12b〜12eと、を有する。ベース部は、第1及び第2のリードフレームにおける少なくとも相互に対向した部分に配置された薄板部と、薄板部よりも下方に突出した凸部11g,12gと、を有する。そして、薄板部の下面及び側面、凸部の側面、吊ピンの下面及び側面は樹脂体によって覆われており、凸部の下面及び吊ピンの先端面は樹脂体から露出している。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のワイヤ長の低減化を図る。

【解決手段】複数のリード2aのうちのリード2fは、第1の厚さを有する基端部2gと、基端部2gの長さよりも長く、かつ平面視において基端部2gからダイパッドに向かって屈曲するインナー部2eと、基端部2gからリード幅方向Hに迫り出した突出部2hとを有しており、インナー部2eは、平面視において前記ダイパッド側に位置する先端部2eaと、基端部2g及び突出部2hと連結する連結部2ebとを有するとともに、平面視において連結部2ebの幅M3は基端部2gの幅M1よりも大きく、複数のリード2fのそれぞれのインナー部2eにステージを接触させた状態でワイヤボンディングを行う。

(もっと読む)

リードフレームの製造方法

【課題】フォトマスクを高精度に位置合せすること。

【解決手段】リードフレームは、めっきを施した導電材料51に対してエッチング加工を行って形成される。めっきマスクを用いて導電材料51の1つの主面にリードフレームの所定部分(ダイパッド及びリード)に対応しためっき部53とアライメントマーク15,16を形成する。フォトマスク71のアライメントマーク74aとアライメントマーク15とを位置合し、導電材料51の1つの主面に形成したレジスト膜(感光性フィルム56)を露光してエッチングマスクを形成し、そのエッチングマスクを用いて導電材料51をエッチングする。

(もっと読む)

半導体装置

【課題】パッケージ応力に起因する回路部品の電気特性変動のバラツキによって出力信号が変動する内部回路について、パッケージ応力に起因する出力信号の変動を防止する。

【解決手段】半導体チップ5に形成された内部回路はその回路を構成する複数の回路部品の電気特性の変動のバラツキによって出力信号が変動するものである。チップタブ3の平面サイズは半導体チップ5の平面サイズよりも小さい。上方から見てチップタブ3の配置位置の全部が半導体チップ5の配置位置と重なっている。さらに、封止樹脂13に起因して半導体チップ5に加わる応力の大きさがチップタブ3上で均一になる位置関係でチップタブ3の周縁と上記半導体チップ5の周縁は間隔をもって配置されている。上記回路部品は半導体チップ5内部で上記チップタブ3上に配置されている。

(もっと読む)

樹脂封止型半導体装置

【課題】生産性の向上と信頼性の向上とを図ることを可能とするとともにコストの削減をも可能とする樹脂封止型半導体装置を提供する。

【解決手段】第1面に1個の電極が形成され、第2面に2個以上の電極が形成された半導体素子111と、半導体素子111を搭載する第1ダイパッド122及び第1リード124を有する第1リードフレーム120と、第1リードフレーム120とは隔離して配置される第2ダイパッド132及び第2リードを有する第2リードフレーム130と、接続部142及び第3リード1244有する第3リードフレーム140とを備える樹脂封止型半導体装置101であって、第2面に形成された電極のうちの1個の電極は、第1ダイパッド122に直接接続され、第2面に形成された他の電極は、第2ダイパッド132に直接接続され、第1面に形成された電極は、電気接続子150を介して第3リードフレーム140の接続部142に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】樹脂バリを容易に除去することができ、かつリードフレームの端子間の放電を抑制することができる半導体装置の製造方法を得る。

【解決手段】パッケージ外部領域5とパッケージ内部領域6を有するリードフレーム1を用いる。リードフレーム1の側面の上端にカエリ面7が設けられ、側面の上端近傍に破断面8が設けられている。パッケージ外部領域5においてリードフレーム1の側面の上端を面取り加工する。パッケージ内部領域6においてリードフレーム1上に半導体素子10を搭載してモールド樹脂12で封止する。面取り加工及び樹脂封止の後に、パッケージ外部領域5においてリードフレーム1の側面に設けられた樹脂バリ13を除去する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体装置の耐圧を確保することのできる技術を提供する。

【解決手段】封止体4は、第1リード1の第1インナー部1Aと、第1オフセット部1Cと、第1アウター部1Bの一部とを封止し、第2リード2の第2インナー部2Aと、第2オフセット部2Cと、第2アウター部2Bの一部とを封止する。さらに、第1アウター部1Bは、封止体4の下面から露出する第1裏面D11と、第1リード1の延在方向と直交する第1外端面D12と、前記第1オフセット部1Cと前記第1アウター部1Bとの境界に位置する第1内端面D13とを有し、第2アウター部2Bは、封止体4の下面から露出する第2裏面D21と、第2リード2の延在方向と直交する第2外端面D22と、第2オフセット部2Cと第2アウター部2Bとの境界に位置する第2内端面D23とを有する。

(もっと読む)

半導体装置

【課題】 縦型MOSFETのオン抵抗及びスイッチング損失の低減。

【解決手段】 封止体と、前記封止体内に位置する半導体チップと、前記封止体の内外に亘って延在する複数のリードと、前記半導体チップの電極と前記封止体内に位置するリードの内端を電気的に接続する導電性のワイヤとを有し、前記半導体チップには縦型電界効果トランジスタセルが並列接続状態で複数組み込まれ、半導体チップの表面にはゲート電極とソース電極が交互に並んでそれぞれ複数配置されるとともに、前記各電極に対応してリードが並び、前記各電極と前記対応した各リードは前記ワイヤによって接続されていることを特徴とする半導体装置。

(もっと読む)

半導体ダイオードパッケージ及びその製造方法

【課題】発光デバイスパッケージ及びその製造方法を改善することを目的とすること。

【解決手段】本発明の一態様は、キャビティが形成されたパッケージ本体と、前記キャビティの底面上の底部フレーム、並びに、前記底部フレームの一方の側面から延在する第1の側壁フレーム、及び、前記底部フレームの他方の側面から延在する第2の側壁フレームを有するリードフレームと、前記リードフレームの上に配置された発光ダイオードとを備え、発光ダイオードパッケージである。前記第1及び第2の側壁フレームの少なくとも一方は、前記底面に対する垂直軸を基準として15°から30°の範囲の角度で傾斜している。

(もっと読む)

ICカード用のリードフレーム及びその製造方法

【課題】 ICカード用のリードフレーム及びその製造方法に関し、新たな固定治具を要することなく、剛性の高いリードフレームを提供する。

【解決手段】 鉄ニッケル合金または銅を含むリードフレーム素材からなり、内部に開口部を有する複数の所定のパターンに耐熱テープを貼付し、前記耐熱テープの他方の面に接触端子パターンを貼付する。

(もっと読む)

電子部品材

【課題】Cu合金の代わりに使用でき、軽量化が図れると共に、原材料費の低減も図れる電子部品材を提供する。

【解決手段】電子部品材は、焼きなまし処理し、引張強度を200〜300MPaかつビッカース硬度Hvを65〜100にしたAl合金の基材10の表面に、Ni、Ni合金、Cu、Cu合金、Ag、Ag合金、Sn、Sn合金、Pd、Pd合金、Au、又はAu合金のいずれか1種又は2種以上で構成される第1のめっき層13を形成したものである。

(もっと読む)

半導体装置

【課題】接地電源用パッド数の増加や半導体チップの大面積化を伴うことなく、接地電源のインダクタンスを低化させてLSI電位変動を抑制することを目的とする。

【解決手段】ダイパッド3をLSI電位の外部端子として機能させ、LSI電位の供給をダイパッド3から樹脂基板4の接続ビア11bを介して行うことにより、LSI電位の電流経路が短縮されると共に電流経路の断面積を拡大することが可能となり、接地電源用パッド数の増加や半導体チップ2の大面積化を伴うことなく、接地電源のインダクタンスを低化させてLSI電位変動を抑制することができる。

(もっと読む)

リードピン付き配線基板

【課題】リフローはんだ付けによって配線基板に信頼性よく固定できる新規な構造のリードピンを提供する。

【解決手段】軸部12と、軸部12の先端側に設けられて、軸部12の径より大きな径をもち、外面全体が球状面からなる接続ヘッド部14とを有し、軸部12及び接続ヘッド部14が銅、銅合金、又はコバールから形成されるリードピン10と、ピン接続部S2を備えた配線基板20とを含み、接続ヘッド部14は、横方向の直径が縦方向の直径より長い楕円球形状からなり、リードピン10の接続ヘッド部14がはんだ層36を介して配線基板20のピン接続部S2に接続されており、リードピン10の接続ヘッド部14の径は、配線基板20のピン接続部S2の径の40乃至80%に設定される。

(もっと読む)

銅又は銅合金部材の製造方法とその部材並びに半導体パッケージ

【課題】本発明の目的は、表面粗さが低く、ロールスクラッチのない表面特性を有し、めっきの密着性に優れた銅又は銅合金部材の製造方法とその部材並びにこれをリードフレーム材として備える半導体パッケージを提供する。

【解決手段】本発明は、フィルムラッピング処理された算術平均粗さ(Ra)が0.02μm以上0.05μm未満である表面粗さを有するロールを用いて、圧下量を10〜50μmの範囲内で仕上げ圧延を行う銅又は銅合金部材の製造方法にあり、その製法によって得られ、材料表面に長さが50μm以上及び幅が3μm以上である突起状のロールスクラッチが存在しないこと、更に、材料表面の算術平均粗さ(Ra)が0.05μm以下及び最大高さ(Rz)が0.08μm以下である銅又は銅合金部材にある。

(もっと読む)

半導体装置用リードフレームとその製造方法

【課題】半導体装置用リードフレームとその製造方法において、複数のめっき層を積層する場合におけるめっき層同士の密着性を向上させ、半導体装置の製造工程におけるワイヤーボンド性の低下や実装の際の半田付け性の悪化を抑制するとともに、製造コストの効果的な削減を図る。

【解決手段】 導体基材20上に下地めっき層21を形成し、当該下地めっき層21の上に金属結合性を有する有機被膜22を介して最表めっき層23を積層することで、リードフレーム2a、2bを構成する。有機被膜22は、主鎖部B1の両末端に金属結合性の官能基A1、A1を持つ機能性有機分子11を自己組織化させた単分子膜として構成する。

(もっと読む)

1 - 20 / 105

[ Back to top ]