Fターム[5F083AD06]の内容

半導体メモリ (164,393) | DRAM (5,853) | 読出しトランジスタ (1,433) | 水平方向以外のチャネルを有するもの (541) | 突起状半導体柱の側面全体をゲート電極で覆うもの (130)

Fターム[5F083AD06]に分類される特許

1 - 20 / 130

半導体装置の製造方法

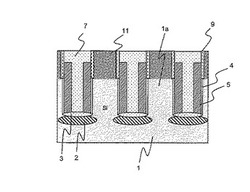

【課題】縦型トランジスタにおける上部拡散層の深さ方向のばらつきを低減することのできる半導体装置の製造方法を提供する。

【解決手段】本発明は表面が平坦なシリコン層からなる上部拡散層11を形成しようとするものであり、具体的には、ファセットを有するシリコン層を選択的に過剰成長させた後、層間絶縁膜7表面に形成されたシリコン層をCMPで擦り切ってシリコン層の表面を平坦化する。シリコン層の成長は、シリコン層を単結晶シリコンで選択的にエピタキシャル成長させる。この場合、ファセットが生じるので、最も成長が遅いファセットが層間絶縁膜表面より上方に位置するまで充分過剰に成長させる。

(もっと読む)

半導体装置の製造方法

【課題】縦型トランジスタのソース又はドレイン用の拡散層を形成するにあたって形成されるシリコン膜に表面凹凸を発生させない半導体装置の製造方法を提供する。

【解決手段】複数の半導体ピラーを形成する工程と、隣り合う前記半導体ピラーで挟まれた溝の側面を覆うように絶縁膜を形成する工程と、前記絶縁膜の前記溝の底部に近い領域に側面開口を形成する工程と、前記溝の内部を覆うようにシリコン膜からなる被覆膜を形成する工程と、前記被覆膜上に前記半導体ピラー内へ拡散させる不純物で構成された不純物層を形成する工程と、前記不純物を、前記側面開口を塞ぐように形成されている前記被覆膜を通して前記半導体ピラー内に熱拡散させてソース又はドレイン用の拡散層を形成する工程と、を含む。前記被覆膜の成膜温度を510℃より高く度550℃未満の範囲とすることにより、非晶質状態のシリコン膜を形成する。

(もっと読む)

半導体素子及びその形成方法

【課題】ビットラインを容易に形成することができ、ビットライン工程マージンを増加させ、さらに隣接したビットライン間のキャパシタンスを減少させる半導体素子及びその形成方法を提供する。

【解決手段】本発明に係る半導体素子は、半導体基板10で一方向に延長され、垂直チャンネル領域12b,14bを含む第1及び第2ピラー12,14と、第1及び第2ピラー12,14の内部で垂直チャンネル領域12b,14bの下部に位置する第1ビットライン22と、第1ビットライン22を含む第1ピラー12及び第2ピラー14の間に位置する絶縁膜32とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のトランジスタのシリコンピラー上部に活性領域を設ける際に、エピタキシャル成長により前記シリコンピラー上部に形成されるシリコン膜の高さが、前記トランジスタ毎にばらつくことを防ぎ、前記シリコン膜への導電型ドーパントの注入深さを均一にする半導体装置の製造方法を提供する。

【解決手段】基板の主面に柱状のシリコンピラーを形成するシリコンピラー形成工程と、前記シリコンピラーを覆うように第1の絶縁膜を形成する第1絶縁膜形成工程と、前記第1の絶縁膜を上面から除去し、前記シリコンピラー上部の上面及び側面を露出させる第1絶縁膜除去工程と、前記シリコンピラー上部の上面及び側面にエピタキシャル成長法によりシリコン膜を形成するシリコン膜形成工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】セルトランジスタが形成された第1領域と周辺回路トランジスタが形成された第2領域を有する半導体装置において、周辺回路トランジスタの上部拡散層のチャネル領域への導電型ドーパントの分布を抑制し、セルトランジスタと周辺回路トランジスタにおける駆動電流の閾値電圧依存性のばらつきを低減する半導体装置の製造方法を提供する。

【解決手段】基板を第1領域と第2領域に区分し、前記第2領域の前記基板上面を前記第1領域の前記基板上面より所定の掘り下げ量だけ掘り下げる工程と、前記第1領域に第1ピラーを、前記第2領域に前記第1ピラーよりも高さが前記掘り下げ量だけ低い第2ピラーを各々形成する工程と、前記第1及び第2ピラーの下部に第1拡散層を、上部に第2拡散層を各々形成する工程と、前記第1及び第2ピラーと前記第1拡散層の側面にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜側面にゲート電極を形成する工程とを有する。

(もっと読む)

補助電極構造を備えた立体型DRAM

【課題】補助電極構造を備えた立体型DRAMの提供。

【解決手段】本補助電極構造を備えた立体型DRAMは、基板(10)、該基板(10)上に形成された少なくとも一つのビット線(11)、該ビット線(11)上の成長領域(111)に形成された柱状体(20)、補助電極(40)、該基板(10)に平行で且つ該ビット線(11)に垂直なワード線(60)、該柱状体(20)に接続されたコンデンサ(70)を包含し、該ビット線(11)は該基板(10)にドーパントをドープし並びに拡散を実行して形成され、該補助電極(40)は該ビット線(11)の間隔領域(112)に設置され、並びに該柱状体(20)に隣接し、該ワード線(60)は該補助電極(40)と絶縁されて設置され、並びに該ビット線(11)と組み合わされて該コンデンサ(70)に電子データを入出力する。本発明は該補助電極(40)の設置により、該ビット線(11)の抵抗を制御できるようにすることで、該ビット線(11)の導電能力を向上する。

(もっと読む)

半導体装置

【課題】1T−DRAMにおいて、高いGIDL電流は、主にPN接合でのリーク電流によるものであり、データ保持時にリーク電流が発生する原因にもなり、DRAMにおける電荷保持時間を低下させている。

【解決手段】ドレイン拡散層のうちゲート電極とオーバーラップする部分を、不純物濃度の異なる2つの部分に分けている。これら2つの部分のうち、不純物濃度がより低い一方の部分では、ボディ部に隣接しており、電界が低減されるためリーク電流が抑制される。また、不純物濃度がより高い他方の部分では、ボディ部から絶縁されており、ゲート絶縁層との界面において比較的大きなトンネル効果が得られる。その結果、GIDL電流を増大しつつ、PN接合によるリーク電流を抑制し、データ保持時間を増大させることが可能となっている。

(もっと読む)

メモリ装置、及びメモリ装置の作製方法

【課題】可能な限り占有面積が削減され、データ保持期間の極めて長いメモリ装置を提供する。

【解決手段】メモリ装置内のメモリ素子のセルトランジスタとして、リーク電流の極めて小さいトランジスタを用いる。さらにメモリセルの占有面積を縮小するために、ビット線とワード線とが交差する領域に、当該トランジスタのソース及びドレインが縦方向に積層されるように形成すればよい。さらにキャパシタは、当該トランジスタの上方に積層すればよい。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体デバイスの製造方法

【課題】チャネル領域となる領域の直下だけに熱拡散によってビット線となる拡散層を形成することができる半導体デバイスの製造方法を提供する。

【解決手段】半導体基板の法線方向に複数の半導体ピラーを形成する工程、前記半導体ピラーで挟まれた溝の側面を覆うように絶縁膜を形成する工程、前記溝の内部全体を覆うように第1のポリシリコン膜を形成する工程、前記第1のポリシリコン膜上に前記半導体基板内へ拡散させる不純物で構成された不純物層を形成する工程、前記不純物層上に第2のポリシリコン膜を形成する工程、前記第2のポリシリコン膜上に前記不純物の外方拡散を防止する第1の拡散防止膜を形成する工程を経た後、前記不純物を前記溝の底部において前記半導体ピラー内に熱拡散させてビット線となる拡散層を形成する。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは、ビット線をキャパシタとセルトランジスタの間に形成するため、構造が複雑であったり、回路の特性を犠牲にしたりする必要があり、集積化の面で大きな障害となっている。

【解決手段】キャパシタの一方の電極をビット線に接続し、他方の電極をセルトランジスタのドレインに接続する。また、セルトランジスタのソースは、ソース線に接続される。この結果、例えば、スタック型キャパシタを採用する場合には、キャパシタの電極の一方をビット線の一部とすることができる。ソース線は、半導体基板上に形成された不純物領域や、ワード線に平行な配線を用いることができるので、構造が単純となる。

(もっと読む)

半導体記憶装置

【課題】SOI構造のDRAMの提供

【解決手段】

半導体基板1上に複数層の絶縁膜(2、3、4、5)が選択的に設けられ、絶縁膜5上より、絶縁膜5が設けられていない領域上に延在して選択的に半導体層(8、9、10)が設けられ、半導体層の一部9の全周囲にゲート絶縁膜16を介し、絶縁膜4上に包囲構造のゲート電極17が設けられ、ゲート電極に自己整合し、直下に空孔7を有する半導体層の一部10にドレイン領域(14、15)が、半導体層の一部8にソース領域(12、13)が設けられた構造のMIS電界効果トランジスタと、ソース領域12の側面に一部を接し、絶縁膜(3、5)中にトレンチが設けられ、トレンチの側面に電荷蓄積電極19が設けられ、電荷蓄積電極の側面及び上部にキャパシタ絶縁膜20を介してセルプレート電極21が設けられた構造のトレンチ型キャパシタと、により構成されたDRAM。

(もっと読む)

埋め込みビットラインを備えた半導体装置の製造方法

【課題】埋め込みビットラインの抵抗を減少させることができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板201に活性領域203を分離するトレンチ202をエッチングにより形成するステップと、活性領域203の何れか1つの側壁の一部を露出させた開口部207を有する絶縁膜205を形成するステップと、絶縁膜205上にトレンチ202を部分的に埋め込み、開口部207を埋め込むようにシリコン膜パターン208Aを形成するステップと、シリコン膜パターン208A上に金属膜209を形成するステップと、金属膜209及びシリコン膜パターン208Aを反応させて、埋め込みビットラインとなる金属シリサイド膜211を形成するステップとを含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】縦型トランジスタの特性を悪化させることなく縦型トランジスタの設置面積を削減できる高集積化に適した半導体装置およびその製造方法を提供する。

【解決手段】一定の間隔を空けて配置された複数のピラー30が備えられ、複数のピラー30が、縦型トランジスタTのチャネルとして機能する半導体層からなるチャネルピラー1と、不純物拡散層からなり、前記チャネルピラー1の下部に接続されて縦型トランジスタTの一方のソースドレインとして機能する下部拡散層4に電気的に接続された引き上げコンタクトプラグ2とを含む半導体装置とする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極断線の確率を下げる。

【解決手段】半導体装置1の製造方法は、シリコン基板2の主面に絶縁体ピラー6を形成する工程と、絶縁体ピラー6の側面に保護膜12を形成する工程と、シリコン基板2の主面にシリコンピラー4を形成する工程と、シリコンピラー4の側面にゲート絶縁膜10を形成する工程と、それぞれシリコンピラー4及び絶縁体ピラー6の側面を覆い、互いに接する第1及び第2のゲート電極11,13を形成する工程とを備える。本製造方法によれば、ダミーピラーとしての絶縁体ピラー6の側面に保護膜12を形成しているので、チャネル用のシリコンピラー4をトランジスタとして加工する際にダミーピラーが削られてしまうことが防止される。したがって、ゲート電極断線の確率を下げることが可能になる。

(もっと読む)

半導体装置

【課題】バイアス切替の前後でドレイン電流の大きさが変化しない縦型トランジスタを実現する。

【解決手段】半導体装置1は、第1の下部拡散層6A、第1の上部拡散層7A、及び第1のゲート電極9Aを有する第1の縦型トランジスタ4Aと、第2の下部拡散層6B、第2の上部拡散層7B、及び第2のゲート電極9Bを有する第2の縦型トランジスタ4Bと、第1及び第2のゲート電極9A,9Bに接続されるゲート配線と、第1の下部拡散層6A及び第2の上部拡散層7Bに接続される第1の配線W1と、第1の上部拡散層7A及び第2の下部拡散層6Bに接続される第2の配線W2とを備える。

(もっと読む)

半導体装置の製造方法

【課題】シリサイド層の成長に起因するゲート電極と半導体基板との間のショートの発生を抑制した上で、シリサイド層を厚く形成可能な半導体装置の製造方法を提供する。

【解決手段】ピラー26の側面にゲート絶縁膜27を介して、ゲート電極51、52を形成し、ピラー26の上端に上部不純物拡散領域36を形成し、上部不純物拡散領域36上に形成された層間絶縁膜39、68を貫通し、かつ上部不純物拡散領域36の上面を露出するシリンダ孔71を形成し、シリンダ孔71の底部に、上部不純物拡散領域36の上面を覆うと共に、シリンダ孔71の一部を埋め込むシリコン膜42を形成し、シリコン膜42の上面、シリコン膜42よりも上方に位置するシリンダ孔71の内面を覆うように下部電極57を形成すると共に、下部電極57を形成する際の熱により、シリコン膜42に含まれるSiと下部電極57に含まれる金属とを反応させてシリサイド層43を形成する。

(もっと読む)

半導体デバイス及びその製造方法

【課題】ゲート電極と上部導電層とのショートを防止した安定動作可能な縦型MOSトランジスタを有する半導体デバイスを提供する。

【解決手段】縦型MOSトランジスタを構成する半導体ピラー5Aは、第1の幅を有する上部5Aaと第2の幅を有する下部5Abを有し、上部5Aa側面は第2の絶縁膜6aと第3の絶縁膜6bで覆われ、下部5Abは側面から第2の絶縁膜6aまでゲート絶縁膜である第1の絶縁膜11Aで覆われており、ゲート電極13Aが第2及び第3の絶縁膜6により上部導電層18と絶縁されている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、溝内に残存する導電膜の高さばらつきを小さくすることで、半導体装置の特性のばらつきを低減可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】半導体基板13をエッチングして、幅W1とされた第1の溝部51を形成し、その後、第1の溝部51の下方に位置する半導体基板13をエッチングして、幅W1よりも狭い幅W2とされた第2の溝部52を形成することで、第1の溝部51、第2の溝部52、及び第1の溝部51の底面及び第2の溝部52の側面よりなる対向する一対の段差部54を有したビット線形成用溝を形成し、次いで、ビット線形成用溝15の内面を覆う絶縁膜16を介して、第2の溝部52を埋め込み、かつ第1の溝部51を埋め込まない厚さとされた第1の導電膜56を成膜し、その後、第1の導電膜56をエッチバックすることで、第2の溝部52の一部に第1の導電膜56を残存させる。

(もっと読む)

半導体装置

【課題】リーク電流が発生しにくく、低消費電力化に好適な半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体基板12内に埋め込まれてX方向に並列して延在する複数のビット線BLと、X方向と交差するY方向に延在するワード線と、ビット線BLと前記第2配線との交点に設けられたメモリセルMと、複数のビット線BLのうち最外列のビット線BLの外側に設けられ、X方向に延在してビット線BLと並走するダミービット線DBLとを含み、ダミービット線DBLが、半導体基板12に供給される電位と同じ電位が供給されるダミービット線(第1ダミー配線)DBL<0>、DBL<1>、DBL<2>を含むことを特徴とする。

(もっと読む)

1 - 20 / 130

[ Back to top ]