Fターム[5F083AD49]の内容

Fターム[5F083AD49]に分類される特許

41 - 60 / 552

半導体装置

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供と、さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図る。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

半導体装置の作製方法

【課題】高いオン特性を有する酸化物半導体を用いたトランジスタを提供する。高速応答及び高速駆動の可能なトランジスタを有する高性能の半導体装置を提供する。

【解決手段】チャネル形成領域を含む酸化物半導体膜を有するトランジスタの作製工程において、該酸化物半導体膜に、金属元素を含む膜と接した状態で加熱処理することにより導入された金属元素と、注入法により該金属元素を含む膜を通過して導入されたドーパントとを含む低抵抗領域を形成する。低抵抗領域はチャネル長方向においてチャネル形成領域を挟んで形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】容量絶縁膜の絶縁性の劣化が生じにくく、かつ容量プレート電極の厚みが薄い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、互いに異なる平面面積を持つメモリセル部と補償容量部とを単一の基板上に備える。メモリセル部と補償容量部とは、同一構成の容量プレート電極を含む。容量プレート電極は、ボロンドープシリコンゲルマニウム膜と金属膜とを含む積層構造を有している。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

半導体装置

【課題】酸化物半導体のようなバンドギャップが大きな半導体を用いたメモリ装置の保持特性を高める。

【解決手段】ビット線にビット線制御トランジスタを直列に挿入し、そのゲートの最低電位は十分な負の値となるようにする。ビット線制御トランジスタのゲートは電池等に接続するビット線制御回路に接続される。ビット線の最低電位はワード線の最低電位よりも高くなるようにする。外部からの電源が切れた際には、ビット線はビット線制御トランジスタによって遮断され、ビット線に蓄積された電荷が流出することが十分に抑制される。この際、セルトランジスタのゲートの電位は0Vであり、一方で、そのソースやドレイン(ビット線)の電位は、ゲートよりも十分に高いので、セルトランジスタは十分なオフ状態であり、データを保持できる。あるいは外部電源遮断時にワード線の電位を十分な負の電位とできるような回路を設けてもよい。

(もっと読む)

半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供する

ことを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウ

ム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて

、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化

物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以

下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有

し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でス

パッタリングを行う。

(もっと読む)

半導体装置

【課題】電源電圧の供給を停止しても、論理回路部間の接続関係、又は各論理回路部内の回路構成を維持できる半導体装置を提供する。また、論理回路部間の接続関係の変更、又は各論理回路部内の回路構成の変更を高速で行うことができる半導体装置を提供する。

【解決手段】再構成可能な回路において、回路構成や接続関係等のデータを記憶する半導体素子に酸化物半導体を用いる。特に、半導体素子のチャネル形成領域に、酸化物半導体が用いられている。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の占有面積を実質的に減少させる。

【解決手段】半導体装置は、第1の方向及びそれと交差する第2の方向に沿って半導体基板上に配列形成された複数の第1の接続領域と、複数の第1の接続領域を第1の方向に沿った列ごとに電気的に接続する複数の配線とを含む。複数の配線は、第2の方向に隣り合う2つの配線が互いに異なる配線層に配置され、かつ平面視において一部が重なってハニカム状に見えるように屈曲させてある。

(もっと読む)

キャパシタ構造の形成方法及びこれに用いられるシリコンエッチング液

【課題】半導体基板に凹凸形状をなすよう、アモルファスシリコン又は多結晶シリコンを的確かつ効率よく除去することができ、しかもそのエッチングが行われる条件下において長時間活性が維持されるシリコンエッチング液及びこれを用いたキャパシタ構造の形成方法を提供する。

【解決手段】アンモニアと、ヒドロキシルアミン化合物、塩基性有機化合物、及び金属含有塩基性化合物からなる群から選ばれる少なくとも1つの特定塩基性化合物とを組み合わせて含むシリコンエッチング液を、多結晶シリコン膜またはアモルファスシリコン膜6に適用して、該多結晶シリコン膜またはアモルファスシリコン膜の少なくとも一部を除去することにより、キャパシタとなる凹凸形状を形成するキャパシタ構造10の形成方法。

(もっと読む)

半導体装置の製造方法

【課題】非晶質炭素膜を用いて形成する電極のアスペクト比を増大させる。

【解決手段】半導体装置の製造方法は、半導体基板上に第1非晶質炭素膜を形成し、周辺回路領域の第1非晶質炭素膜を除去してメモリセル領域の第1非晶質炭素膜を第2非晶質炭素膜とし、第2非晶質炭素膜を覆う第1シリコン酸化膜を基板全面に形成し、第2非晶質炭素膜上の第1シリコン酸化膜を除去して周辺回路領域の第1シリコン酸化膜を第2シリコン酸化膜とし、第2非晶質炭素膜と第2シリコン酸化膜を覆う第1絶縁膜を形成し、第1絶縁膜に第1開口を形成し、第1開口を埋め込む第2絶縁膜を形成し、第2絶縁膜に第2開口を形成し、第2開口と第1開口が重なる位置に露出する第2非晶質炭素膜にホールを形成し、ホール内に下部電極を形成し、第2絶縁膜を除去して第1開口内に第2非晶質炭素膜を露出させ、露出した第2非晶質炭素膜を全て除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】第2の部分の寄生容量を低下させることにより、半導体装置の特性を向上させる。

【解決手段】MISトランジスタは、半導体基板上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられ、第1の幅W1を有する第1の部分と第2の幅W2を有する第2の部分とを有するゲート電極を有する。第2の部分の側壁上には、酸化シリコン膜が設けられている。第2の部分に接するゲート絶縁膜は、第1の部分に接するゲート絶縁膜よりも厚くなっている。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも

制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワ

イドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジス

タのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわた

って情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込

みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミス

を防ぐことが可能である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】メモリ・ロジック混載型の半導体装置の高性能化を可能にする技術を提供する。

【解決手段】ストッパ膜17は、ストッパ膜13及び層間絶縁膜14から成る絶縁層上に形成されている。コンタクトプラグ16,65,66のそれぞれは、その上面がストッパ膜17から露出するように、ソース・ドレイン領域9,59とそれぞれ電気的に接続されてストッパ膜13、層間絶縁膜14及びストッパ膜17に設けられている。絶縁層20は、ストッパ膜17及びコンタクトプラグ16,65,66の上に設けられている。キャパシタ82の下部電極は、メモリ形成領域において、コンタクトプラグ66の上面とストッパ膜17の上面とに接触するように絶縁層20内に設けられている。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

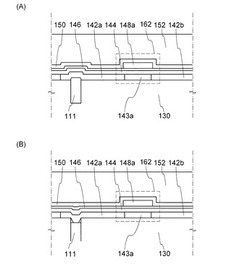

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】信号処理回路は、電源電圧が選択的に供給され、第1の高電源電位が選択的に与えられる第1のノードを有する回路と、第1のノードの電位を保持する不揮発性の記憶回路とを有する。不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなる第2のノードとを有する。トランジスタはエンハンスメント型のnチャネル型のトランジスタである。トランジスタのゲートには、第2の高電源電位または接地電位が入力される。電源電圧が供給されないとき、トランジスタはゲートに接地電位が入力されてオフ状態を維持する。第2の高電源電位は、第1の高電源電位よりも高い。

(もっと読む)

メモリ装置

【課題】メモリセルの占有面積が小さいメモリ装置、また、メモリセルの占有面積が小さく、データ保持期間の極めて長いメモリ装置を提供する。

【解決手段】ビット線と、容量素子と、該ビット線上に設けられた溝部を有する第1の絶縁層と、一部が該溝部の底部で該ビット線と電気的に接続し、他の一部が該第1の絶縁層の上面で該容量素子の一方の電極と電気的に接する半導体層と、該半導体層と接する第2の絶縁層と、該第2の絶縁層と接するワード線と、を有する構成のメモリ装置とする。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極用溝18の底部18cから活性領域の一部が突き出すように形成されたフィン部15と、ゲート電極用溝18及びフィン部15の表面を覆うゲート絶縁膜21と、ゲート電極用溝18の下部に埋め込まれ、ゲート絶縁膜21を介してフィン部15を跨ぐように形成されたゲート電極22と、第1の不純物拡散領域28と、第2の不純物拡散領域29と、フィン部15の表面に設けられた準位形成領域30と、を備える半導体装置10を選択する。

(もっと読む)

41 - 60 / 552

[ Back to top ]