Fターム[5F083AD49]の内容

Fターム[5F083AD49]に分類される特許

61 - 80 / 552

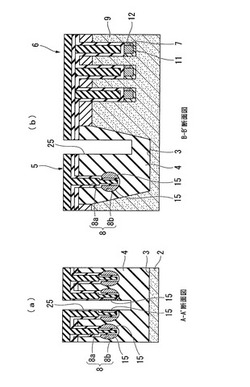

半導体装置及びその製造方法

【課題】コンタクトホールに埋め込まれたコンタクトプラグが埋め込み配線と非導通になることを防止した半導体装置及びその製造方法を提供する。

【解決手段】ゲート絶縁膜を介してピラー部9の側面と対向する位置において幅広となる形状を有する第1の溝部8を形成し、この第1の溝部8の幅広となる部分8bに埋め込まれた状態で第1の埋め込み配線15を形成し、複数のピラー部9が並ぶ領域よりも外側の領域において、第1の溝部8の間に位置すると共に、第1の溝部8の幅広となる部分8bに埋め込まれた第1の埋め込み配線15に至る深さで第1のコンタクトホール25を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート電極用溝18の底部に設けられた第1の不純物拡散領域27と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆うように、半導体基板13に設けられた第2の不純物拡散領域28と、少なくとも第2の側面18bに配置されたゲート絶縁膜21を覆うように半導体基板13に設けられ、第1の不純物拡散領域27と接合された第3の不純物拡散領域29と、を有する。

(もっと読む)

ルチル結晶構造を備えた酸化チタン膜の製造方法

【課題】高温のアニールを必要とせずに、誘電率の高いルチル結晶構造の酸化チタン膜を形成する。

【解決手段】非晶質の酸化ジルコニウム膜上に、チタンプリカーサとしてメチルシクロペンタジエニルトリスジメチルアミノチタンを用いてALD法により非晶質の酸化チタン膜を形成し、300℃以上の温度でアニールして結晶化することでルチル結晶構造を有する酸化チタン膜が得られる。

(もっと読む)

二重ゲート電極構造を含む半導体装置及びその製造方法

【課題】漏洩電流発生を最小化すると同時にオン電流(On current)を増加させ得る二重ゲート電極構造を含む半導体装置及びその製造方法が提供される。

【解決手段】本発明による半導体装置は、基板に配置されるゲート電極と、前記ゲート電極の両端に各々隣接するように前記基板に配置される第1不純物注入領域及び第2不純物注入領域と、前記第1不純物注入領域と前記第2不純物注入領域との間に配置されるチャンネル領域を含み、前記ゲート電極は前記第1不純物注入領域に隣接する第1サブゲート電極と前記第2不純物注入領域に隣接する第2サブゲート電極と、を含み、前記第1サブゲート電極と前記第2サブゲート電極とは前記チャンネル領域の上に配置される。この半導体装置では1つのチャンネル領域が2つのサブゲートによって独立的に制御されて漏洩電流発生を最小化できる。

(もっと読む)

半導体装置及びその製造方法

【課題】ビット線コンタクトの抵抗が低減された半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、第1の方向に延在する半導体基板1に複数の第1の溝3aと該溝よりも幅狭でかつ平行に延在する複数の第2の溝3bとを第1の方向に直交する第2の方向に交互に離間して有し、第1の溝内にワード線7aが形成され、第2の溝には素子分離用導電層7cが埋設され、第1の溝の底面3Aから下方の領域に延在する下部拡散領域5を有し、ワード線7aは第1の溝内の第2の方向に平行でかつ対向する側壁のそれぞれに第2の絶縁膜6a、6bを介して形成されてなると共に第3の絶縁膜8で覆われており、素子分離用導電層7cはワード線と同じ材料でなり、底面3Aに下部拡散領域5に導通すると共に第3の絶縁膜8によってワード線7aと絶縁された半導体選択成長層10を備え、その層10上にビット線コンタクトを備えている、ことを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜(第1の結晶性酸化物半導体膜ともいう)を形成し、該酸化物半導体膜に酸素を導入して少なくとも一部を非晶質化し酸素を過剰に含む非晶質酸化物半導体膜を形成する。該非晶質酸化物半導体膜上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体膜の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜(第2の結晶性酸化物半導体膜ともいう)を形成する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル抵抗を減少させてオン電流を増加させることが可能で、各トランジスタを独立して安定して動作させることの可能な半導体装置を提供する。

【解決手段】ゲート電極用溝18の底部18cから突き出すように形成されたフィン部15と、ゲート電極用溝18及びフィン部15の表面を覆うゲート絶縁膜21と、ゲート電極用溝18の下部に埋め込まれ、ゲート絶縁膜21を介してフィン部15を跨ぐように形成されたゲート電極22と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆う第1の不純物拡散領域28と、第2の側面18bに配置されたゲート絶縁膜21の下端部以外の部分を覆う第2の不純物拡散領域29とを備え、ゲート電極用溝18の深さが半導体基板13の表層13aから150〜200nmであり、ゲート電極用溝18の底部18cからフィン部15の上部15aまでの高さが10〜40nmである。

(もっと読む)

半導体装置

【課題】微細化が可能であるメモリセル構造を備える半導体装置を提供する。

【解決手段】ワード線と、ビット線と、電源ノードと、ビット線と電源ノードとの間にPN結合を成す第1及び第2の領域並びに第2の領域とPN結合を成す第3の領域を少なくとも有するメモリ素子と、メモリ素子の第2の領域とは独立して設けられてメモリ素子の第2の領域と電気的に接続された第1の電極及び前記ワード線に接続された第2の電極を有するキャパシタと、を備える。

(もっと読む)

半導体デバイス及びその製造方法

【課題】エッチング選択比の高い非晶質炭素膜を用いたシリンダ型キャパシタを有する半導体デバイスでは、非晶質炭素膜を除去する際に、キャパシタの下部電極に変形が生じやすい。

【解決手段】非晶質炭素膜及び層間絶縁膜をメモリセル領域及び周辺回路領域にそれぞれ形成し、非晶質炭素膜及び層間絶縁膜上に絶縁膜を形成し、非晶質炭素膜上のキャパシタに対応した部分における絶縁膜を除去して、キャパシタの下部電極を両側から支持すると共に、メモリセル領域から周辺回路領域まで連続的に覆う絶縁膜パターンを形成する。続いて、非晶質炭素膜を用いたキャパシタを形成した後、絶縁膜パターン下部の非晶質炭素膜を除去する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】、メモリセルエリアの総面積を低減できるという積層構造のメリットを維持しつつ、セルキャパシタの容量に余裕を持たせる。

【解決手段】半導体記憶装置1は、半導体基板と、半導体基板の表面に配置された複数のセルトランジスタT1−1〜9及びT2−1〜9と、それぞれセルトランジスタT1−1〜9及びT2−1〜9に対応し、これらが配置された半導体基板の表面内の領域Cと平面的に見て重複する領域に設けられる複数のセルキャパシタC1−1〜9及びC2−1〜9とを備え、セルキャパシタC1−1〜9及びC2−1〜9は、平面的に見て互いに重複する領域に形成される。

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

半導体装置

【課題】キャパシタの配列におけるデッドスペースをなるべくなくし、個々のキャパシタの形状をなるべく拡大した半導体装置を提供する。

【解決手段】半導体装置は、互いに隣接して平行に線状に延びる第1および第2トランスファーゲート2と、これらの間の間隙に配列され、それぞれ上方に延びる棒状の導電体からなる第1および第2ストレージノードコンタクト9と、第1の電極と第2の電極とが絶縁膜を介して対向配置されてなる第1キャパシタ14と、第3の電極と第4の電極とが絶縁膜を介して対向配置されてなる第2キャパシタ14とを備え、平面視において、第1の電極の第1トランスファーゲート側の一部のみに第1ストレージノードコンタクト9の上面が接続され、第3の電極の第2トランスファーゲート側の一部のみに第2ストレージノードコンタクト9の上面が接続されている。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】電気的特性の安定した酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供すること。また、結晶性の高い酸化物半導体膜を用いることにより、移動度の向上した半導体装置を提供すること。

【解決手段】表面粗さの低減された絶縁膜上に接して、結晶性を有する酸化物半導体膜を形成することにより、電気的特性の安定した酸化物半導体膜を形成することができる。これにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することができる。さらに、移動度の向上した半導体装置を提供することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、接合リーク電流を低減可能で、かつトランジスタの信頼性を向上させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート電極61よりも上方に配置されたゲート絶縁膜21、及びゲート電極61の上面61aを覆う水素含有絶縁膜62と、水素含有絶縁膜62を介して、ゲート電極用溝17の上部17Bを埋め込むフッ素含有絶縁膜63と、を備え、ゲート絶縁膜21と接触する第1及び第2の不純物拡散領域65,66の面に、半導体基板13に含まれるシリコンと水素含有絶縁膜62に含まれる水素とが結合したSi−H結合、及び半導体基板13に含まれるシリコンとフッ素含有絶縁膜63に含まれるフッ素とが結合したSi−F結合を有する。

(もっと読む)

半導体装置の製造方法

【課題】サポート膜で保持されたシリンダ型電極を有するキャパシタを形成する際に、シリンダホール形成時にデフォーカスの発生したウエハエッジ部において、シリンダ型電極を形成する際の型材となるコア絶縁膜を除去すると、パターンとびが発生する。

【解決手段】コア絶縁膜26を除去するために形成するサポート膜27の開口部をデフォーカスの発生したウエハエッジ部では形成せず、好ましくは通常露光部のマット幅Maよりも大きなマット幅Mbとなるように形成し、ウエハエッジ部のサポート膜27下にコア絶縁膜26が残るようにする。

(もっと読む)

集積回路とその方法

【課題】標準/低温処理技術と適合しキャパシタンスの密度を向上させる多層構造で使用されるCMPと適合性を有するキャパシタ構造を提供する。

【解決手段】キャパシタ構造体は、集積回路の誘電体層の開口101内に形成される。下部電極層102は、開口101の側面表面の少なくとも一部の上にのびるが、誘電体層405の上部表面までにはのびていない。誘電体材料層405が、この下部電極102の上と、集積回路誘電体層203の上部表面の上に配置される。最後に上部電極層406が、この誘電体材料層405の上に形成される。上部電極層406と下部電極層102のオーバーラップは存在せず、平面化プロセスの間発生することのある短絡の問題を回避できる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の作製方法

【課題】高度に集積化したDRAMを提供する。

【解決手段】第1絶縁体101上にビット線102b、ビット線102b上に第2絶縁体103、第2絶縁体103上にストライプ状の第3絶縁体106a乃至106c等を形成し、第3絶縁体106bを覆って、半導体領域109bとゲート絶縁体110を形成する。ビット線102bと半導体領域109bは第1のコンタクトプラグ105a、105bで接続される。その後、導電性膜を形成し、これを異方性エッチングすることで、第3絶縁体106a乃至106cの側面にワード線111a乃至111dを形成し、第3絶縁体106bの頂部にキャパシタへ接続するための第2コンタクトプラグ115bを形成する。ワード線111b、111cを同期させることで、キャパシタに電荷を出入りさせる。このような構造でメモリセルの面積を4F2とできる。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化した半導体集積回路において用いられるキャパシタを提供する。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

(もっと読む)

61 - 80 / 552

[ Back to top ]