Fターム[5F083AD49]の内容

Fターム[5F083AD49]に分類される特許

81 - 100 / 552

キャパシタおよび半導体装置

【課題】微細化した半導体集積回路において用いられるキャパシタを提供する。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

(もっと読む)

キャパシタ、半導体装置及びそれらの製造方法

【課題】高い比誘電率を有する容量絶縁膜を使用して、静電容量を大きくし、しかもリーク電流を低減する。

【解決手段】容量絶縁膜として、c軸配向した結晶酸化ニオブを用い、特に成膜時の酸素含有量を、例えば、スパッタガスにおける酸素ガス比を調整することで制御して、a軸配向ピークを示さず、c軸配向ピークが優先した膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】活性領域とビット線コンタクトとの間の接触面積が大きく、コンタクト抵抗の低下が図られた半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、基板1に形成された第1の方向に延在する第1の溝4と、第1の溝4の下部を埋めこんで形成された第2の絶縁層6と、基板1に形成された第1の方向に直交する第2の方向に延在する複数の第2の溝と、第2の溝の下部を埋めこんで第2の溝内に形成されたワード線と、第1の溝4と第2の溝とによって基板1内に区画して形成され、基板1に垂直に立設すると共に、上部に拡散領域23aを有する半導体ピラー1dと、第1の方向に並ぶ所定数ごとの半導体ピラー1dにその上部の側面を介して拡散領域23aに接続するビット線コンタクト22aと、ビット線コンタクト22aに接続するビット線26と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離用ゲート電極のみのしきい値電圧を高くすることができ、素子分離用ゲート電極の底部にチャネルが形成されない半導体装置を提供する。

【解決手段】半導体基板1に形成された複数の活性領域と、これら活性領域同士を区画する素子分離領域と、活性領域内を複数の素子領域に区画する第1素子分離用トレンチ32Aと、隣接する第1素子分離用トレンチ32A間に設けられ、第1素子分離用トレンチ32Aの深さよりも浅く形成されたゲートトレンチ31Aと、絶縁膜25を介して第1素子分離用トレンチ32A内に形成された素子分離用電極32と、ゲート絶縁膜26Aを介してゲートトレンチ31A内に形成されたゲート電極31と、を具備してなり、素子分離用電極32底部に成膜されている絶縁膜25の膜厚が、ゲート電極31の底部に成膜されているゲート絶縁膜26Aの膜厚よりも厚いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】チタン酸ストロンチウム膜を容量絶縁膜として用いたキャパシタにおいて、静電容量が大きく、リーク電流が小さいキャパシタを形成する。

【解決手段】半導体装置の製造方法は、下部電極を形成後、下部電極上に中間窒化チタン膜及び非晶質チタン酸ストロンチウム膜が互いに接するように積層された積層膜を形成する。次に、第1の熱処理を行うことにより、中間窒化チタン膜及び非晶質チタン酸ストロンチウム膜を結晶質チタン酸ストロンチウム膜に変換する。次に、結晶質チタン酸ストロンチウム膜上に上部電極を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】論理回路の動作特性に優れた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、多層配線層と、第1能動素子3a、容量素子19および周辺回路を有する記憶回路200と、第2能動素子3bを有する論理回路100と、記憶回路領域200に形成されており、能動素子3aと容量素子19とを電気的に接続する容量コンタクト13cと、論理回路領域100に形成されており、能動素子3bと第1配線8aとを電気的に接続する接続コンタクト13aと、を備え、第1配線8aは、容量素子19が埋め込まれた配線層のうち最下層の配線層の層間絶縁膜7aに位置しており、接続コンタクト13aは、容量コンタクト13cと同一層に設けられており、第1配線8aと接続コンタクト13aは、デュアルダマシン構造を有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の容量の増大が実現される半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、半導体基板1内の記憶回路領域に形成されており、多層配線層内に設けられた凹部40内に埋め込まれた少なくとも1以上の容量素子19および周辺回路を有する記憶回路200と、平面視において、半導体基板1内の記憶回路領域とは異なる領域である論理回路領域に形成された論理回路100と、当該凹部40内において、下部電極14、容量絶縁膜15、及び上部電極16から構成される前記容量素子19上に積層している上部接続配線18と、容量素子19が埋め込まれている配線層のうち最上層に設けられた論理回路100を構成する配線8bの上面に接するように設けられたキャップ層6cと、を備え、上部接続配線18の上面30とキャップ膜6cの上面34とが、同一面を構成している。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、半導体装置の歩留まりを向上可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】アンモニア水を用いた湿式エッチングにより、エッチングマスク形成用溝の側面を洗浄することで、下部電極及びエッチングマスクの母材となる下部電極形成用金属膜を成膜する前に、異方性ドライエッチング時にエッチングマスク形成用溝の側面に付着したポリマーを除去し、次いで、エッチングマスク形成用溝に、下部電極形成用金属膜を成膜することでエッチングマスクを形成し、その後、湿式エッチングにより、エッチングマスクをマスクとして、メモリセル領域に形成された第4の層間絶縁膜を選択的に除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコンプラグと上層の導体プラグとの界面に十分な膜厚の金属シリサイド層を形成してコンタクト抵抗の低減を図る。

【解決手段】多結晶シリコンプラグを形成した後、多結晶シリコンプラグの表面からゲルマニウムイオン注入を実施してゲルマニウム含有多結晶シリコン16Gとし、その後、シリサイド化可能な金属膜を成膜して金属シリサイド層19を形成し、金属シリサイド19上に導体膜(バリア膜20、W膜21)を形成する。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

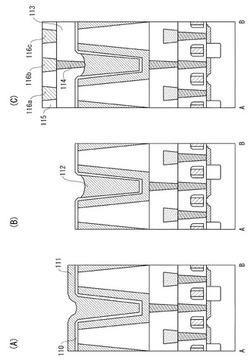

半導体記憶装置の製造方法

【課題】製造が容易なNAND型半導体記憶装置の製造方法を提供する。

【解決手段】製造方法は、基板101上に第1絶縁膜105及び第2絶縁膜106を交互に積層して積層体110を形成する工程と、第1絶縁膜105及び第2絶縁膜106の積層方向に延び、積層体110を貫通する貫通孔114を形成する工程と、貫通孔114の内面上に、MONOS116を構成するブロック絶縁膜、チャージトラップ膜及びトンネル誘電体膜の少なくとも一部を形成する工程と、トンネル誘電体膜上にチャネル半導体117を形成する工程と、積層体110にトレンチ121を形成する工程と、トレンチ121を介してエッチングを施すことにより、第2絶縁膜106を除去する工程と、第2絶縁膜106を除去した後の空間内に導電材料を埋め込む工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】DRAMの微細化及び高集積化により、プロセス低温化が進み、400〜500℃熱処理による基板内の酸素ドナー化による電子発生量が多くなってきた。そのため、基板深くに形成されるウェル同士の分離耐圧が厳しくなり、デバイス劣化を引き起こしてしまう。

【解決手段】P型半導体基板11の表面から0.2〜1μmの範囲の深さに2E+17atom/cm3以上のピーク濃度を有するNウェル層12の下方に、P型半導体基板11中に発生するキャリア電子濃度より高濃度のP型不純物を含有する空乏層拡大防止層17を有する半導体装置。

(もっと読む)

半導体装置の製造方法及びハードマスクの形成方法

【課題】アモルファスカーボン膜のパターン寸法ばらつきが低減した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に下地膜を形成する工程と、下地膜上にアモルファスカーボン膜を成膜する工程と、アモルファスカーボン膜のパターンを形成する工程と、アモルファスカーボン膜をマスクにして下地膜をエッチングする工程を有する。アモルファスカーボン膜は、アモルファスカーボン膜の表面から下地膜に接する面に向かってその厚み方向を進むにつれて、アモルファスカーボン膜の膜密度を小さくする。

(もっと読む)

半導体装置及びその製造方法

【課題】低リーク電流、高容量の誘電体膜上に形成する窒化チタン電極の薄膜化を抑制する。

【解決手段】下部電極表面に形成された結晶質酸化ジルコニウムを含む誘電体膜と、誘電体膜表面に形成された窒化チタンを含む上部電極とで構成されるキャパシタを含む半導体装置であって、誘電体膜は、前記上部電極を構成する窒化チタンとの界面に非晶質膜を含む。

(もっと読む)

誘電体膜の形成方法、及びこれを用いる半導体素子のキャパシタの形成方法

【課題】誘電特性及び漏れ電流特性を向上させることのできる半導体素子の誘電体膜の形成方法及びキャパシタの形成方法を提供する。

【解決手段】誘電体膜は、原子層堆積法により、ウェーハ上に酸化ジルコニウム(ZrO2)及び酸化アルミニウム(Al2O3)で構成された誘電体膜を形成する方法であって、チャンバー内に、1つのZrと1つのAl原子とが1つの分子を構成しているソースガスを注入し、ウェーハ上に、ZrO2とAl2O3とからなる[ZrO2]x[Al2O3]y(ここで、x及びyは正数である)膜を形成するステップを繰り返すことにより、ZrO2とAl2O3とで構成された厚さ30Å〜500Åの誘電体膜を形成する。

(もっと読む)

半導体デバイスの製造方法および基板処理装置

【課題】TiN膜の上部に形成するTiO膜の少なくとも一部の結晶構造をブルッカイト型構造又はルチル型構造とし、TiO膜の誘電率を高める。

【解決手段】ジルコニウム酸化膜の膜厚を制御することにより、ジルコニウム酸化膜の少なくとも一部の結晶構造を立方晶系構造又は正方晶系構造とし、これにより、チタン酸化膜の少なくとも一部の結晶構造をブルッカイト型構造又はルチル型構造とする。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAMセルとロジックを混載したLSIデバイスにおけるアスペクト比の大きいコンタクト構造において、素子分離絶縁膜および不純物拡散層のオーバエッチングを抑制して、接合リークを抑制することを課題とする。

【解決手段】周辺MOSトランジスタを覆う第1エッチングストッパ層121と、DRAMメモリセルのキャパシタ部上層に第2エッチングストッパ層122が形成され、周辺MOSトランジスタの不純物拡散層113は、第1、第2エッチングストッパ層121、122を貫通する電極層131により、上記キャパシタ部上層に形成された金属配線層と接続され、不純物拡散層113の少なくとも一つは素子分離絶縁膜102の境界上に電極層131を接続し、素子分離絶縁膜102上に形成された電極層131の底部の不純物拡散層113表面からの深さ寸法は、不純物拡散層113の接合深さ寸法もより短く形成されたものである。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】シリンダ型下部電極の剥がれ落ちを防止する、半導体装置の製造方法を提供する。

【解決手段】複数の第1の開口を有するコア絶縁膜を半導体基板上に形成し、複数の第1の開口の側面を導電膜で覆う、シリンダ状の複数の下部電極を形成し、少なくとも複数の下部電極間のコア絶縁膜の上面を覆うサポート膜を形成し、サポート膜を用いて少なくとも複数の下部電極が形成される領域の外側を除去したマスク膜を形成し、マスク膜を形成した後、複数の下部電極間の一部にコア絶縁膜が残るように、コア絶縁膜に対して等方性エッチングを行うものである。

(もっと読む)

SOI型トランジスタ

【課題】DRAMメモリアレイに用いられるセミコンダクタ・オン・インシュレータ型トランジスタを提供する。

【解決手段】SOI型のトランジスタは、半導体物質層60(SOI層)と、この半導体物質層60の内部を通って走るゲート線65a,65b,66cと、このゲート線65a,65b,66cに沿ってソース拡散領域70a、70b、70cよりも遠くまで延びるドレイン拡散領域64と、このドレイン拡散領域64よりも上方にあるソース拡散領域70a、70b、70cと、ドレイン拡散領域64まで延びるドレインコンタクト79と、ソース拡散領域まで延びるソースコンタクトと、を備え、これらドレインコンタクト79及びソースコンタクトは、ゲート線65a,65b,66cと平行に走る平面内にある。

(もっと読む)

ジルコニウム酸化膜を有する半導体素子のキャパシタ及びその製造方法

【課題】70nm以下の金属配線を有する次世代DRAMで要求される容量および良好な漏れ電流特性を確保できるキャパシタ及びその製造方法を提供する。

【解決手段】キャパシタ形成方法は、ストレージ電極65を形成するステップと、ストレージ電極65の表面をプラズマ窒化66A処理するステップと、該表面がプラズマ窒化66A処理されたストレージ電極65上にZrO2薄膜67を蒸着するステップと、ZrO2薄膜67の表面をプラズマ窒化処理して、表面が窒化66BされたZrO2薄膜を形成するステップと、窒化66Bされた前記ZrO2薄膜上にプレート電極68を形成するステップとを含む。

(もっと読む)

81 - 100 / 552

[ Back to top ]