Fターム[5F083AD49]の内容

Fターム[5F083AD49]に分類される特許

121 - 140 / 552

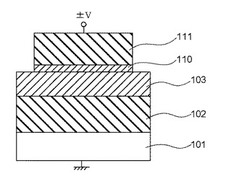

半導体記憶装置及びその製造方法

【課題】半導体記憶装置におけるトランジスタの特性向上と、キャパシタのリーク電流特性の両方を改善し、高信頼、高歩留のデバイスを提供する。

【解決手段】窒化チタンからなる下部電極102上に酸化ジルコニウムを主成分とする誘電体膜103を有するキャパシタにおいて、微結晶状態の酸化ジルコニウムを主成分とする誘電体膜を成膜し、2次的な結晶粒成長を伴わない条件でチタン化合物を主成分とする第一の保護膜110を形成し、その後、上部電極111を形成することで、上部電極形成時に伴う熱処理を行っても、またトランジスタの界面準位を低減する水素アニールを行っても、リーク電流の増大を抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜の形成を1000℃以上で行う場合に、Grow−in欠陥の発生の抑制と、BMDを用いたゲッタリング効果の向上を両立させる。

【解決手段】初期状態での酸素濃度が5×1017atoms/cm3以下の半導体基板に素子分離領域3を形成し、ゲート絶縁膜5aを1000℃以上の熱酸化により形成した後、酸素をイオン注入して熱処理することで、BMD層30を素子分離領域3の底面よりも下方に形成する。

(もっと読む)

半導体装置及びその製造方法、並びに吸着サイト・ブロッキング原子層堆積法

【課題】キャパシタの誘電体膜において、リーク特性改善のためのAlドープ層を設けても、誘電体膜がAlドープ層で分断されず、サイズ効果の影響を抑え、結晶性の良好な誘電体膜を提供する。

【解決手段】誘電体膜中に少なくとも1層のAlドープ層を有し、Alドープ層の1層におけるAl原子の面密度を1.4E+14[atoms/cm2]未満とする。また、その面密度を達成するため、通常のALDによる誘電体膜成膜と、Alソースの吸着サイトを制限するブロッカー分子の吸着を行った後、Alソースを吸着させ、反応ガスを導入して反応させる吸着サイト・ブロッキングALD法によるAl添加の組み合わせを採用する。

(もっと読む)

半導体装置の製造方法

【課題】容量コンタクトパッドと容量コンタクトプラグが一体となった構造を形成する。これにより、従来は2回、必要だったフォトリソグラフィ工程を1回に削減して、製造コストを低減する。

【解決手段】半導体装置の製造方法では、層間絶縁膜上に、開口を有するマスクパターンを形成する。このマスクパターンを用いて、層間絶縁膜をエッチングすることにより、開口の下の層間絶縁膜内に容量コンタクトホールを形成する。湿式エッチングにより、マスクパターン内の開口を大きくした後、開口内に導電材料を埋め込むことにより、それぞれ容量コンタクトプラグ及び容量コンタクトパッドを形成する。この後、容量コンタクトパッド上にキャパシタを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域となるSOI構造を有する半導体線条突出部の形状のばらつきを抑制し、トランジスタ特性のばらつきを減少することができる半導体装置を提供する。

【解決手段】半導体基板1の素子分離用の溝に埋込み絶縁膜が埋め込まれてなる素子分離領域2と、素子分離領域2によって区画されてなり、素子分離用の溝を区画する側壁面と半導体基板の1一面とを有し、かつ側壁面には埋込み絶縁膜に向けて突出した半導体線条突出部1aが素子分離用の溝に沿って設けられてなる活性領域Tと、半導体線条突出部1aを残して活性領域Tを分断するように設けられたゲート電極用のゲート溝3と、ゲート溝3の内面に形成されたゲート絶縁膜4と、ゲート溝3に埋め込まれたゲート電極5と、ゲート電極5のゲート長方向両側の活性領域Tにそれぞれ形成され、半導体線条突出部1aによって連結される不純物拡散領域7と、を具備してなることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で横方向に成長するシリコン膜が連結されることを防ぎつつ、活性領域上に十分な厚みのシリコン膜を形成可能とした半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上に第1のシリコン膜12aを選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に第1のシリコン膜12aを覆うのに十分な厚みでマスク絶縁膜を埋め込んだ後、このマスク絶縁膜を第1のシリコン膜12aの表面が露出するまでエッチングにより除去する工程と、第1のシリコン膜12a上に第2のシリコン膜12bを選択的にエピタキシャル成長させる工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセル領域の周辺に金属電極を有するアンチフューズを製造歩留り良く形成する。

【解決手段】MOSトランジスタを備えたメモリセルを有するメモリセル領域と、アンチフューズを備えた周辺回路領域とを有する半導体装置において、メモリセルを構成するコンタクトプラグ又はビット配線と同層に形成される周辺回路のコンタクトプラグ又は配線を用いて、アンチフューズの電極を形成する。

(もっと読む)

キャパシタの製造方法および半導体装置の製造方法

【課題】高温相の結晶構造の容量絶縁膜を電極上に直接形成可能なキャパシタの製造方法を提供する。

【解決手段】本発明のキャパシタCapの製造方法は、第一の電極3を形成する工程と、成膜温度が低い順に、非晶質相、低温相の結晶構造、高温相の結晶構造を形成し得る金属酸化物の形成工程であって、前記第一の電極3上に、前記低温相の結晶構造の成膜温度よりも低い第一の温度で前記非晶質相からなる前記金属酸化物を形成する工程と、前記第一の温度から、前記高温相の結晶構造の成膜温度である第二の温度まで、10℃/秒以上の昇温速度で昇温し、前記第二の温度で前記金属酸化物をアニールすることにより、前記金属酸化物に前記高温相の結晶構造を析出させて容量絶縁膜4とする工程と、前記容量絶縁膜4上に第二の電極5を形成する工程を採用する。

(もっと読む)

半導体装置の製造方法

【課題】メモリセル領域と周辺回路領域の双方におけるMOSトランジスタの最適化が可能な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、サイドウォールを側壁に有するゲート電極を含むMOSトランジスタを、半導体基板1上のメモリセル領域及び周辺回路領域に備えた半導体装置の製造方法であって、前記サイドウォールを形成した後に、選択エピタキシャル成長法により、前記半導体基板1上面にシリコン層10を形成する工程を備え、前記シリコン層10を形成した後に、少なくとも前記周辺回路領域をマスク20bで覆い、エッチングにより、前記メモリセル領域内のMOSトランジスタTr1のサイドウォール9cを薄化する工程を採用する。

(もっと読む)

半導体装置の製造方法

【課題】シリサイド層の成長に起因するゲート電極と半導体基板との間のショートの発生を抑制した上で、シリサイド層を厚く形成可能な半導体装置の製造方法を提供する。

【解決手段】ピラー26の側面にゲート絶縁膜27を介して、ゲート電極51、52を形成し、ピラー26の上端に上部不純物拡散領域36を形成し、上部不純物拡散領域36上に形成された層間絶縁膜39、68を貫通し、かつ上部不純物拡散領域36の上面を露出するシリンダ孔71を形成し、シリンダ孔71の底部に、上部不純物拡散領域36の上面を覆うと共に、シリンダ孔71の一部を埋め込むシリコン膜42を形成し、シリコン膜42の上面、シリコン膜42よりも上方に位置するシリンダ孔71の内面を覆うように下部電極57を形成すると共に、下部電極57を形成する際の熱により、シリコン膜42に含まれるSiと下部電極57に含まれる金属とを反応させてシリサイド層43を形成する。

(もっと読む)

半導体デバイス及びその製造方法

【課題】ゲート電極と上部導電層とのショートを防止した安定動作可能な縦型MOSトランジスタを有する半導体デバイスを提供する。

【解決手段】縦型MOSトランジスタを構成する半導体ピラー5Aは、第1の幅を有する上部5Aaと第2の幅を有する下部5Abを有し、上部5Aa側面は第2の絶縁膜6aと第3の絶縁膜6bで覆われ、下部5Abは側面から第2の絶縁膜6aまでゲート絶縁膜である第1の絶縁膜11Aで覆われており、ゲート電極13Aが第2及び第3の絶縁膜6により上部導電層18と絶縁されている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、溝内に残存する導電膜の高さばらつきを小さくすることで、半導体装置の特性のばらつきを低減可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】半導体基板13をエッチングして、幅W1とされた第1の溝部51を形成し、その後、第1の溝部51の下方に位置する半導体基板13をエッチングして、幅W1よりも狭い幅W2とされた第2の溝部52を形成することで、第1の溝部51、第2の溝部52、及び第1の溝部51の底面及び第2の溝部52の側面よりなる対向する一対の段差部54を有したビット線形成用溝を形成し、次いで、ビット線形成用溝15の内面を覆う絶縁膜16を介して、第2の溝部52を埋め込み、かつ第1の溝部51を埋め込まない厚さとされた第1の導電膜56を成膜し、その後、第1の導電膜56をエッチバックすることで、第2の溝部52の一部に第1の導電膜56を残存させる。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で電気的な短絡(ショート)が発生することを防止した半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上にシリコン膜12を選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に反射防止膜を埋め込んで平坦化した後、この平坦化した面上に、互いに隣接する活性領域5の各間において第1の方向Xに延在する開口部を有するマスクパターンを形成する工程と、マスクパターンの開口部から露出した部分を半導体基板の表面が露出するまでドライエッチングにより除去する工程とを含む。これにより、互いに隣接する活性領域5の間でシリコン膜12が横方向にエピタキシャル成長することによって連結された部分を、ドライエッチングにより切断し除去することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】メモリセル間の短絡を防止した上で、活性領域上にシリコン膜が十分に形成された半導体装置を提供する。

【解決手段】半導体基板2の表層に埋め込み形成された素子分離膜8によって、活性領域7が区画された半導体装置1であって、前記活性領域7の側面17が露出するように、前記素子分離膜8の上面の一部が除去されて設けられた凹部と、前記凹部を埋め込みつつ、前記活性領域7の上面7d及び前記側面17と接するように設けられたシリコン膜10と、を有することを特徴とする。

(もっと読む)

半導体装置

【課題】リーク電流が発生しにくく、低消費電力化に好適な半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体基板12内に埋め込まれてX方向に並列して延在する複数のビット線BLと、X方向と交差するY方向に延在するワード線と、ビット線BLと前記第2配線との交点に設けられたメモリセルMと、複数のビット線BLのうち最外列のビット線BLの外側に設けられ、X方向に延在してビット線BLと並走するダミービット線DBLとを含み、ダミービット線DBLが、半導体基板12に供給される電位と同じ電位が供給されるダミービット線(第1ダミー配線)DBL<0>、DBL<1>、DBL<2>を含むことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】リークパスを確実に防止することができる、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置は、ゲート絶縁膜を介して半導体基板上に設けられたゲート電極と、前記ゲート電極の側部に設けられた側壁絶縁膜と、前記半導体基板内における前記ゲート絶縁膜を挟むような位置に形成され、前記側壁絶縁膜により覆われた被覆領域と前記側壁絶縁膜により覆われていない露出領域とを有する、ソース又はドレイン領域と、前記ゲート電極及び前記側壁絶縁膜を覆うように形成された、エッチングストッパ膜と、前記半導体基板上に、前記エッチングストッパ膜を埋め込むように設けられた、層間絶縁膜と、前記層間絶縁膜を貫通するように設けられ、前記露出領域に接続される、第1セルコンタクトプラグとを具備する。前記エッチングストッパ膜は、前記被覆領域と前記露出領域との境界部分が完全に覆われるように、前記露出領域の一部を覆っている。

(もっと読む)

半導体装置及びその製造方法

【課題】フィールドシールド用トランジスタのゲート長を、背景技術と比べて長く取れるようにする。

【解決手段】半導体装置1は、底面並びに第1及び第2の側面を有するセル用ゲートトレンチ10と、トレンチ10より幅の狭いフィールドシールド用ゲートトレンチ11と、トレンチ10とトレンチ11の間に設けられた上部拡散層と、トレンチ10を挟んで第1の上部拡散層の反対側に設けられた第2の上部拡散層と、トレンチ11を挟んで第1の上部拡散層の反対側に設けられた第3の上部拡散層と、トレンチ10の底面に設けられた下部拡散層と、それぞれ第1及び第2の上部拡散層と電気的に接続された第1及び第2の記憶素子と、下部拡散層と電気的に接続されたビット線BLと、ゲート絶縁膜を介して第1及び第2の側面をそれぞれ覆うワード線WLと、ゲート絶縁膜を介してトレンチ11に埋め込まれたフィールドシールド用ゲート電極DWLとを備える。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】半導体装置の動作を安定化させつつ、面積効率の向上を図る。

【解決手段】半導体基板10に設けられ、メモリセルを構成する拡散層50、及びダミーセルを構成する拡散層52と、半導体基板10上に設けられた層間絶縁膜20、22と、層間絶縁膜22上に設けられ、拡散層50と重なる少なくとも1つの凹部32を有するシリンダー層絶縁膜24と、拡散層50上に設けられたコンタクトプラグ102と、拡散層52上に設けられたコンタクトプラグ104と、凹部32の側面及び底面上に設けられ、コンタクトプラグ102を介して拡散層52と接続する下部電極130と、下部電極130上、シリンダー層絶縁膜24上、及びコンタクトプラグ104上に設けられ、コンタクトプラグ104を介して拡散層52と接続する誘電体膜132と、誘電体膜132上に設けられた上部電極134と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極と半導体基板との間のショートの発生を抑制した上で、厚さが厚く、かつ均一な厚さとされたシリサイド層を形成可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート絶縁膜27を介して、ピラー26の側面26a,26bに設けられたゲート電極61,62と、ピラー26の上端26−1に形成されたシリサイド層38と、ゲート電極61,62を覆うと共に、ピラー26の側面を囲むように配置され、かつシリサイド層38の側面を露出する絶縁膜と、シリサイド層38の側面を覆うように設けられ、かつピラー26の上端26−1に含まれるシリコンをシリサイド化させる金属膜39と、シリサイド層38の下面38bと接触するように、ピラー26に形成された上部不純物拡散領域36と、シリサイド層38の上面38aに設けられたキャパシタ52と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、コンタクトプラグと埋め込み型のゲート電極との間に配置される絶縁膜の厚さを十分に確保可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート絶縁膜16を介して、半導体基板11に形成された凹部14の凹部14の一部を埋め込むゲート電極41と、ゲート電極41の上端面41aを覆うように凹部14内を埋め込む絶縁膜18と、凹部14の一方の側面14a側に位置する半導体基板11の主面11aに形成された不純物拡散領域43と、不純物拡散領域43の上面43aを覆うシリコン層21と、半導体基板11の主面11aに形成された第1及び第2の層間絶縁膜23,31に内設され、シリコン層21の上面21aと接触し、かつ下端34bがシリコン層21の上面21aと絶縁膜18の上面18aとの間に配置されたコンタクトプラグ34と、を備える。

(もっと読む)

121 - 140 / 552

[ Back to top ]