Fターム[5F083BS49]の内容

Fターム[5F083BS49]に分類される特許

1 - 20 / 34

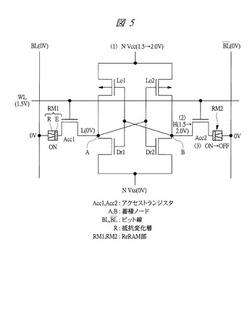

半導体記憶装置

【課題】不揮発性メモリ部内蔵のSRAMの特性の向上を図る。

【解決手段】SRAMを構成するアクセストランジスタAcc1とビット線BLとの間に抵抗変化層Rを有するReRAM部RM1を設け、アクセストランジスタAcc2とビット線/BLとの間に抵抗変化層Rを有するReRAM部RM2を設ける。SRAM通常動作期間の終了時において、例えば、蓄積ノードAに低電位(L=0V)、蓄積ノードBに高電位(H=1.5V)が保持されている場合、ReRAM部RM1をオン状態(ON)とし、ReRAM部RM2をオフ状態(OFF)とすることで、SRAMの保持データをReRAM部へ書き込み、再び、SRAM通常動作となった場合には、蓄積ノードAおよびBに対応するデータ書き戻すとともに、ReRAM部RM1、RM2の双方をオン状態に(リセット)する。

(もっと読む)

リレーデバイスを有するメモリ要素

【課題】メモリ要素有する集積回路を提供すること。

【解決手段】上記集積回路は、基板において形成された回路網と、回路網の上における複数の機械的リレーメモリ回路とを含む。集積回路は、回路網と複数の機械的リレーメモリ回路との間に配置された誘電スタックをさらに含む。誘電スタックは、複数の金属ルーティング層およびビア層を含む。回路網は、相補型金属酸化物半導体回路網を含む。回路網は、複数の機械的リレーメモリ回路に対する制御信号を生成するように動作可能である。

(もっと読む)

トンネルトランジスタ、トランジスタを含む論理ゲート、論理ゲートを使用するスタティックランダムアクセスメモリ、およびトンネルトランジスタの製造方法

【課題】第1、第2ゲートを有するトンネルトランジスタで、第1、第2のゲート間の電圧の差がより小さい場合にしようできるトンネルトランジスタを提供する。

【解決手段】ドレイン2、ソース4およびドレイン2とソース4との間で電流を制御するための少なくとも第1ゲート6とを含み、第1および第2のゲート誘電体材料7、11の第1側9、13が、それぞれ第1および第2の半導体部分14、15に実質的に沿って、実質的に接続して配置されたトンネルトランジスタ1。

(もっと読む)

半導体記憶装置

【課題】4個のトランジスタと2個のMTJ素子からなり、電源を印加しないでも不揮発性メモリとして動作するSRAMからなる半導体記憶装置を提供する。

【解決手段】第1及び第2のインバータ2,4と第1及び第2の転送用MOSFET3,5とを含むメモリセル1からなるSRAMにおいて、第1及び第2のインバータ2,4はスピン注入型のMTJ素子6,8と駆動用MOSFET7,9とからなり、これらのインバータ2,4からフリップフロップ回路が構成され、第1及び第2のインバータ2,4の出力端子は、それぞれ第1及び第2の転送用MOSFET3,5を介してビットライン及びビットラインバーに接続され、第1及び第2の転送用MOSFET3,5のゲートは、同一のワードラインに接続される。従来のSRAMに比較してメモリセルの面積が小さく、高速で低消費電力の不揮発性メモリが得られる。

(もっと読む)

不揮発性メモリセルおよび不揮発性メモリ

【課題】 スタティックノイズマージンを損なうことなく、揮発性記憶部および不揮発性記憶部間のストアとリコールを行える不揮発性メモリセルを提供する。

【解決手段】 不揮発性記憶部12は、揮発性記憶部11のノードV1とバイアス供給ノードNSとの間に直列に介挿されたNチャネルトランジスタTw1および抵抗変化型素子R1と、揮発性記憶部11のノードV2とバイアス供給ノードNSとの間に直列に介挿されたNチャネルトランジスタTw2および抵抗変化型素子R2を有する。ストア時、NチャネルトランジスタTw1およびTw2はONとされ、抵抗変化型素子R1およびR2は、ノードV1(V2)からバイアス供給ノードNSに向かう電流を通過させたときに高抵抗となり、逆方向の電流を通過させたときに低抵抗となる。リコール時は、揮発性記憶部11のフリップフロップに対する電源電圧を立ち上げる。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

半導体装置

【課題】本発明は、SOIにおいて適したゲッタリング方法を適用して得られる半導体装置を提供する。

【解決手段】埋め込み酸化膜と、埋め込み酸化膜上に表面シリコン層を有するSOI構造を有する半導体装置において、埋め込み酸化膜上に、表面シリコン層を活性層として有するトランジスタと、素子分離絶縁膜を有し、素子分離絶縁膜上に容量が形成されており、素子分離絶縁膜に希ガス元素又は金属元素が含まれていることを特徴とする半導体装置とする。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルに書き込み用のトランジスタ、読み出し用のトランジスタおよび選択用のトランジスタを備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体集積回路

【課題】セル面積が小さい不揮発性SRAMセルを提案する。

【解決手段】本開示に係わる半導体集積回路は、第1及び第2のインバーターINV1,INV2と、ゲートにワード線WLが接続され、ソースに第1のビット線BLが接続され、ドレインに第2のインバーターINV2の入力端子が接続される第1のトランジスタM5と、ゲートにワード線WLが接続され、ソースに第2のビット線bBLが接続され、ドレインに第1のインバーターINV1の入力端子が接続される第2のトランジスタM6と、第1の端子に第1のトランジスタM5のドレインが接続され、第2の端子に第1のインバーターINV1の出力端子が接続される第1の可変抵抗素子R1と、第1の端子に第2のトランジスタINV2のドレインが接続され、第2の端子に第2のインバーターINV2の出力端子が接続される第2の可変抵抗素子R2とを備える。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のソース電極および第1のドレイン電極と、第1のソース電極および第1のドレイン電極と電気的に接続され、酸化物半導体材料が用いられている第1のチャネル形成領域と、第1のチャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、を有する第1のトランジスタと、容量素子と、を有し、第1のトランジスタの第1のソース電極または第1のドレイン電極の一方と、容量素子の電極の一方とは、電気的に接続された半導体装置である。

(もっと読む)

ゲート型横型サイリスタベースランダムアクセスメモリ(GLTRAM)セルを製造するための方法

【解決手段】

ゲート型横型サイリスタベースメモリデバイス(gltram)を製造するための方法が提供される。半導体層(406)内の第1の伝導性タイプの第1、第2、第3及び第4のウエル領域(463,471,486,493)を含む半導体層(406)が設けられる。第1のゲート構造(465/408)は第1のウエル領域(463)上にあり、第2のゲート構造(475/408)は第2のウエル領域(471)上にあり、第3のゲート構造(485/408)は第3のウエル領域(486)上にあり且つ第2のゲート構造(475/408)と一体であり、第4のゲート構造(495/408)は第4のウエル領域(493)上に配置される。第1のゲート構造(465/408)の第1の側壁(414)及び第2乃至第4のゲート構造(475/408,485/408,495/408)の側壁(412,413,416,417,418,419)に隣接して側壁スペーサ(469)が形成される。また、第1のウエル領域(463)の部分(468)及び第1のゲート構造(465/408)の部分を覆う絶縁スペーサブロック(467)が形成される。絶縁スペーサブロック(467)は第1のゲート構造(465/408)の第2の側壁(415)に隣接する。第1のゲート構造(465/408)に隣接して第1のソース領域(472)が形成され、第1及び第2のゲート構造(465/408,475/408)の間に共通ドレイン/カソード領域(474/464)が形成され、第3のゲート構造(485/408)に隣接して第2のソース領域(482)が形成され、第3及び第4のゲート構造(485/408,495/408)の間に共通ドレイン/ソース領域(484/492)が形成され、第4のゲート構造(495/408)に隣接してドレイン領域(494)が形成される。第1のゲート構造(465/408)に隣接する絶縁スペーサブロック(467)の下で第1のウエル領域(463)内に延在する第1のベース領域(468)が形成され、第1のベース領域(468)に隣接する第1のウエル領域(463)内に延在するアノード領域(466)が第1のウエル領域(463)内に形成される。

(もっと読む)

別々の読み出し及び書き込みアクセストランジスタを有するゲート型横型サイリスタベースランダムアクセスメモリ(GLTRAM)セル並びにそれを組み込んだメモリデバイス及び集積回路

【解決手段】

書き込みビット線(452)、読み出しビット線(454)、及び少なくとも1つのメモリセル(410)を含むメモリデバイス(340)が提供される。メモリセル(410)は、書き込みアクセストランジスタ(470)と、読み出しビット線(454)及び先の書き込みアクセストランジスタ(470)に結合される読み出しアクセストランジスタ(480)と、先の書き込みアクセストランジスタ(470)に結合されるゲート型横型サイリスタ(GLT)デバイス(460)とを含む。その多くの特徴の中でも、メモリセル(410)は、読み出し及び書き込みビット線(454,452)を分離することによって読み出し動作中の読み出し障害を回避する。

(もっと読む)

半導体装置およびその製造方法、ならびにその半導体装置を用いた集積半導体装置および不揮発性半導体記憶装置

【課題】絶縁ゲート型電界効果トランジスタにおいて低電圧下で急峻なスイッチング特性を有する半導体素子を提供する。

【解決手段】大規模集積回路に用いられているプレーナ型のロジック回路用MOSFETにおいて、ドレイン拡散層電極のなかに、ダイオード素子と抵抗素子が並列配置されるように形成することで、低電圧であってもゲート電圧変化に対してドレイン電流が急峻な変化を示す高性能トランジスタが実現できる。

(もっと読む)

半導体装置の製造方法

【課題】リーク電流の発生なくp型領域やn型領域を半導体基板上に結晶成長させてなるサイリスタ構成の素子を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1の表面側にp型領域、n型領域、p型領域、およびn型領域がこの順に接して設けられた素子を備え、少なくとも1つの領域が半導体基板1の表面に結晶成長させた結晶成長層からなる半導体装置の製造方法において、第1n領域25および第2p領域27を結晶成長層として形成する際には、半導体基板1上に第1絶縁膜17と第2絶縁膜19との積層膜を成膜する第1工程と、第2絶縁膜19のエッチングに続けて第1絶縁膜17をウェットエッチングすることによって半導体基板1に達する開口を形成する第2工程と、開口底部に露出する半導体基板1の表面に、第1n領域25および第2p領域27を選択的に結晶成長させる第3工程とを行う。

(もっと読む)

半導体装置およびその製造方法およびその駆動方法

【課題】サイリスタ動作時に、寄生バイポーラトランジスタを作らせず、書き込みのディスターブの発生を防止して、誤書き込みを防止することを可能にするSRAM型の半導体装置とその製造方法を提供する。

【解決手段】半導体基板11に形成されたサイリスタ形成領域21を分離する素子分離領域12と、サイリスタ形成領域21に形成されていて、p型の第1領域(第1p型領域)p1と、n型の第2領域(第1n型領域)n1と、p型の第3領域(第2p型領域)p2と、n型の第4領域(第2n型領域)n2とが順に接合されたサイリスタT1、T2と、第2p型領域p2の下部に形成されたn型の第5領域(第1ウエル領域)31を有する半導体装置1において、第5領域31の底部および素子分離領域12の下部に接合するp型の第6領域(第2ウエル領域)32を有する。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタとサイリスタとを同一半導体基板に形成するとき、MOSトランジスタのエクステンション領域に対するサーマルバジェットの問題を回避することを可能にする。

【解決手段】第1p型領域p1、第1n型領域n1、第2p型領域p1、第2n型領域n2が順に接合され、第2p型領域p1にゲートが形成されたサイリスタTと、ソース・ドレイン領域43、44、53、54とエクステンション領域41、42、51、52を備えたMOSトランジスタ3、5とを半導体基板11に形成する半導体装置の製造方法であって、ゲート電極22の側壁に形成した第1サイドウォール23、24(図示せず)を用いてサイリスタTを完成させた後に第1サイドウォール23、24を除去してから、エクステンション領域41、42、51、52を形成することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】サイリスタ構成の半導体装置において、第2p型領域上に第1n型領域、第1p型領域を積層して形成しても、第1p型領域と第2p型領域とがショートを起こさないようにすることを可能とする。

【解決手段】p型の第1p型領域p1(第1領域)と、n型の第1n型領域n1(第2領域)と、p型の第2p型領域p2(第3領域)と、n型の第2n型領域n2(第4領域)とが順に接合されたサイリスタT1が素子分離領域13で分離された半導体装置1であって、第2p型領域p2は、素子分離領域13で分離された半導体基板11に形成され、第1n型領域n1は、第2p型領域p2の一部上に形成されて、かつ、前記第1n型領域n1と第2p型領域p2との界面の一端部が素子分離領域11の側壁部に接合するように形成されていることを特徴とする。

(もっと読む)

半導体装置

【課題】配線層にスイッチ素子を有するプログラム可能な半導体装置の提供。

【解決手段】第1の配線層101の配線と第2の配線層102の配線を接続するビア103の内部、ビアの第1の配線との接触部、第2の配線との接触部のうちの少なくとも1つに、電解質材料104等導電率が可変の部材が配設され、ビア103は、第1の配線との接触部を第1の端子、第2の配線との接触部を第2の端子とする導電率が可変型のスイッチ素子又は可変抵抗素子として用いられ、スイッチ素子の導電率を変えることで、第1の

端子と第2の端子との接触部との接続状態を、短絡、開放、又はその中間状態に可変に設定自在とされる。金属イオンの酸化還元反応によって、第1の電極と第2の電極間の導電率が変化する2端子スイッチ素子を備え、第1の電極に接続された逆極性の第1、第2のトランジスタと、第2の電極に接続された逆極性の第3、第4のトランジスタを備えている。

(もっと読む)

1 - 20 / 34

[ Back to top ]