Fターム[5F083EP02]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 電荷蓄積機構 (5,261) | FGを有するもの (3,098)

Fターム[5F083EP02]の下位に属するFターム

Fターム[5F083EP02]に分類される特許

161 - 180 / 2,151

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、酸化物半導体膜に酸素ドープ処理を行い、その後、酸化物半導体膜及び酸化物半導体膜上に設けられた酸化アルミニウム膜に対して熱処理を行うことで、化学量論的組成比を超える酸素を含む領域を有する酸化物半導体膜を形成する。該酸化物半導体膜を用いたトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジスタのしきい値電圧の変化量が低減されており、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体集積回路

【課題】不揮発性メモリを搭載した半導体集積回路において、外部端子を通して不揮発性メモリの特性テストを実施し、更に、その外部端子にサージ電圧が印加された場合であっても、そのサージ電圧が不揮発性メモリに伝わることを防止する。

【解決手段】半導体集積回路は、不揮発性メモリと、不揮発性メモリに対するデータ書き込み時、書き込み電圧が印加される書き込み制御線と、書き込み制御線に接続された第1ノードと、第1スイッチ回路を介して第1ノードに接続された外部端子と、スイッチ回路を介さずに外部端子に接続された第1ESD保護回路と、動作モードに応じて第1スイッチ回路をON/OFF制御する制御回路と、を備える。動作モードは、外部端子を用いて不揮発性メモリの特性テストを行うテストモードと、外部端子を使用しないユーザモードと、を含む。テストモードにおいて、制御回路は、第1スイッチ回路をONする。ユーザモードにおいて、制御回路は、第1スイッチ回路をOFFする。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】従来のMONOS型の不揮発性半導体記憶装置の製造方法では、トップ絶縁膜のエッチング加工にウェットエッチングを用いるため、サイドエッチングが侵攻してしまうという問題があった。これにより電荷蓄積層とゲート電極との間の絶縁性が損なわれ、電気的リークが発生し、消去特性などの電気特性が低下していた。

【解決手段】本発明の不揮発性半導体記憶装置の製造方法は、2つの犠牲膜を用いることにより、トップ絶縁膜と側壁保護膜とを同時に形成するエリアを作り出し、酸化処理によってそれらを形成する。このような製造方法とすることで、メモリゲート絶縁膜のサイドエッチングが発生することはない。

(もっと読む)

不揮発性メモリ

【課題】大容量NAND Flash Memory Chipに、プロセスコストが殆ど無く、SRAMに比べセル面積が小さいDRAMメモリを混載し、CHIPコストをおさえつつ、NANDのシステム性能を向上させることを可能とする複合メモリを提供すること。

【解決手段】第1絶縁膜と、第1Floating Gateと、第2絶縁膜と、第1ゲート電極からなる第1メモリセルと、第3絶縁膜と、第2Floating Gateと、第4絶縁膜と、第2ゲート電極と、第2Floating Gateと第4ゲート電極を接続する第1コンタクトからなる第1選択トランジスタと、第1メモリセルが直列に複数接続され、ビット線に接続され、第1選択トランジスタを介してソース線に接続されたもので第1セルブロックを構成し、これを複数配列する不揮発性メモリにおいて、面積S1が、面積S2に比べて大きい。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】耐圧確保に有利な構造を提供する。

【解決手段】実施形態の半導体記憶装置は、基板上で所定方向に平行に延伸した複数の素子分離領域と、隣接する素子分離領域に挟まれた素子領域上の第1絶縁膜と、素子領域上の所定方向に間隔を空けて形成され、第1絶縁膜の上に順に積層された電荷蓄積層、第2絶縁膜、及び制御ゲート電極をそれぞれ有する複数のワードラインと、その両側に1つずつ配置され所定方向の幅がワードラインより大きい選択トランジスタと、ワードライン及び選択トランジスタの上面を覆う層間絶縁膜と、ワードライン間に位置し上部を層間絶縁膜に覆われた第1空洞部と、選択トランジスタのワードラインとは反対側の側壁部に形成され上部が層間絶縁膜で覆われた第2空洞部を備える。実施形態の半導体記憶装置は、互いに隣接する選択トランジスタ間の基板表面に酸化膜が形成され、その下の所定方向に垂直方向の断面が凸型形状になっている。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの高容量化と面積の低減を可能とした半導体装置及びその製造方法を提供する。

【解決手段】EEPROMメモリセル50は、シリコン基板1のメモリセル領域に設けられたN-層21aと、トンネル絶縁膜13aと、浮遊ゲート電極15aと、電極間絶縁膜

17aと、制御ゲート電極19aと、を有する。また、キャパシタ60は、シリコン基板1のキャパシタ領域に設けられた下部電極層24aと、第1の誘電体膜13cと、共通電極15cと、第2の誘電体膜17cと、上部電極19cと、を有する。下部電極層24aと第1の誘電体膜13cと共通電極15cとにより第1のキャパシタ61が構成されると共に、共通電極15cと第2の誘電体膜17cと上部電極19cとにより第2のキャパシタ62が構成されており、第1のキャパシタ61と第2のキャパシタ62とが並列に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】本実施形態は、ゲートパターン加工時のアスペクト比を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板上に、ゲート絶縁膜と下部ゲート電極と電極間絶縁膜と上部ゲート電極とハードマスクとを順次形成し、選択トランジスタの形成予定領域に、ハードマスクと上部ゲート電極と電極間絶縁膜とを貫き、下部ゲート電極まで達する溝を形成し、溝の中に選択的に下部ゲート電極の結晶構造から影響を受けつつ結晶成長させることにより、特定の結晶配向を優先的に持つ結晶構造を有し、且つ、下部ゲート電極と上部ゲート電極とを電気的に接続する接続層を形成する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】クラックや結晶欠陥の発生なしに高電圧トランジスタの素子領域間の耐圧を向上できるようにした不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリセル領域の第1素子分離絶縁層が当該メモリセル領域の第1素子分離溝内に第1の酸化膜を埋め込んで構成され、第1の酸化膜の上面が半導体基板の上面と第1ゲート電極の上面との間に存在するように構成されている。

周辺領域の第2素子分離絶縁層は、周辺領域の第2素子分離溝内の全体に埋込まれると共にその上面が半導体基板の上面の上方に突出した第1の酸化膜と、当該第1の酸化膜上に積層され、その上面が第1導電膜の上面より上方に突出している第2の酸化膜とで構成されている。

(もっと読む)

半導体装置の製造方法

【課題】周辺回路素子の寿命を長くすると共に、後工程の熱処理等により周辺回路領域の素子分離溝部分に結晶欠陥が発生することを防止する。

【解決手段】本実施形態の半導体装置の製造方法は、半導体基板上の第1の領域に複数のメモリセルを形成し、前記半導体基板上の第2の領域に周辺回路素子を形成する半導体装置の製造方法であって、前記第1の領域に第1の開口幅を有する複数の第1の素子分離溝、前記第2の領域に前記第1の開口幅よりも広い第2の開口幅を有する第2の素子分離溝をそれぞれ形成する工程を備えた。さらに、前記第1の素子分離溝の内面に第1の膜厚の酸化膜を、前記第2の素子分離溝の内面に前記第1の膜厚よりも厚い第2の膜厚の酸化膜を、プラズマ酸化により一括形成する工程を備えた。

(もっと読む)

不揮発性半導体記憶装置

【課題】高駆動力と高信頼性を実現する選択ゲートスイッチトランジスタを備える不揮発性半導体記憶装置を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置は、選択ゲートスイッチトランジスタを備える不揮発性半導体記憶装置である。そして、この選択ゲートスイッチトランジスタが、半導体基板上に形成されるゲート絶縁膜と、ゲート絶縁膜上に形成されるゲート電極と、半導体基板中に、ゲート電極を挟むように設けられる第1のソース・ドレイン領域と第2のソース・ドレイン領域とを備えている。そして、第1のソース・ドレイン領域が、第1のn型不純物層と、第1のn型不純物層よりも不純物濃度が高く深さの浅い第2のn型不純物層を備えている。さらに、第2のソース・ドレイン領域が、第1のn型不純物層よりも不純物濃度が低く深さの浅い第3のn型不純物層と、第3のn型不純物層よりも不純物濃度が高く深さの深い第4のn型不純物層を備える。

(もっと読む)

膜形成方法および不揮発性記憶装置

【課題】より良質な膜を形成する。

【解決手段】実施形態の膜形成方法は、下地の上に設けられた酸素及び窒素の少なくともいずれかを含む膜の表面に、酸素及び窒素の少なくともいずれかを含むイオン化されたガスクラスタを照射して、前記ガスクラスタを照射した後の前記膜の密度を前記ガスクラスタを照射する前の前記膜の密度よりも高くする。

(もっと読む)

不揮発性半導体記憶装置

【課題】所定のレイアウト面積内において複数の抵抗値が得られる抵抗素子を有する不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板13上に配置された絶縁膜14と、絶縁膜14上に配置された導電層12と、導電層12上に配置された絶縁膜16と、絶縁膜16上に配置され、開口部を介して導電層12に接続された導電層11Aと、導電層11Aに接続されたコンタクト24Aと、絶縁膜16上に配置され、開口部を介して導電層12に接続された導電層11Bと、導電層11Bに接続されたコンタクト24Bと、絶縁膜16上に配置され、開口部を介して導電層12に接続された導電層11Cと、導電層11Cに接続されたコンタクト24Cとを備える。導電層12はフローティングゲート層と同じ材料から形成され、導電層11A、11B、11Cはコントロールゲート層と同じ材料から形成されている。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】コンタクトと素子領域間にかかる電界を緩和し絶縁破壊を防ぐ。

【解決手段】実施形態の半導体装置は、基板上第1方向に延伸し並列し高さが同じ第1〜4分離、第1、2分離間の低い第1領域、高さが等しい第2、3分離間の第2領域、第3、4分離間の第3領域、第1領域上面、第1分離の第2分離に対向した側面および上面の一部、第2分離の第1分離に対向した側面および上面の一部に接する第1電極15−1、その第2方向で第3領域上面、第3分離の第4分離に対向した側面および上面の一部、第4分離の第3分離に対向した側面および上面の一部に接する第2電極15−2を有す。半導体装置は、第1電極の第2方向とは異なる方向に位置し第2領域上面、第2分離の第3分離に対向した側面および上面の一部、第3分離の第2分離に対向した側面および上面の一部に接する第3電極を有す。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】ライナー膜をストッパ膜とした平坦化処理工程を設けることなくゲート電極上の段差を解消できるようにした不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置を提供する。

【解決手段】上端がキャップ膜と第2ゲート電極のシリコン層6との接触界面にほぼ一致するか低くなるようにメモリセルトランジスタの積層ゲート電極MG間および選択ゲート電極の積層ゲート電極SGD間に積層ゲート間絶縁膜8,9を形成する工程と、ライナー膜10を形成する工程と、選択ゲート電極SGD間のライナー膜10上に、第1の絶縁膜11を形成する工程と、ライナー膜10およびキャップ膜をエッチング処理する工程と、第1の絶縁膜11および積層ゲート間絶縁膜8,9をエッチングして第1の絶縁膜11の上面を第2ゲート電極6の上面高さとほぼ一致させる工程と、第2ゲート電極のシリコン層6の上部にシリサイド層7を形成する工程とを備える。

(もっと読む)

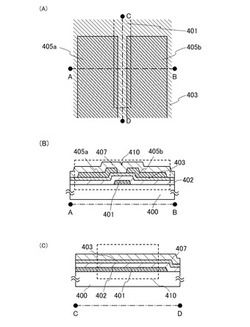

半導体装置及びその製造方法

【課題】微細なパターンを含む半導体装置の信頼性を向上する。

【解決手段】本実施形態の半導体装置は、素子形成領域100内の半導体素子と、素子形成領域100内から引き出し領域150内に延在する複数の配線WLと、引き出し領域150内の配線WLに接続されるコンタクト部39と、を具備し、配線WLは、n番(nは1以上の整数)の側壁膜のパターンに対応する(n+1)番目の側壁膜のパターンに基づいて形成され、配線WLの配線幅WW又は素子形成領域150内の配線間隔WDに対応する第1の寸法は、リソグラフィの解像度の限界寸法より小さく、露光波長がλ、レンズの開口数がNA、プロセスパラメータがk1で示される場合、第1の寸法は、(k1/2n)×(λ/NA)以下であり、引き出し領域内で互いに隣接する配線WLの間隔WC2に対応する第2の寸法は第1の寸法より大きい。

(もっと読む)

半導体装置の製造方法

【課題】露光パターンのピッチの1/4のピッチのパターンを形成する方法でありながら、形成されたパターンの本数を4の倍数以外の数にする。

【解決手段】第2のパターンおよび第2のマスクパターンを覆うと共に第1の膜の上に第3の膜を形成する工程と、第3の膜をエッチバック処理することにより、第2のパターンおよび第2のマスクパターンの側壁に第1の側壁ラインパターンおよび第1の側壁マスクパターンをそれぞれ形成する工程と、第2のマスクパターンおよび第1の側壁マスクパターンを覆うように第3のマスクパターンを形成する工程と、第3のマスクパターンをマスクとし、第2のパターンを第1の側壁ラインパターンに対して選択的にエッチングして除去した後、第3のマスクパターンを除去する工程とを備えた。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造工程数の削減が可能な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1、第2積層体、第1、第2半導体ピラー、第1、第2メモリ膜、接続部及び分断部を備えた不揮発性半導体記憶装置が提供される。第1、第2積層体は、第1軸に沿って積層された複数の第1、第2電極膜と、第1、第2電極膜間に設けられた第1、第2電極間絶縁膜と、をそれぞれ含む。第1、第2半導体ピラーは第1、第2積層体を第1軸に沿って貫通する。第2積層体は、第1積層体と並置される。接続部は第1、第2半導体ピラーを接続する。第1メモリ膜は、第1、第2電極膜と、第1、第2半導体ピラーとの間に設けられる。分断部は、第1、第2半導体ピラー間で第1、第2電極膜を分断し、接続部に接し、第1メモリ膜に用いられる材料を含む積層膜を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体集積回路内の抵抗素子の抵抗値のばらつきを抑制した半導体装置を提供する。

【解決手段】半導体装置は基板を備える。第1の絶縁膜は基板上に設けられる。第1の抵抗部は第1の絶縁膜上に設けられる。境界膜は第1の抵抗部上に設けられる。第2の抵抗部は境界膜上に設けられる。第2の絶縁膜は、第2の抵抗部上に設けられている。第1の導電部および第2の導電部は、第2の絶縁膜上に設けられ、互いに絶縁されている。第1の導電部は、第2の絶縁膜および第2の抵抗部を貫通して境界膜の表面に接触する第1のコネクト部を含む。第2の導電部は、第2の絶縁膜および第2の抵抗部を貫通して境界膜の表面に接触する第2のコネクト部を含む。第1の抵抗部は、一端において第1のコネクト部を介して第1の導電部に電気的に接続され、かつ、他端において第2のコネクト部を介して第2の導電部に電気的に接続された抵抗素子である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気的特性の良好なトランジスタ及びその作製方法を提供することを課題の一とする。

【解決手段】基板上に酸化物半導体膜及び絶縁膜を有し、酸化物半導体膜の端部は絶縁膜と接しており、酸化物半導体膜は、チャネル形成領域と、チャネル形成領域を挟んで形成されたドーパントを含む領域とを含み、酸化物半導体膜上に接して形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、サイドウォール絶縁膜を有するゲート電極と、サイドウォール絶縁膜、酸化物半導体膜、および絶縁膜に接して形成されたソース電極およびドレイン電極とを有する半導体装置である。

(もっと読む)

161 - 180 / 2,151

[ Back to top ]