Fターム[5F083EP02]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 電荷蓄積機構 (5,261) | FGを有するもの (3,098)

Fターム[5F083EP02]の下位に属するFターム

Fターム[5F083EP02]に分類される特許

201 - 220 / 2,151

半導体記憶装置及びその製造方法

【課題】コンタクトとアクティブエリアとの間のショートマージンを確保できる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板の上層部分に形成され、前記上層部分を第1方向に延びる複数本のアクティブエリアに区画する複数本の素子分離絶縁体と、前記アクティブエリアに接続されたコンタクトと、を備える。そして、各前記アクティブエリアの上面のうち、前記第1方向における一部の領域には、前記第1方向に対して直交する第2方向において前記アクティブエリアの全体にわたって凹部が形成されている。前記第1方向において、隣り合う前記アクティブエリアにそれぞれ接続された2本の前記コンタクトの位置は相互に異なる。前記コンタクトは前記凹部の側面に接し、底面には接していない。

(もっと読む)

半導体記憶装置の製造方法

【課題】隣接するメモリセル間およびメモリセルと選択トランジスタとの間に間隙を設けつつ、選択トランジスタおよび周辺回路における短絡を抑制する。

【解決手段】本実施形態による半導体記憶装置は、ゲートを有する複数のメモリセルが直列に接続されたメモリセルストリングを備える。選択トランジスタが、メモリセルストリングの一端にある端部メモリセルに接続されている。側壁膜が、端部メモリセルと選択トランジスタとの間において、端部メモリセルのゲートの側面および選択トランジスタのゲートの側面を被覆する。端部メモリセルの側壁膜と選択トランジスタの側壁膜との間に空隙がある。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ゲートの端部に集中する電界を緩和し、電荷のトラップおよびトンネル絶縁膜の破壊を抑制し、信頼性を向上させる。

【解決手段】半導体記憶装置は、半導体基板上に設けられたアクティブエリアを備えている。素子分離部が、アクティブエリア間に設けられ、絶縁膜で充填されている。データを記憶する複数のメモリセルがアクティブエリアに形成されている。空洞が、アクティブエリアのメモリセルが形成された部分の上端縁部と素子分離部内の絶縁膜との間に設けられている。

(もっと読む)

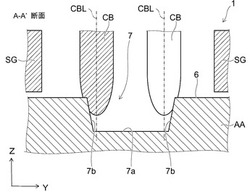

半導体装置

【課題】動作特性に対する信頼性を向上させることができる半導体装置を提供する。

【解決手段】シリコンを含む基板7と、前記基板7上に設けられた積層体6と、を有する半導体装置1であって、前記積層体6は、少なくとも前記積層体6の側壁の前記基板側にフッ素を含む抑制領域13を有している。前記抑制領域13は、基板7上に設けられた絶縁膜2の前記側壁側に設けられ、フッ素濃度は、チャネル領域11のフッ素濃度よりも高い。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

半導体素子及びその製造方法

【課題】絶縁膜を貫通するコンタクトプラグの抵抗を改善させられる半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグと、前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、を含む。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

半導体記憶装置及びその高電圧制御方法

【課題】チャージポンプ等の高電圧生成部の回路面積を削減する。

【解決手段】半導体記憶装置は、ワードライン及びビットラインが接続されマトリクス状に配置された複数のメモリセル21と、ワードラインを駆動する複数のワードラインドライバ23a及び23b、電源電圧を昇圧して高電圧を生成するチャージポンプ11と、複数のメモリセル21のうちアクセスに関係のある箇所には高電圧が印加され、アクセスに関係のない箇所には電源電圧が印加されるように制御するX方向高電圧制御回路31及びY方向高電圧制御回路32とを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】 トランジスタの接合耐圧と表面耐圧の劣化を抑制し、信頼性の高い不揮発性半導体記憶装置を提供する。

【解決手段】 トランジスタTr.2は、ソース高濃度領域9を有するソース拡散層、メモリセルのゲート絶縁膜より厚いゲート絶縁膜16を有するゲート電極、ドレイン高濃度領域9とドレイン高濃度領域を囲むドレイン低濃度領域23を有するドレイン拡散層22を備え、ドレイン拡散層22は、ゲート絶縁膜16の底面より低い第1の窪みを有し、ドレイン低濃度領域23は、第1の窪みより低い第2の窪み“c”を有し、ドレイン高濃度領域9に接合されるコンタクト10を介してビット線に接続され、ソース高濃度領域に接合されるコンタクトを介してセンスアンプに接続される。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流の極めて小さい酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上に加熱処理により酸素を放出する下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、基板を加熱処理する。次に、第1の酸化物半導体膜上に導電膜を形成し、該導電膜を加工してソース電極およびドレイン電極を形成する。次に、第1の酸化物半導体膜を加工して第2の酸化物半導体膜を形成した直後にソース電極、ドレイン電極および第2の酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】トランジスタの素子領域の端部に形成される寄生トランジスタの影響を軽減することができる不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板10内に形成された素子領域10Aと、素子領域10A上に形成された第1のゲート絶縁膜14と、第1のゲート絶縁膜14上に形成された第1のゲート電極15と、第1のゲート電極15上に形成され、開口を有するゲート間絶縁膜16と、ゲート間絶縁膜16上に形成され、開口を介して第1のゲート電極15と接する第2のゲート電極12と、素子領域10A、第1のゲート絶縁膜14および第1のゲート電極15によって形成された積層構造を囲む素子分離領域11とを備える。素子領域10Aの側面、第1のゲート絶縁膜14の側面及び第1のゲート電極15の側面と、素子分離領域11との間には空隙18Aが形成されている。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。酸化物半導体層の側壁はサイドウォール絶縁層により覆われている。なお、該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

記憶素子、記憶装置、信号処理回路、記憶素子の駆動方法

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶素子を提供する。消費電力の低減可能な信号処理回路を提供する。

【解決手段】クロック信号に同期してデータを保持する記憶素子において、酸化物半導体層にチャネルが形成されるトランジスタ及び容量素子を用いることより、電源電圧の供給が停止した間もデータ保持ができる。ここで、電源電圧の供給を停止する前に、クロック信号のレベルを一定に保った状態で当該トランジスタをオフ状態とすることにより、データを正確に容量素子に保持させることができる。また、このような記憶素子を、CPU、メモリ、及び周辺制御装置のそれぞれに用いることによって、CPUを用いたシステム全体で、電源電圧の供給停止を可能とし、当該システム全体の消費電力を削減することができる。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】データ消失温度が高く、かつ生産性の高い不揮発性記憶装置およびその製造方法を提供することである。

【解決手段】実施形態に係る不揮発性記憶装置の製造方法は、第1の記憶部と、第1の記憶部が有するデータ消失温度よりも高いデータ消失温度を有する第2の記憶部と、を有する不揮発性記憶装置の製造方法であって、第2の記憶部のメモリセルを形成するための第2の積層体を形成する工程と、第1の記憶部が形成される領域に形成された第2の積層体を除去する工程と、第1の記憶部のメモリセルを形成するための第1の積層体を形成する工程と、第2の記憶部が形成される領域に形成された第1の積層体を除去する工程と、第1の記憶部が形成される領域に形成された第1の積層体と、第2の記憶部が形成される領域に形成された第2の積層体と、を同時に処理して、第1の積層体から第1の記憶部のメモリセルを形成するとともに、第2の積層体から第2の記憶部のメモリセルを形成する工程と、を備えている。

(もっと読む)

記憶装置

【課題】誤書込みを防止することが可能な記憶装置を提供する。

【解決手段】複数のメモリセルが直列に接続されたNANDセルユニットと、NANDセルユニットの一方の端子に接続する第1の選択トランジスタと、NANDセルユニットの他方の端子に接続する第2の選択トランジスタと、第1の選択トランジスタと接続するソース線と、該ソース線と交差し、且つ第2の選択トランジスタと接続するビット線とを有し、第1の選択トランジスタ及び第2の選択トランジスタは、チャネル領域が酸化物半導体層で形成されたトランジスタである。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】良好な電気特性及び信頼性を有する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、半導体基板に形成された素子分離溝に埋め込まれた素子分離絶縁膜と、素子分離溝により所定間隔だけ隔てられ、且つ、半導体基板上に第1の絶縁膜と電荷蓄積膜とが順次積層されてなる積層構造の複数のメモリセルと、電荷蓄積膜と素子分離絶縁膜との上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された制御電極膜とを有し、素子分離絶縁膜の上面は電荷蓄積膜の上面よりも低く、第2の絶縁膜は、電荷蓄積膜上のセル上部分と素子分離絶縁膜上のセル間部分とを備え、セル上部分の誘電率はセル間部分の誘電率よりも低い。

(もっと読む)

半導体記憶装置の製造方法、及び半導体記憶装置

【課題】1つの実施形態は、例えば、トンネル電流を容易に増加できる半導体記憶装置の製造方法、及び半導体記憶装置を提供することを目的とする。

【解決手段】1つの実施形態によれば、半導体記憶装置の製造方法が提供される。半導体記憶装置の製造方法では、Ge、Sn、C、及びNのいずれかの不純物を半導体基板の表面に導入する。半導体記憶装置の製造方法では、前記不純物が導入された前記半導体基板の表面にトンネル絶縁膜が形成されるように、前記半導体基板を熱酸化する。半導体記憶装置の製造方法では、前記トンネル絶縁膜上に電荷蓄積層を有するゲートを形成する。半導体記憶装置の製造方法では、前記ゲートと自己整合的に前記半導体基板内に不純物拡散領域を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、窒素、リン、又は砒素など15族元素のいずれか一以上の元素が添加されている。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】トンネル領域を有する半導体不揮発性メモリにおいて、トンネル領域の周囲部分は掘り下げられており、掘り下げられたドレイン領域には、空乏化電極絶縁膜を介して、トンネル領域の一部を空乏化するための電位を自由に与えることが可能な空乏化電極を配置する。

(もっと読む)

201 - 220 / 2,151

[ Back to top ]