Fターム[5F083EP22]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 制御機構 (7,428) | CGを有するもの (4,415)

Fターム[5F083EP22]の下位に属するFターム

スタックゲート (1,853)

スプリットゲート (271)

CGがFGを覆う構造 (414)

CGを複数有するもの (58)

Fターム[5F083EP22]に分類される特許

41 - 60 / 1,819

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】ソース電極層405a及びドレイン電極層405bの端部と、ゲート電極層401の端部とを重畳させ、更に酸化物半導体層403のチャネル形成領域となる領域に対して、ゲート電極層401を確実に重畳させることで、トランジスタのオン特性を向上させる。また、絶縁層491中に埋め込み導電層を形成し、埋め込み導電層481a,481bと、ソース電極層405a及びドレイン電極層405bとの接触面積を大きくとることで、トランジスタのコンタクト抵抗を低減する。ゲート絶縁層402のカバレッジ不良を抑制することで、酸化物半導体層403を薄膜化し、トランジスタの微細化を実現する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法とデータ書き換え方法

【課題】データ保持時間を、マスクROMと同様の無限大とすることができる、長期にわたりデータを保持できる信頼性の高いEEPROMを提供する。

【解決手段】不揮発性半導体記憶装置は、所定のセンスレベルに対して熱平衡状態しきい値電圧が正方向である第1の不揮発性半導体記憶素子100に正のデータを記憶し、熱平衡状態しきい値電圧が負方向である第2の不揮発性半導体記憶素子200に負のデータを記憶することでデータ保持時間を無限大にする。

(もっと読む)

半導体不揮発性メモリ及びデータ書き込み方法

【課題】データ書き込み時における書き込み回数を減らし、且つ読み出し精度を高めることが可能な半導体不揮発性メモリ及びデータ書き込み方法を提供する。

【解決手段】書き込むべきデータの値に対応した量の電荷を電荷蓄積部に注入することによって書き込みを行うデータ書き込み手段を有し、データ書き込み手段によるデータの書き込みに先立ち、電荷蓄積部各々から読み出し電流を送出させ、読み出し電流が最大読み出し電流閾値よりも大となる電荷蓄積部に、この読み出し電流が最大読み出し電流閾値を下回るまで電荷を注入する初期化書き込みを行う。

(もっと読む)

半導体装置

【課題】結晶性の優れた酸化物半導体層を形成して電気特性の優れたトランジスタを製造

可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを目的の一つとす

る。

【解決手段】第1の加熱処理で第1の酸化物半導体層を結晶化し、その上部に第2の酸化

物半導体層を形成し、温度と雰囲気の異なる条件で段階的に行われる第2の加熱処理によ

って表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層の形成と酸素

欠損の補填を効率良く行い、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加

熱処理を行うことにより、酸化物半導体層に再度酸素を供給し、酸化物絶縁層上に、水素

を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導

体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】不純物添加シリコン層に添加された不純物が不純物無添加シリコン層に拡散するのを抑制する。

【解決手段】セレクトゲート電極SG1上にはワード線WL1が積層され、最上層のワード線WL1上にはセレクトゲート電極SG2がロウごとに形成されることで、NANDセルNC1が構成され、セレクトゲート電極SG1、SG2およびワード線WL1は、不純物添加シリコン層2と層間絶縁膜とを拡散防止層3を介して交互に積層することで構成し、ワード線WL1は、拡散防止層3にて挟まれた不純物添加シリコン層2にて構成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルトランジスタに電荷を蓄積する際の電圧を従来よりも自由に設定し得る不揮発性半導体記憶装置を提案する。

【解決手段】不揮発性半導体記憶装置1では、選択メモリセルトランジスタ115に電荷を蓄積させる際、電圧の高い書き込み禁止電圧をP型MOSトランジスタ9bから印加し、電圧の低い書き込み電圧をN型MOSトランジスタ15aから印加して、選択メモリセルトランジスタ115又は非選択メモリセルトランジスタ116へ電圧を印加する役割分担を、P型MOSトランジスタ9b及びN型MOSトランジスタ15aに分けたことで、P型MOSトランジスタ9b及びN型MOSトランジスタ15aそれぞれのゲート電圧やソース電圧を個別に調整でき、最終的にゲート基板間電圧を例えば4[V]等に設定し得る。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化を実現し、トランジスタとして十分に機能できる電気的特性を付与された半導体装置を提供する。

【解決手段】半導体層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタを有する半導体装置において、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体膜を用いる。該半導体装置において、酸化物半導体膜は作製工程において酸素が導入され、酸素を多く(過剰に)含む膜であり、トランジスタを覆う酸化アルミニウム膜を含む絶縁層が設けられる。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】チャネル移動度を向上させた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20上に設けられたメモリトランジスタ40と選択トランジスタ50を有する。メモリトランジスタ40は、導電層41a〜41d、メモリゲート絶縁層43、柱状半導体層44、及び酸化層45を有する。導電層41は、メモリトランジスタ40のゲートとして機能する。メモリゲート絶縁層43は、導電層の側面に接する。半導体層44は、導電層と共にメモリゲート絶縁層43を一方の側面で挟み、半導体基板20に対して垂直方向に延び、メモリトランジスタ40のボディとして機能する。酸化層45は、半導体層44の他方の側面に接する。半導体層44は、シリコンゲルマニウムにて構成される。酸化層45は、酸化シリコンにて構成される。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】寄生抵抗がより低いチャネルボディ層を有する不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態の不揮発性半導体記憶装置は、半導体層と、第1絶縁層が表面に設けられた第2絶縁層と、第3絶縁層と、第2絶縁層および第3絶縁層の上に、電極層と絶縁膜とを有する第1積層体と、第1積層体の積層方向に貫通し第2絶縁層に達する一対の第1ホールのそれぞれの側壁に設けられたメモリ膜と、メモリ膜の内側に設けられた第1チャネルボディ層と、層間絶縁膜と選択ゲートとを有する第2積層体と、一対の第1ホールのそれぞれ上端と連通し、第2積層体の積層方向に貫通する第2ホールの側壁に設けられたゲート絶縁膜と、ゲート絶縁膜の内側に設けられた第2チャネルボディ層と、第1積層体の下側に設けられた連結部と、一対の第1ホールの間に挟まれ、第1積層体の表面から第1絶縁層に達する第4絶縁層と、を備える。

(もっと読む)

二重フローティングゲート構造を有するトランジスタを備えた不揮発性メモリ

【課題】CMOS製造プロセスに用いることのできる材料を用いかつノイズマージンの広い不揮発性メモリを提供する。

【解決手段】本実施形態の不揮発性メモリによれば、第1および第2のPチャネルトランジスタはそれぞれ第1の半導体領域上に設けられ、第1の半導体領域上に、第1の絶縁膜と、第1のフローティングゲート、第2の絶縁膜、第2のフローティングゲート、第3の絶縁膜、および第1の制御ゲートが、この順序で積層された構造を有し、前記第1および第2のNチャネルトランジスタはそれぞれ第2の半導体領域上に設けられ、前記第2の半導体領域上に、第4の絶縁膜、第3のフローティングゲート、第5の絶縁膜、第4のフローティングゲート、第6の絶縁膜、および第2の制御ゲートがこの順序で積層された積層構造を有している。

(もっと読む)

半導体装置およびその製造方法

【課題】実施形態は、一括して形成することが可能なメモリセルを有し、その直下に制御回路を設けた構成を実現する半導体装置およびその製造方法を提供する。

【解決手段】実施形態は、基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、前記第1のコンタクトホールの内部に、前記p形半導体領域に接したコンタクトプラグを形成する工程と、を備える。さらに、前記n形半導体領域に連通する第2のコンタクトホールを前記絶縁層に形成する工程と、前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、を備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】読み出し速度の向上を図ることができる半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、交互に積層して設けられた複数の電極膜及び層間絶縁膜を有した積層体と、前記積層体を積層方向に貫く半導体ピラーと、前記半導体ピラーと前記電極膜との間に設けられた電荷蓄積膜と、前記半導体ピラーの側面に設けられた添加部と、を備えている。そして、前記半導体ピラーは、ゲルマニウムを含む半導体材料を用いて形成され、前記添加部は、酸化アルミニウムを用いて形成されている。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

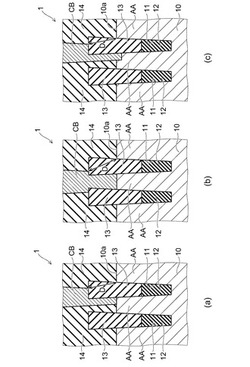

不揮発性半導体記憶装置

【課題】円筒型MONOSメモリセルで電荷保持特性の向上を図る。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に形成され、上面から下面まで達する円筒状の貫通ホールを有するコントロールゲートCGと、前記貫通ホール内における前記コントロールゲートの側面上に形成されたブロック絶縁膜150と、前記貫通ホール内における前記ブロック絶縁膜の側面上に形成された電荷蓄積膜151と、前記貫通ホール内における前記電荷蓄積膜の側面上に形成されたトンネル絶縁膜152と、前記貫通ホール内における前記トンネル絶縁膜の側面上に形成された半導体層SPと、を具備し、前記トンネル絶縁膜は、SiO2を母材とし、添加することで前記母材のバンドギャップを低下させる元素を含む第1絶縁膜を含み、前記元素の濃度および濃度勾配は、前記半導体層側から前記電荷蓄積膜側に向かって単調に増加する。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

41 - 60 / 1,819

[ Back to top ]