Fターム[5F083EP22]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 制御機構 (7,428) | CGを有するもの (4,415)

Fターム[5F083EP22]の下位に属するFターム

スタックゲート (1,853)

スプリットゲート (271)

CGがFGを覆う構造 (414)

CGを複数有するもの (58)

Fターム[5F083EP22]に分類される特許

1,801 - 1,819 / 1,819

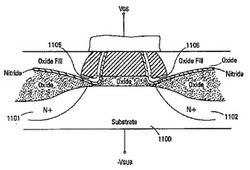

自己整合型電荷分離構造NROMフラッシュメモリ

【課題】電荷捕獲領域が重ならずにセルを小さくすることが可能なトランジスタを提供する。

【解決手段】窒化物リードオンリーメモリ(NROM)セルは、窒化物層を有し、前記窒化物層は、トランジスタの中心部の下方に配置されない。前記窒化物層を有するゲート絶縁層は、2つの部分を有する。各部分は、構造分離された(structurally defined and separated)電荷捕獲領域を有する。電荷は、トランジスタの動作方向に応じて、ある特定の捕獲領域に蓄積される。前記ゲート絶縁層の前記2つの部分は、ポリシリコンゲート構造体の中間部分から外側部分を分離する。

(もっと読む)

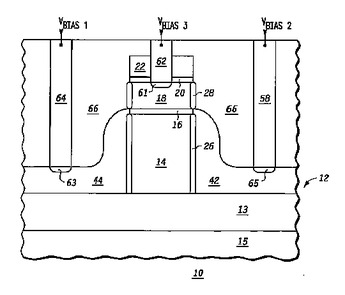

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

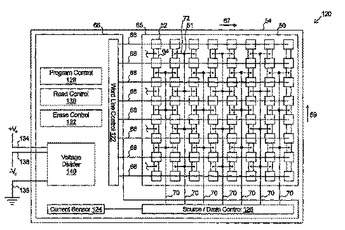

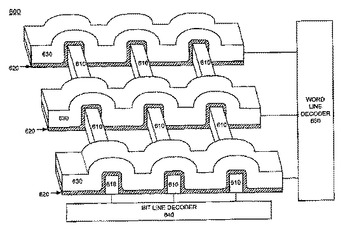

スタガー式ローカル接続構造を持つメモリセルアレイ

メモリセルアレイ(50)は、半導体基板(54)に製造された、2次元アレイのメモリセル(52)を含む。メモリセル(52)は、行方向(67)を形成する複数の行と、列方向(69)を形成する複数の列で並べられている。メモリセル(52)の各列は、複数の交互に配置されたチャネル領域(58)及びソース/ドレイン領域(64)を含む。各ソース/ドレイン領域(64)上には導電性インターコネクト(72)が配置されており、この導電性インターコネクト(72)はただ1つのその他のソース/ドレイン領域(64)に結合する。この1つのソース/ドレイン領域(64)とは、その列に隣接する第2の列に存在する領域である。導電性インターコネクト(64)は、1つおきの導電性インターコネクト(64)がその列の右側に隣接する列に接続するように、また、1つおきの導電性インターコネクトが、その列の左側に隣接する列に接続するように、配置される。複数のソース/ドレインコントロールライン(70)は、隣接するメモリセル(52)の列間に延在し、また、その隣接する列と列との間を結合する各導電性インターコネクト(72)に電気的に結合する。  (もっと読む)

(もっと読む)

過剰消去されたセルを復旧させるために、正のゲートストレスを使用したメモリデバイスおよびそのための方法

複数のメモリセルから構成されたフラッシュ電気的消去可能読出し専用メモリ(EEPROM)デバイス(10)の消去方法は、複数のメモリセル(10)をプリプログラミングするステップ(100)と、複数のメモリセル(10)に消去パルスを印加するステップ(110)と、を有し、これに消去検証(120)が続く。この消去検証(120)の後に、スレッショルド電圧が所定の最小レベル(VTMIN)を下回るメモリセルのソフトプログラミング(135)と、複数のメモリセル(10)への正のゲートストレスの印加(130)が続く。この消去方法は、過剰消去を防止し、スレッショルド電圧分布を低減する。  (もっと読む)

(もっと読む)

ナノクラスターを備えた半導体デバイス

ナノクラスターを備えたデバイスを形成するプロセス。本プロセスは、ナノクラスター(例えばシリコンナノ結晶)を形成する段階と、デバイスの誘電体を形成する次の段階中に酸化剤によるナノクラスターの酸化を抑制するためにナノクラスターを覆って酸化バリア層を形成する段階とを含む。酸化バリア層の少なくとも一部は、誘電体の形成後に除去される。1つの実施例では、本デバイスは、ナノクラスターがメモリの電荷蓄積トランジスタの電荷蓄積位置として利用されるメモリである。この実施例では、酸化バリア層が、メモリの高電圧トランジスタ用のゲート誘電体を形成することにより、ナノクラスターを酸化剤から保護する。 (もっと読む)

電荷損失が減少された窒化物層を備えるメモリセル構造及びその製造方法

本発明の一実施形態に従って、半導体基板(210)、半導体基板上に配置された第1シリコン酸化物層(215)、第1シリコン酸化物層上に配置された電荷格納層(220)、電荷格納層上に配置された第2シリコン酸化物層(225)、及び第2シリコン酸化物層上に配置されたゲート層(230)がメモリセル構造に含まれる。例示的な実施形態では、例えば、水素含有量が約0at%〜約0.5at%の範囲に減少されたシリコン窒化物が電荷格納層(220)に含まれる。電荷格納層(220)における水素含有量が減少されることで、結果として電荷損失が減少される。電荷損失が減少された電荷格納層(220)が、メモリデバイスにおける閾電圧シフト、プログラミングデータ損失及びプログラミング性能損失を減少する利点を有し、その結果メモリデバイスパフォーマンスを改善する。  (もっと読む)

(もっと読む)

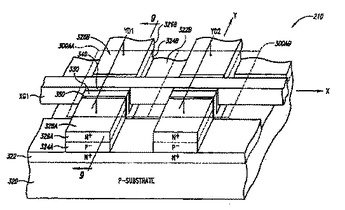

不揮発性半導体記憶装置、その製造方法、電子カード及び電子装置

【課題】 カップリング比のばらつきを小さくできるNAND型EEPROMを提供する。

【解決手段】 メモリセルの電荷蓄積層17の上層導電部23は、互いに間を設けて形成された一対の立上り部27により構成される内側面29及び外側面31を有する。内側面29側には底面高さ調節層43があり、外側面31側には素子分離絶縁層5がある。このため、半導体基板9の位置(A)のメモリセルと位置(B)のメモリセルとで、立上り部27の高さが異なっていても、電荷蓄積層17と制御ゲートCGとが対向する領域の面積を同じにできる。

(もっと読む)

不揮発性メモリを電荷トラッピングするための改善された消去および読み取り手法

本発明は、不揮発性電荷トラッピング型メモリデバイスのアレイを動作させるための方法を述べる。方法は、アレイの実質的に全ての不揮発性メモリデバイスのブロック消去ステップの前に、アレイの実質的に全ての不揮発性メモリデバイスにブロック書き込みするステップを備える。本発明の利点は、これを行なうことにより、さらなる電荷トラッピング型不揮発性メモリデバイスを、基準セルとして使用できることであり、基準セルは、アレイ内のメモリセルのブロック書き込みおよびブロック消去によって書き込みおよび消去され、したがって、基準セルは、アレイ内のメモリセルと同一の繰り返し履歴を示す。この特性を用いて、読み取りパラメータを目盛りセルの経年変化に適応させることができる。また、対応するデバイスも、提供される。  (もっと読む)

(もっと読む)

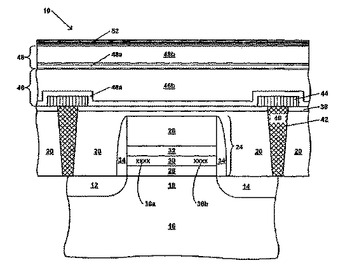

不揮発性メモリおよびその製造方法

トランジスタの制御ゲート(28)およびウェル領域(12)に、それぞれ、第1および第2の電圧を印加するステップを含む不揮発性メモリのトランジスタ(10)の電荷蓄積場所から放電するための方法。第1の電圧はトランジスタの制御ゲートに印加され、制御ゲートは、トランジスタの選択ゲート(18)に隣接して位置する一部を少なくとも有する。トランジスタは、制御ゲートの下に位置するトランジスタの構造の誘電体(22,26)内に配置されたナノクラスタ(24)を有する電荷蓄積場所を含む。最後に、第2の電圧が、制御ゲートの下に位置するウェル領域(12)に印加される。第1の電圧および第2の電圧の印加により、電荷蓄積場所のナノクラスタから電子を放出するために前記構造の両端に電圧差が発生する。  (もっと読む)

(もっと読む)

電界効果トランジスタ及びその製造方法

SiC基板1と、SiC基板1表面に形成されたソース3a及びドレイン3bと、SiC表面に接して形成され厚さが1分子層以上のAlN層5と、その上に形成されたSiO2層とを有する絶縁構造と、この絶縁構造上に形成されたゲート電極15とを有しており、SiCとの間の界面状態を良好に保ちつつ、リーク電流を抑制することができる。 (もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

耐久性が改善された分離トランジスタメモリ及びその製造方法

本発明は、フラッシュメモリ装置のような不揮発性メモリ装置に使用されるフローティングゲートトランジスタ構造を有する。1つの実施の形態において、システムはCPUとメモリ装置とを有し、該メモリ装置は複数のメモリセルを有するアレイを具備する。メモリセルは複数の柱状構造とこれら柱状構造間に挿入され、これら柱状構造のうちの1つに近接するフローティングゲート構造とを有する。他の実施の形態において、メモリ装置10は、複数のメモリセルを有するアレイを具備する。メモリセルは隣接する複数のFETを有し、これらFETは、ソース/ドレイン領域と共通のフローティングゲート構造を有し、該フローティングゲート構造は、1つのFETのソース/ドレイン領域から第1間隔だけ離間し、且つ、他のFETのソース/ドレイン領域から第2間隔だけ離間している。さらに他の実施の形態において、メモリ装置は、基板上に複数の柱状構造を配置し、これら複数の柱状構造間にフローティングゲートを、これら柱状構造のうちの1つに近接するように挿入することによって形成される。  (もっと読む)

(もっと読む)

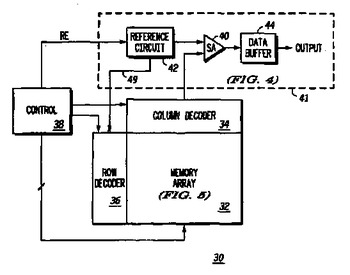

不揮発性メモリにおける基準トランジスタ用可変ゲート・バイアス

不揮発性メモリ(30)はナノクリスタルメモリセル(50、51、53)を備える。メモリセルトランジスタ(50、51、53)のプログラム及び消去閾値電圧は、プログラム/消去動作の回数の関数として上昇する。読み出し動作の間、基準トランジスタ(46)がセル電流と比較するための基準電流を供給する。基準トランジスタ(46)がナノクリスタルを含まないことを除いて、基準トランジスタ(46)は、メモリセルトランジスタ(50、51、53)を製造する際に用いるのと同様のプロセスで製造される。同様のプロセスを用いて基準トランジスタ(46)及びメモリセルトランジスタ(50、51、53)双方を製造することにより、基準トランジスタ(46)の閾値電圧は、メモリセルトランジスタ(50、51、53)の閾値電圧のずれに追従する。基準トランジスタ(46)のゲートにバイアスをかけるために、読み出し制御回路(42)が設けられている。読み出し制御回路(42)は、基準トランジスタ(46)のドレイン電流を検知し、基準電流をセル電流に対して実質的に一定値に維持するように、ゲートバイアス電圧を調節する。  (もっと読む)

(もっと読む)

不揮発性メモリデバイス

不揮発性メモリデバイス(100)は、基板(110)、絶縁層(120)、フィン(210)、複数の誘電層(310〜330)及び制御ゲート(510/520)を備える。絶縁層(120)は、基板(110)上に形成され、フィン(210)は、絶縁層(120)上に形成される。誘電層(310〜330)は、このフィン(210)を覆うように形成され、制御ゲート(510/520)は、誘電層(310〜330)上に形成される。誘電層(310〜330)は、メモリデバイス(100)の電荷格納構造として機能する酸化物−窒化物−酸化物層を備える。  (もっと読む)

(もっと読む)

電荷蓄積場所を有するメモリ

メモリは、チャネル領域(1725)を含む半導体構造(1105)の対向する側壁に隣接するゲート構造と、ゲート構造と対向する側壁との間にある複数の電荷蓄積場所(1713、1715、1709及び1711)とを有する。チャネル領域は、2つの電流端子領域間に配置され、それらの電流端子領域は一例ではソース/ドレイン領域としての役割を果たす。メモリセルは、メモリセルのアレイ(1801)内に実装することができ、一方のゲート構造が1つのワード線に結合され、他方のゲート構造が別のワード線に結合される。一例では、各セルは、それぞれが1ビットのデータを記憶する、4つの電荷蓄積場所を含む。  (もっと読む)

(もっと読む)

個別ゲート構造を備えたトランジスタ

個別ゲート構造(701,703)を備えたトランジスタを形成する方法。これらのゲート構造はそれぞれ、半導体構造(105)の複数の側壁に隣接する。本方法は、ゲート材料層(203)を含む少なくとも一つの共形な層を、チャネル領域を含む半導体基板の上に堆積させることを含む。平坦層(403)がウェハの上に形成される。平坦層は、基板上の所定の位置において少なくとも一つの共形な層の頂部表面よりも低い位置に頂部表面を有する。少なくとも一つの共形な層をエッチングすることにより、半導体構造の上のゲート材料は除去される。  (もっと読む)

(もっと読む)

BEOLプロセスにおいて、UVによって誘発されたSONOSデュアルビットのフラッシュメモリデバイスの電荷を低減するUVブロック層

SONOSフラッシュメモリセル(24)をUVにより誘発される電荷から保護する方法であって、SONOSフラッシュメモリセル(24)を半導体デバイス(10、50)に製造するステップと、SONOSフラッシュメモリセル(24)上に、少なくとも1つのUV保護層(38、46、48、又は52)を蒸着させるステップとを含み、UV保護層には実質的にUV不透過性の材料が含まれる。SONOSフラッシュメモリセル(24)と、少なくとも1つのUV保護層(38、46、48又は52)(UV保護層には実質的にUV不透過性の材料が含まれる)を含むSONOSフラッシュメモリデバイス(10、50)が提供される。  (もっと読む)

(もっと読む)

フラッシュメモリデバイスの特性を改善する方法

半導体デバイスを製造する方法において、シリコン基板(62)上にゲート酸化膜(60)を提供する。このゲート酸化膜(60)上に第1ポリシリコン層(64)を提供し、第1ポリシリコン層(64)上に絶縁層(66)を提供し、またこの絶縁層(66)上に第2ポリシリコン層(68)を提供する。適切なマスキングを実行した後にエッチングステップが実行されると、シリコン基板を露出させ、かつこのシリコン基板上にスタックゲート構造を形成すべく、第2ポリシリコン層、絶縁層、第1ポリシリコン層、およびゲート酸化膜の一部を除去するようにこれらの層がエッチングされる。スタックゲート構造(72)上に薄い酸化膜(80)を成長させるべく、短時間(例えば10秒から20秒)の急速熱アニールを実行する。それから、急速熱アニールによって形成された酸化膜(80)上に第2酸化膜(82)をたい積する。

(もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】下層のポリシリコン膜を酸化させることなく、酸素アニールによりHTO膜を十分に改質させ、電気的にリークが少ないトンネル酸化膜を形成する半導体装置の製造方法を提供すること。

【解決手段】ポリシリコン膜からなる第1フローティングゲート16上に、窒化膜26又は酸窒化膜28を介してHTO膜を成膜し、酸素アニール処理を施して、トンネル酸化膜18(HTO膜)を形成する。

(もっと読む)

1,801 - 1,819 / 1,819

[ Back to top ]