Fターム[5F083EP49]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 絶縁膜 (4,144) | ゲート絶縁膜 (1,132) | 材料 (527)

Fターム[5F083EP49]に分類される特許

21 - 40 / 527

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートの閾値電圧の変動が抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、交互に積層された複数の電極層と複数の第1絶縁層とを有する第1積層体と、第1積層体を貫通する第1ホールの側壁に設けられたメモリ膜と、第1ホール内に設けられたメモリ膜の内側に設けられた第1チャネルボディ層と、第1積層体の上に設けられた層間絶縁膜と、層間絶縁膜の上に設けられた選択ゲート電極層と、選択ゲート電極層の上に設けられた第2絶縁層と、を有する第2の積層体と、第1ホールに連通し第2積層体および層間絶縁膜を貫通する第2ホールの側壁に設けられたゲート絶縁膜と、第2ホール内におけるゲート絶縁膜の内側に設けられ、第1チャネルボディ層とつながった第2チャネルボディ層と、を備える。選択ゲート電極層と第2絶縁層との界面における第2ホールの径は選択ゲート電極層と層間絶縁膜との界面における第2ホールの径よりも小さい。

(もっと読む)

不揮発性半導体記憶装置

【課題】カップリング比の増大と書き込み/消去時のリーク電流の低減とを実現する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、半導体層11と、半導体層11上の第1の絶縁層13と、第1の絶縁層13上の電荷蓄積層14と、電荷蓄積層14上の第2の絶縁層15と、第2の絶縁層15上の制御ゲート電極16とを備える。第2の絶縁層15は、電荷蓄積層14側から制御ゲート電極16側に向かって、第1のランタンアルミネート層LAO、ランタンアルミシリケート層LASO及び第2のランタンアルミネート層LAOを備える。

(もっと読む)

三次元集積回路を作製する方法

【課題】集積回路を作製する新規なタイプの方法を提供する。

【解決手段】少なくとも第3の層がその間に配置された、少なくとも半導体の第1および第2の層を備える基板を作製するステップと、少なくとも第1のMOSデバイスを作製するステップであって、その活性領域が半導体の第1の層の少なくとも一部に形成される、ステップと、少なくとも第2のMOSデバイスを作製するステップであって、その活性領域が半導体の第2の層の少なくとも一部に形成され、第2のMOSデバイスの活性領域が第2のMOSデバイスのゲートと第1のMOSデバイスの活性領域との間に配置される、ステップとを少なくとも含む、集積電子回路を作製する方法。

(もっと読む)

不揮発性半導体記憶装置

【課題】高い信頼性を有し且つ安価な不揮発性半導体記憶装置を提供する。

【解決手段】この不揮発性半導体記憶装置において、メモリストリングスは、基板に対して垂直方向に延びる一対の柱状部、及び前記一対の柱状部の下部を連結させるように形成された連結部を有する半導体層と、前記柱状部の側面を取り囲むように形成された電荷蓄積層と、前記柱状部の側面及び前記電荷蓄積層を含む第1の絶縁膜と、前記柱状部の側面及び前記第1の絶縁膜を覆うように形成された第1導電層と、前記連結部の周囲に形成される第2の絶縁膜と、前記連結部に前記ゲート絶縁膜を介して形成される第2導電層とを備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】信頼性を向上させることができる半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、積層して設けられた複数のゲート電極と、前記ゲート電極の間に設けられた絶縁膜と、を有した積層体と、前記積層体を貫く半導体ピラーと、前記半導体ピラーと前記ゲート電極との間に空隙を介して設けられた電荷蓄積層と、前記電荷蓄積層と前記ゲート電極との間に設けられたブロック絶縁層と、を有したメモリセルを積層方向に複数備えている。そして、前記複数の各メモリセル毎に、前記電荷蓄積層と前記半導体ピラーとの間の距離を保つ支持部が設けられている。

(もっと読む)

導電性側壁スペーサを有する不揮発性メモリ装置及びその製造方法

【課題】従来の窒化膜側壁を電荷トラップ媒体に利用する場合の信頼性劣化を改善した不揮発性メモリ装置を提供する。

【解決手段】半導体基板21上のゲート絶縁膜22Aと、該ゲート絶縁膜上に順に積層して形成された第1電極膜23、第2電極膜24、及びハードマスク膜25を有するゲート100と、該ゲートの第1電極膜23及び第2電極膜24の両側壁に形成された一対の再酸化側壁スペーサ27と、該再酸化側壁スペーサ及びゲート100のハードマスク膜25の両側壁上に形成された一対の側壁スペーサ28Aと、一対の側壁スペーサ28A上に形成された、電荷を捕獲及び放出する一対の導電性側壁スペーサ29Bと、半導体基板21内に形成された一対のLDD領域26と、半導体基板21内に形成されたソース/ドレイン領域30とを備え、導電性側壁スペーサ29Bが、ゲート100及び側壁スペーサ28Aよりも低い高さを有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高性能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1及び第2のメモリセルMCを有し、第2の方向に延びるフィン型積層構造Fin0〜Fin3と、フィン型積層構造Fin0〜Fin3の第2の方向の一端に接続され、第3の方向に延びる梁5とを備える。フィン型積層構造Fin0〜Fin3及び梁5は、それぞれ、第1の方向に積み重ねられる第1及び第2の半導体層2a,2bを備え、梁5は、第3の方向の一端に第1及び第2の半導体層2a,2bに対するコンタクト部を有し、かつ、梁5とフィン型積層構造Fin0〜Fin3の接続部からコンタクト部まで延びる低抵抗領域8を有する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

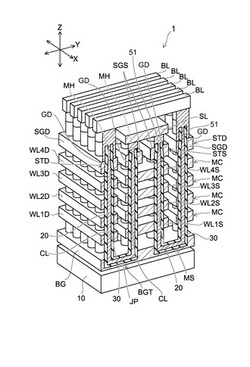

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼でき、非常に小型の3次元集積回路メモリ用の構造を低い製造コストで提供する。

【解決手段】3次元アレイは第1の端部と第2の端部を含む2つの端部を有し、第1の端部と第2の端部の一方はビット線BLに接続され、第1の端部と第2の端部の他方はソース線CSLに接続される不揮発性メモリセルのNANDストリングのスタック1412、1413、1414と、ビット線BL及びソース線SLの一方をメモリセルのストリング1412、1413、1414に接続させるダイオード1492を有する。

(もっと読む)

半導体装置

【課題】消去特性と消去ディスターブ特性との双方を向上することが可能な、MONOS型メモリセルなどの半導体装置を提供する。

【解決手段】半導体基板SUBの主表面に形成される第1のゲート電極CGと、主表面上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる絶縁膜ONOと、第1および第2のゲート電極CG,MGの真下のチャネル領域を挟むように、主表面に形成される1対のソース/ドレイン領域NR1,NR2とを備える。上記ソース領域NR1は、第1のソース領域N11および第2のソース領域N12を含んでいる。上記第2のソース領域N12は第1のソース領域N11よりも主表面から深い領域に形成されている。上記第1のソース領域N11と第2のソース領域N12とに含まれる不純物の材質が異なっている。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

半導体記憶装置

【課題】3次元型の半導体記憶装置のパフォーマンスを向上させる。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板と、半導体基板上に設けられ、積層された複数のメモリセルを含む複数のメモリユニットと、カラム方向に配列された複数のメモリユニット上に複数本形成されたビット線とを備え、複数のビット線のロウ方向の配列ピッチは、メモリユニットのロウ方向の配列ピッチよりも小さく、カラム方向に配列された各メモリユニットの端部は、複数本形成されたビット線のいずれか1つに接続される。

(もっと読む)

固集積フラッシュメモリーセルストリング、セル素子、及びこの製造方法

【課題】優れた縮小化特性を有し、閾値電圧の散布を減らすことができるフラッシュメモリーセルストリング及びこの製造方法を提供する。

【解決手段】本発明は、フラッシュメモリーセルストリング及びこの製造方法に関する。前記フラッシュメモリーセルストリングは、多数のセル素子及び前記セル素子の端部に連結されるスイッチング素子を含む。前記セル素子は、半導体基板と、半導体基板に順次に積層される透過絶縁膜と、電荷貯蔵ノードと、コントロール絶縁膜と、制御電極とを備え、ソース/ドレーンが形成されないことを特徴とする。前記スイッチング素子は、セル素子に連結される側にソースまたはドレーンを含まないし、セル素子に連結されない側にソースまたはドレーンを含むが制御電極と重なり、又はまたは重ならないことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】選択用トランジスタのゲート電極と記憶用トランジスタのゲート電極との間の耐圧を確保し、かつ閾値電圧の変動が抑制されたMONOS型メモリセルを提供する。

【解決手段】主表面SBSを有する半導体基板SUBと、主表面SBS上に形成された第1のゲート電極CGと、主表面SBS上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる第1の絶縁膜ONOとを備える半導体装置である。上記第2のゲート電極MGの最上面MGSは第1のゲート電極CGの最上面CGSより低くなっている。上記第2のゲート電極MGの最上面MGSは主表面SBSに沿うように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性半導体装置の高集積化を図ることのできる技術を提供する。

【解決手段】スイッチ用nMIS(Qs)のスイッチゲート電極SGと、スイッチ用nMIS(Qs)にワード線に対して交差する方向に沿って隣接するメモリ用nMIS(Qm)のメモリゲート電極MGとの間に、スイッチ用nMIS(Qs)のソース/ドレイン領域SDHとして機能し、同時にメモリ用nMIS(Qm)のドレイン領域Dとして機能する半導体領域を形成し、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)側のソース/ドレイン領域SDHを構成する半導体領域の形状と、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)と反対側(ビット線側)のソース/ドレイン領域SDLを構成する半導体領域の形状とを非対称とする。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置の集積化を図る。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板と半導体基板上に設けられ、積層された複数のメモリセルを含むメモリセルアレイと、複数のメモリセルと電気的に接続されて平行に配列された複数のビット線と、ビット線接続配線を介してビット線と接続された複数のセンスアンプとを備える。ビット線接続配線は、隣接するN(Nは2以上の整数)本ごとに1つのグループとする。センスアンプは、ビット線接続配線が延びる第1方向にはNよりも小さい数で、且つ前記第1方向と交差する第2方向には前記グループ間のピッチよりも小さいピッチで配列されている。

(もっと読む)

不揮発性メモリ装置及びその製造方法

【課題】半導体基板のセル領域と周辺回路領域との間に段差をなくして、工程を容易かつ単純にしつつ、特に、コンタクトナットオープン(Contact not open)、下部構造物に対するアタック(Attack)などを防止し、工程歩留まり及び信頼性を向上させることができる不揮発性メモリ装置及びその製造方法を提供すること。

【解決手段】周辺回路領域及び該周辺回路領域より高さが低いセル領域を有する半導体基板と、該半導体基板の前記セル領域上に配置され、複数の層間絶縁膜及び複数の制御ゲート電極が交互に積層された制御ゲート構造物と、該制御ゲート構造物が形成された前記半導体基板の前記セル領域を覆う第1の絶縁膜と、該第1の絶縁膜上の選択ゲート電極と、前記半導体基板の前記周辺回路領域上の周辺回路素子とを備えることを特徴とする。

(もっと読む)

選択トランジスタ、選択トランジスタの作成方法、メモリ装置及びメモリ装置の製造方法

【課題】少ない工程数で製造でき、フラットバンド電圧のシフトを抑制できる選択トランジスタ、選択トランジスタの作成方法、メモリ装置及びメモリ装置の製造方法を提供すること。

【解決手段】直列接続された複数のメモリトランジスタを備えたメモリ装置で用いられる選択トランジスタであって、半導体基板上に形成されたトンネル絶縁層と、トンネル絶縁層上に形成された電荷蓄積層と、電荷蓄積層上に形成され、アルゴンをソースガスとするガスクラスタイオンビームが照射されたブロッキング絶縁層と、ブロッキング絶縁層上に形成されたゲート電極と、ゲート電極の両側の半導体基板中に形成されたソース/ドレイン領域と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の電気的性能および信頼性を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGは、金属膜6aと金属膜6a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極であり、金属膜6aの上端部には、金属膜6aの一部が酸化することで金属酸化物部分17が形成されている。スプリットゲート型の不揮発性メモリの制御ゲート電極は、金属膜4aと金属膜4a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極である。

(もっと読む)

半導体装置およびその製造方法

【課題】FMONOSメモリセルとCMOSトランジスタが共存する半導体装置において、トランジスタの駆動電流を高めるとともにFMONOSメモリセルとしての機能を確保する半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面上に形成された、チャネルを有するMONOS型メモリセルと、主表面上に形成されたnチャネル型トランジスタと、主表面上に形成されたpチャネル型トランジスタとを備える半導体装置である。上記MONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタの上面に接するように窒化膜CS1、CS2が形成されている。上記窒化膜CS1、CS2はMONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタのチャネルに応力を付加する。

(もっと読む)

21 - 40 / 527

[ Back to top ]