Fターム[5F083EP49]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 絶縁膜 (4,144) | ゲート絶縁膜 (1,132) | 材料 (527)

Fターム[5F083EP49]に分類される特許

41 - 60 / 527

不揮発性半導体記憶装置及びその製造方法

【課題】 メモリセルにおける絶縁特性が向上する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】 実施形態に係る不揮発性半導体記憶装置は、半導体領域を持つ。前記半導体領域の表面には金属元素を含む界面領域が設けられる。前記界面領域の表面にはトンネル絶縁膜が設けられる。前記トンネル絶縁膜の表面には電荷蓄積絶縁膜が設けられる。前記電荷蓄積絶縁膜の表面にはブロック絶縁膜が設けられる。前記ブロック絶縁膜の表面には制御ゲート電極が設けられる。

(もっと読む)

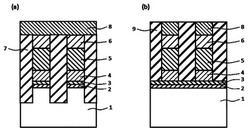

半導体装置およびその製造方法

【課題】不揮発性メモリおよび容量素子を有する半導体装置の性能を向上させる。

【解決手段】同一の半導体基板1上に、不揮発性メモリのメモリセルMCと容量素子とが形成されている。メモリセルMCは、半導体基板の上部に絶縁膜3を介して形成された制御ゲート電極CGと、半導体基板1の上部に形成されて制御ゲート電極CGと隣合うメモリゲート電極MGと、メモリゲート電極MGと半導体基板1との間および制御ゲート電極CGとメモリゲート電極MGとの間に形成されて内部に電荷蓄積部を有する絶縁膜5とを有している。容量素子は、制御ゲート電極CGと同層のシリコン膜で形成された下部電極と、絶縁膜5と同層の絶縁膜で形成された容量絶縁膜と、メモリゲート電極MGと同層のシリコン膜で形成された上部電極とを有している。そして、上部電極の不純物濃度は、メモリゲート電極MGの不純物濃度よりも高くなっている。

(もっと読む)

ダイオードストラッピングを備えた熱アシストフラッシュメモリ

【課題】フラッシュメモリの動作速度及び耐久性を向上させる技術の提供。

【解決手段】メモリが、行及び列を含むメモリセルのアレイを有している。該メモリは、アレイ内の単数又は複数のワード線上の第1の離隔位置のセットに第1のバイアス電圧を印加するとともに、単数又は複数のワード線上の第2の離隔位置のセットに第1のバイアス電圧とは異なる第2のバイアス電圧を印加する、ワード線に結合された回路部を有し、第1の離隔位置のセットにおける位置は、第2の離隔位置のセットの位置の間に介在しており、それにより、第1の離隔位置のセットにおける位置と第2の離隔位置のセットにおける位置との間に、単数又は複数のワード線の加熱をもたらす電流の流れが誘導される。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜(第1の結晶性酸化物半導体膜ともいう)を形成し、該酸化物半導体膜に酸素を導入して少なくとも一部を非晶質化し酸素を過剰に含む非晶質酸化物半導体膜を形成する。該非晶質酸化物半導体膜上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体膜の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜(第2の結晶性酸化物半導体膜ともいう)を形成する。

(もっと読む)

熱アシスト誘電体電荷トラップメモリ

【課題】

誘電体電荷トラップメモリの動作速度及び/又は耐久性を向上させる技術を提供する。

【解決手段】

メモリデバイスは、ワードライン及びビットラインを含む誘電体電荷トラップ構造メモリセルのアレイを含む。該アレイに、読み出し、プログラム及び消去の動作を制御するように構成された制御回路が結合される。コントローラは、該アレイのメモリセル内の誘電体電荷トラップ構造を熱アニールする支援回路を備えるように構成される。熱アニールのための熱を誘起するために、ワードラインドライバ及び前記ワードライン終端回路を用いて、ワードラインに電流を誘起することができる。熱アニールは、サイクルダメージからの回復のために、通常動作とインターリーブされて適用されることが可能である。また、熱アニールは、消去のようなミッション機能中に適用されることもでき、それにより該機能の性能を向上させ得る。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みビットライン型不揮発メモリの微細化に適した製造方法を提供し、かつコンタクトの位置ずれに起因するビットライン間ショートを生じ難い構造を提供する。

【解決手段】導電体膜が埋め込まれたシャロートレンチ溝内にビットライン拡散層を設けてSONOS構造セルとする。これにより、ビットライン拡散層の半導体基板主面上での面積を大きくせずにビットライン拡散層の抵抗を低くすることができ、セル面積を増大させることなく安定した電気的特性の半導体記憶装置が得られる。また、Si3N4のサイドウォールを設けてイオン注入することでビットラインを形成する。これにより、メモリセルの微細化が可能となる。

(もっと読む)

トンネル障壁の上に電界分布層を有する電荷捕獲装置

【課題】チャネル幅寸法に沿った電荷捕獲構造の電荷密度が一様でない場合でもチャネル幅寸法に沿ってしきい値電圧を一様に維持したフラッシュメモリセルおよびフラッシュメモリセルの製造方法を提供する。

【解決手段】ソース領域及びドレイン領域を有する表面を有し、前記ソース領域及び前記ドレイン領域がチャネル領域によって分離された半導体基板と、前記チャネル領域の上の前記基板の表面上に配置された3nmを超える実質的なゲート絶縁膜厚を有するトンネル障壁絶縁体構造105、前記トンネル障壁絶縁体構造及び前記チャネル領域の上に配置された導電層101、前記導電層及び前記チャネル領域の上に配置された電子捕獲構造106、並びに前記電子捕獲構造及び前記チャネル領域の上に配置された上側絶縁体構造107を有する、前記チャネル上の多層スタックと、前記上側絶縁体構造及び前記チャネル領域の上に配置された上側導電層108とを具える。

(もっと読む)

半導体素子の形成方法

【課題】相互接続領域の具現が困難なパッドレイアウトを具現化し、オーバレイマージンを増大できる半導体素子の形成方法を提供する。

【解決手段】半導体基板に被食刻層、第1のハードマスク物質層、第1の分割パターン物質層及び第2のハードマスク物質層を形成して選択食刻し第2のハードマスクパターンを形成し、これをマスクとし第1の分割パターン物質層を食刻し第1の分割パターンを形成する。第1のハードマスク物質層の上部にスペーサ物質層及び第2の分割パターン物質層を形成し、第1の分割パターンが現われるまでスペーサ物質層及び第2の分割パターン物質層を部分食刻しスペーサ物質層を露出させ、複数の第1の分割パターン間に第2の分割パターンを形成し、第1、第2の分割パターンをマスクとしスペーサ物質層及び第1のハードマスク物質層を食刻し第1のハードマスクパターンを形成し、これをマスクとし被食刻層を食刻し微細パターンを形成する。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】従来のMONOS型の不揮発性半導体記憶装置の製造方法では、トップ絶縁膜のエッチング加工にウェットエッチングを用いるため、サイドエッチングが侵攻してしまうという問題があった。これにより電荷蓄積層とゲート電極との間の絶縁性が損なわれ、電気的リークが発生し、消去特性などの電気特性が低下していた。

【解決手段】メモリゲート絶縁膜の形成前に保護絶縁膜を形成し、この保護絶縁膜によりメモリゲート絶縁膜のサイドエッチングを防止する製造方法とすることで、電荷蓄積層とゲート電極との間の絶縁性が向上する。そして、この保護絶縁膜を不揮発性半導体記憶装置の製造後も側壁保護膜として残してもよい。そうすると不揮発性半導体記憶装置の完成後に、他の半導体素子を形成するためのウェットエッチング工程があったとしても、メモリゲート絶縁膜がサイドエッチングされることはない。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】従来のMONOS型の不揮発性半導体記憶装置の製造方法では、トップ絶縁膜のエッチング加工にウェットエッチングを用いるため、サイドエッチングが侵攻してしまうという問題があった。これにより電荷蓄積層とゲート電極との間の絶縁性が損なわれ、電気的リークが発生し、消去特性などの電気特性が低下していた。

【解決手段】本発明の不揮発性半導体記憶装置の製造方法は、2つの犠牲膜を用いることにより、トップ絶縁膜と側壁保護膜とを同時に形成するエリアを作り出し、酸化処理によってそれらを形成する。このような製造方法とすることで、メモリゲート絶縁膜のサイドエッチングが発生することはない。

(もっと読む)

有機分子メモリ

【課題】電荷保持特性に優れた有機分子メモリを提供する。

【解決手段】実施の形態の有機分子メモリは第1の導電層と、第2の導電層と、第1の導電層と第2の導電層との間に設けられ、電荷蓄積型分子鎖または抵抗変化型分子鎖を含み、電荷蓄積型分子鎖または前記抵抗変化型分子鎖が縮合多環系の基を備える有機分子層と、を備えている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 チャネルにおける電子の移動度低下を抑制する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】

実施形態に係る不揮発性半導体記憶装置は、基板を持つ。基板上方には、絶縁膜及び電極膜が交互に積層された積層体が設けられている。前記積層体を貫き、前記積層体中に弗素を含むシリコンピラーが設けられている。前記シリコンピラーの前記積層体に対向する面上にトンネル絶縁膜が設けられている。前記トンネル絶縁膜の前記積層体に対向する面上には電荷蓄積層が設けられている。前記電荷蓄積層の前記積層体に対向する面上に前記電極膜と接するようにブロック絶縁膜が設けられている。前記シリコンピラー中に埋込部が設けられている。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

不揮発性メモリ及びその製造方法

【課題】

不揮発性メモリ構造を提供する。

【解決手段】

必要に応じて、LDD領域が、アクティブ領域のゲートチャネル領域の保護のためのマスクを用いてイオン注入によって形成され得る。2つのゲートが、互いに離隔され、アクティブ領域の中央領域の2つの側方のそれぞれでアイソレーション構造上に配設される。これら2つのゲートの各々は、その全体がアイソレーション構造上に配置されてもよいし、部分的にアクティブ領域の中央領域の側方部分に重なってもよい。電荷トラップ層及び誘電体層が、格納ノード機能を果たすように、2つのゲートの間且つアクティブ領域上に形成される。これらは更に、スペーサとして機能するように、2つのゲートの全ての側壁上に形成されてもよい。ソース/ドレイン領域が、ゲート及び電荷トラップ層の保護のためのマスクを用いて、イオン注入によって形成される。

(もっと読む)

半導体記憶装置の製造方法

【課題】高集積化を図ることができる半導体記憶装置の製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、基板上に第1膜と第2膜とを交互に積層して第1積層体を形成する工程と、前記第1積層体上に第3膜と第4膜とを交互に積層して第2積層体を形成する工程と、前記第1膜のエッチング速度よりも前記第3膜のエッチング速度の方が低くなる条件でエッチングを施すことにより、前記第2積層体及び前記第1積層体を貫く貫通ホールを形成する工程と、前記貫通ホールの内面上に電荷蓄積膜を形成する工程と、前記貫通ホール内に半導体部材を形成する工程と、を備える。そして、前記第1膜と前記第2膜とを相互に異なる材料によって形成し、前記第3膜と前記第4膜とを相互に異なる材料によって形成し、前記第1膜と前記第3膜とを相互に異なる材料によって形成する。

(もっと読む)

半導体記憶装置

【課題】動作速度が高い半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、一方向に沿って相互に平行に配列された複数枚のゲート電極膜と、前記一方向に延び、前記複数枚のゲート電極膜を貫通する半導体部材と、前記ゲート電極膜と前記半導体部材との間に設けられた電荷蓄積膜と、を備える。前記ゲート電極膜における前記半導体部材に対向した端部には、前記一方向に沿って突出した凸部が設けられており、前記ゲート電極膜間の空間の一部は気体層となっている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コストが低い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、絶縁膜及び電極膜が交互に積層された積層体を形成する工程と、前記積層体上に、サイズが相互に異なる複数のホールが形成されたハードマスクを形成する工程と、マスク材料を堆積させることにより、最も小さい前記ホールを閉塞させると共に、その他の前記ホールを小さくする工程と、前記マスク材料及び前記ハードマスクをマスクとしてエッチングを施すことにより、前記その他のホールの直下域において、各所定枚数の前記絶縁膜及び前記電極膜を除去して、コンタクトホールを形成する工程と、前記コンタクトホールを介してエッチングを施すことにより、前記電極膜の一部分を除去して隙間を形成する工程と、前記隙間内に絶縁材料を埋め込む工程と、前記コンタクトホール内に導電材料を埋め込む工程と、を備える。

(もっと読む)

不揮発性半導体記憶装置の動作方法

【課題】制御部を増加せずにブロックサイズを小さくできる不揮発性半導体記憶装置の動作方法を提供する。

【解決手段】メモリストリングを有するメモリ部と、メモリ部を制御する制御部と、を備える不揮発性半導体記憶装置110の動作方法である。メモリストリングは、直列に接続された複数のトランジスタを含み、複数のトランジスタのうちの一部である第1グループGR1と、第1グループの隣りに接続された第1調整用トランジスタTr−AJと、調整用トランジスタの第1グループとは反対側に接続されたトランジスタを含む第2グループGR2と、を有する。制御部は、第1グループのトランジスタの閾値の書き換えを行ったのち、第1調整用トランジスタに、閾値の書き換えによって生じた第2グループのトランジスタの閾値の相対的な変動分を調整する第1調整用閾値を設定する制御を行う。

(もっと読む)

41 - 60 / 527

[ Back to top ]